Renesas RA Family

# **RA0 Quick Design Guide**

# Introduction

This document answers common questions and points out subtleties of the RA0 MCU that might be missed unless the hardware manual was extensively reviewed. The document is not intended to be a replacement for the hardware manual. It is intended to supplement the manual by highlighting some key items most engineers will need to start their own design. It also discusses some design decisions from an application point of view.

### **Target Device**

**RA0 MCU Series**

### Contents

| 1.    | Power Supplies                                               | 3  |

|-------|--------------------------------------------------------------|----|

| 1.1   | References                                                   | 3  |

| 2.    | Emulator Support                                             | 4  |

| 2.1   | SWD Interface                                                | 4  |

| 3.    | MCU Operating Modes                                          | 5  |

| 4.    | Option-Setting Memory                                        | 6  |

| 4.1   | Option-Setting Memory Registers                              | 7  |

| 5.    | Clock Circuits                                               | 8  |

| 5.1   | Reset Conditions                                             | 9  |

| 5.2   | Clock Frequency Requirements                                 | 9  |

| 5.2.1 | 1 Requirements for Programming and Erasing ROM or Data Flash | 9  |

| 5.3   | Lowering Clock Generation Circuit (CGC) Power Consumption    | 9  |

| 5.4   | Writing the System Clock Control Registers                   | 10 |

| 5.5   | Clock Setup Example                                          | 10 |

| 5.6   | HOCO Accuracy                                                | 11 |

| 5.7   | Flash Interface Clock                                        | 11 |

| 5.8   | Board Design                                                 | 11 |

| 5.9   | External Crystal Resonator Selection                         | 11 |

| 5.10  | External Clock Input                                         | 12 |

| 6.    | Reset Requirements and the Reset Circuit                     | 12 |

| 6.1   | Pin Reset                                                    | 12 |

| 6.2   | Power-On Reset                                               | 13 |

| 6.3   | Independent Watchdog Timer Reset                             | 13 |

| 6.4   | Voltage-Monitoring Resets                                    | 13 |

| 6.5   | Software Reset                                               |    |

| 6.6   | Other Resets                                   | 14 |

|-------|------------------------------------------------|----|

| 6.7   | Determination of Cold/Warm Start               | 14 |

| 6.8   | Determining the Reset Source                   | 14 |

| 7.    | Memory                                         | 15 |

| 7.1   | SRAM                                           | 16 |

| 7.2   | Peripheral I/O Registers                       | 16 |

| 7.3   | On-Chip Flash Memory                           | 16 |

| 7.3.1 | Background Operation                           | 17 |

| 7.3.2 | ID Code Protection                             | 17 |

| 7.4   | Restriction on Endianness                      | 18 |

| 8.    | Register Write Protection                      | 19 |

| 9.    | I/O Port Configuration                         | 19 |

| 9.1   | Multifunction Pin Selection Design Strategies  | 19 |

| 9.2   | Setting Up and Using a Port as GPIO            | 20 |

| 9.2.1 | Internal Pull-Ups                              | 21 |

| 9.2.2 | Open-Drain Output                              | 21 |

| 9.3   | Setting Up and Using Port Peripheral Functions | 21 |

| 9.4   | Setting Up and Using IRQ Pins                  | 22 |

| 9.5   | Unused Pins                                    | 23 |

| 9.6   | Nonexistent Pins                               | 24 |

| 9.7   | Electrical Characteristics                     | 24 |

| 10.   | Module Stop Function                           | 24 |

| 11.   | Interrupt Control Unit                         | 25 |

| 12.   | Low Power Consumption                          | 26 |

| 13.   | Buses                                          | 29 |

| 13.1  | Bus Error Monitoring                           | 29 |

| 13.1. | 1 Bus Error Types                              | 29 |

| 13.1. | 2 Operation When a Bus Error Occurs            | 29 |

| 14.   | General Layout Practices                       | 30 |

| 14.1  | Digital Domain vs. Analog Domain               | 30 |

| 14.2  | High Speed Signal Design Considerations        | 30 |

| 14.3  | Signal Group Selections                        | 31 |

| 15.   | References                                     | 31 |

| Revi  | sion History                                   | 33 |

## 1. Power Supplies

The RA0 family has digital power supplies and analog power supplies. The power supplies use the following pins.

| Table 1. | Digital | Power | Supplies |

|----------|---------|-------|----------|

|----------|---------|-------|----------|

| Symbol | Name         | Description                                                                                                                             |

|--------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| VCC    | Power supply | Power supply pin. Connect to the system power<br>supply. Connect this pin to VSS via a 0.1 µF<br>capacitor placed close to the VCC pin. |

| VSS    | Ground       | Ground.                                                                                                                                 |

| VCL    | Power supply | Connect this pin to VSS via a 0.47 $\mu$ F to 1.0 $\mu$ F capacitor close to the VCL pin.                                               |

### Table 2. Analog Power Supplies

| Symbol | Name                                 | Description                                                                     |

|--------|--------------------------------------|---------------------------------------------------------------------------------|

| VREFH0 | 12-bit ADC high<br>reference voltage | Reference voltage input pin for the 12-bit A/D when not used as GPIO.           |

| VREFL0 | 12-bit ADC low reference voltage     | Analog reference ground pin for the 12-bit A/D converter when not used as GPIO. |

### 1.1 References

Further information regarding the power supply for the RA MCU Group can be found in the following documents:

• R01UH1040 RA0E1 Group, RA0E1 Group User's Manual: Hardware

The **Overview** chapter lists power pins in each package with recommended bypass capacitors.

The **Resets** chapter discusses the Power-On Reset and how to differentiate this from other reset sources.

The **Low Voltage Detection** chapter provides details on the Low-Voltage Detection Circuit that can be used to monitor the power supply. The **Option-Setting Memory** chapter additionally describes how to enable Low-Voltage Detection 0 Circuit automatically at startup.

If you plan to use the on-chip Analog to Digital Converters (ADC), refer to the **12-Bit A/D Converter** (ADC12) chapter in the Hardware User's Manual for details on how to provide filtered power supplies for these peripherals.

| Chapter Name             | Description                                                                                                                                                           |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overview                 | Lists power pins in each package with notes on termination and bypassing.                                                                                             |

| Resets                   | Discusses the Power-On Reset and how to differentiate this from other reset sources.                                                                                  |

| Low Voltage Detection    | Provides details on the Low-Voltage Detection Circuit that can be used to monitor the power supply.                                                                   |

| Low Power Modes          | Using low power modes may allow you to reduce the power consumption of the MCU. See this chapter for details on how operating modes affect power supply requirements. |

| 12-Bit A/D Converter     | If you plan to use the on-chip A/D converter, these chapters give details on how to provide filtered power supplies for these peripherals.                            |

| Clock Generation Circuit | Provides detailed descriptions on how to configure and use the available clocks, including PCB design recommendations.                                                |

### Table 3. RA0 MCU Groups, User's Manual: Hardware

# 2. Emulator Support

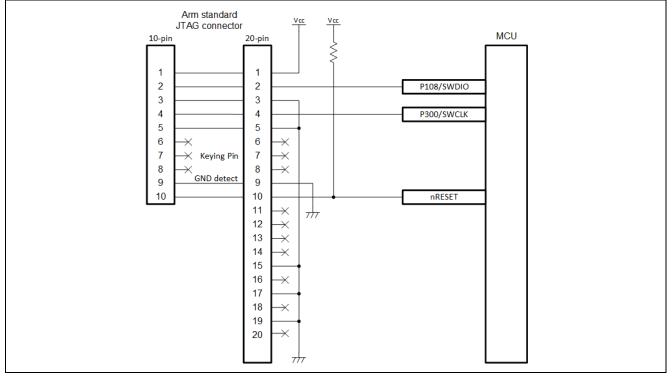

RA0 MCU devices have an emulator interface that supports debugging using SWD communication.

The SWD emulator interface can be connected to an Arm®-standard 10-pin or 20-pin socket.

To comply with the Arm<sup>®</sup> specification, pull up resistors are required on the SWD signals. Without the correct pull up resistors, the interface may not function correctly. However, RA0 MCU devices have internal pull up resistors that are enabled by default for these signals. When the internal pull up resistors are enabled, no external resistors are required on these signals.

Emulator support is useful for product development and prototyping, but may not be needed once a design moves to production. If emulator support is no longer needed for a design, make sure to configure the ports according to the *Handling of Unused Pins* section of the MCU Hardware User's Manual. Also see section 9.5 in this document.

# 2.1 SWD Interface

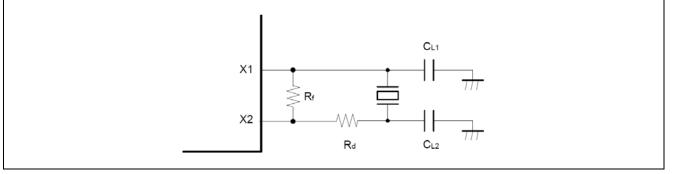

The following diagram shows the typical connectivity of the debug interface when using Serial Wire Debug (SWD).

Figure 1. SWD Interface Connections

Note: The output of the reset circuit of the user system must be open collector.

# 3. MCU Operating Modes

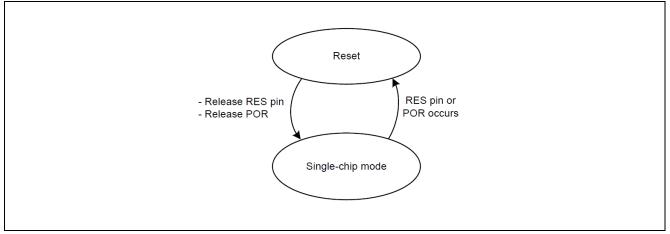

After reset, the RA0 MCU series will enter Single-chip mode. This will occur for both RES pin resets and POR resets.

Figure 2 shows the operating mode transitions.

Figure 2. Operating Mode Transitions

It is important to note that RA0 MCU devices do not have an MD (Mode) pin. This is different from other Renesas RA devices. RA0 MCU devices do not support SCI Boot Mode, so there is no need for the MD pin.

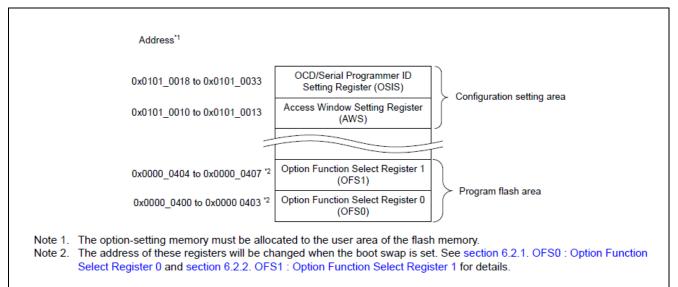

# 4. Option-Setting Memory

The option-setting memory determines the state of the MCU after a reset. It is allocated to the configuration setting area and the program flash area of the flash memory. The available methods for configuration are different for the two areas.

The registers are detailed in the Option-Setting Memory chapter in the Hardware User's Manual.

Options-Setting Memory registers occupy space in the code flash memory map. Although the registers are located in a portion of the flash memory that is reserved on the RA MCUs, **it is possible that some customers may store data in these locations inadvertently**. The user must check to ensure that no unwanted data is written to these locations or else unexpected behavior of the chip may result. Additionally, when using binary files for programming, the user must ensure that reserved areas of memory are not programmed due to the addresses of the configuration setting area. For instance, settings in the option-setting memory can enable the Independent Watchdog Timer (IWDT) immediately after reset. If data stored in program ROM inadvertently overlaps the option-setting memory register, it is possible to turn on the IWDT on without realizing it. This will cause the debugger to have communications problems with the board.

The figure below shows the option-setting memory area, which consists of the option function select registers on RA0E1. The Option-Setting Memory may be different for each device. Please consult MCU User's Manual for the specific device details.

Figure 3. Option-Setting Memory for RA0E1

# 4.1 Option-Setting Memory Registers

The following is a summary of the Option-Setting Memory registers. Make sure that they are configured properly before startup.

- OFS0 register

- Independent Watchdog Timer (IWDT) auto start

- IWDT timeout, frequency, windowing, interrupt type, and low power mode behavior

- OFS1 register

- LVDAS (LVD0 Circuit Start) enable after reset.

- HOCO startup settings after reset.

- Port 206 / RES function selection.

- Flash Read Protection after reset.

Renesas FSP Configurator supports setting of Option Function Select Registers in BSP settings, as shown in Figure 4 for RA0E1 MCU.

| 🎾 FSP Visu | ualization 🔲 Properties 🗙                  |                                                               |

|------------|--------------------------------------------|---------------------------------------------------------------|

| PB-RA      | DE1                                        |                                                               |

| Settings   | Property                                   | Value                                                         |

|            | ✓ R7FA0E1073CFJ                            |                                                               |

|            | part_number                                | R7FA0E1073CFJ                                                 |

|            | rom_size_bytes                             | 65536                                                         |

|            | ram_size_bytes                             | 12288                                                         |

|            | data_flash_size_bytes                      | 1024                                                          |

|            | package_style                              | LQFP                                                          |

|            | package_pins                               | 32                                                            |

|            | ✓ RA0E1                                    |                                                               |

|            | series                                     | 0                                                             |

|            | ✓ RA0E1 Family                             |                                                               |

|            | <ul> <li>OFS0 register settings</li> </ul> |                                                               |

|            | ✓ Independent WDT                          |                                                               |

|            | Start Mode                                 | IWDT is Disabled                                              |

|            | Timeout Period                             | 2048 cycles                                                   |

|            | Dedicated Clock Frequency Divisor          | 128                                                           |

|            | Window End Position                        | 0% (no window end position)                                   |

|            | Window Start Position                      | 100% (no window start position)                               |

|            | Reset Interrupt Request Select             | Reset is enabled                                              |

|            | Stop Control                               | Stop counting when in Sleep, Snooze mode, or Software Standby |

|            | <ul> <li>OFS1 register settings</li> </ul> |                                                               |

|            | Voltage Detection 0 Circuit Start          | Voltage monitor 0 reset is disabled after reset               |

|            | Voltage Detection 0 Level                  | 1.86 V                                                        |

|            | Enable or disable Flash Read Protection    | Disabled                                                      |

|            | Flash Read Protection Start                | 0x01                                                          |

|            | Flash Read Protection End                  | 0x3F                                                          |

|            | P206/RES pin selection                     | RES input                                                     |

|            | Enable inline BSP IRQ functions            | Disabled                                                      |

|            | Main Oscillation Stabilization Time        | 2^18/X1                                                       |

|            | Use Low Voltage Mode                       | Not Supported                                                 |

|            | ID Code Mode                               | Unlocked (Ignore ID)                                          |

|            | ID Code (32 Hex Characters)                | FFFFFFFFFFFFFFFFFFFFFFFF                                      |

|            | Fill Flash Gap                             | Fill gap                                                      |

Figure 4. Option Function Select Register Settings in FSP Configuration for RA0E1 MCU

# 5. Clock Circuits

RA0 MCUs have five primary oscillators. All five of these may be used as the source for the main system clock. In a typical system, the main clock is driven with an external crystal or clock. This input is directed to internal selectors and frequency dividers, where it is further directed to the main system clock (ICLK), flash clock, CPU clock, and peripheral module clocks.

Note: Some RA0 devices may multiplex the Main Clock Oscillator and Sub Clock Oscillator input pins. Refer to the *Clock Generation Circuit* chapter in the *Hardware User's Manual's* for the block diagram of the clock generation circuit.

Each clock has specific tolerances and timing values. Refer to the Hardware User's Manual's AC Characteristics section in the Electrical Characteristics chapter for the Frequency and Clock Timing specifications. Refer to the Hardware User's Manual's Clock Generation Circuit chapter for the relationship between the various clock frequencies.

| Oscillator                      | Input Source               | Frequency       | Primary Uses                                                                                                                                                                                 |

|---------------------------------|----------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main clock                      | External                   | 1 MHz to 20 MHz | System clock (ICLK):                                                                                                                                                                         |

| (MOSC)                          | crystal/resonator          |                 | To CPU, Flash, SRAM, Flash-IF,                                                                                                                                                               |

|                                 | -or-                       |                 | Peripheral module clock                                                                                                                                                                      |

|                                 | External clock             | Up to 20 MHz    |                                                                                                                                                                                              |

| Sub-clock<br>(SOSC)             | External crystal/resonator | 32.768 kHz      | Real-time clock, system clock (ICLK)<br>in low power modes, PCLBUZ0, TAU<br>clock, UARTA clock, TML32 clock.                                                                                 |

| High-speed on-chip<br>(HOCO)    | On-chip oscillator         | 24/32 MHz       | System clock (ICLK) at startup, CPU,<br>Flash, SRAM, Flash-IF, Peripheral<br>module clock.                                                                                                   |

| Middle-speed on-<br>chip (MOCO) | On-chip oscillator         | 1 MHz to 4 MHz  | System clock (ICLK), Peripheral<br>clocks, PCLBUZ0, TAU clock, TML32<br>clock, UARTA clock.                                                                                                  |

| Low-speed on-chip<br>(LOCO)     | On-chip oscillator         | 32.768 kHz      | System clock (ICLK) in low power<br>modes, Peripheral clocks, Systick<br>timer, TAU, TML32 clock, UARTA<br>clock, PCLBUZ0, Real-Time clock,<br>Independent Watchdog Timer clock <sup>1</sup> |

Table 4. RA0 Oscillator Source Specifications

Note 1: The LOCO will oscillate if the IWDT is enabled, regardless of the LOCO register (LOCOCR) settings.

Some RA0 devices may multiplex the Main Clock Oscillator and Sub Clock Oscillator input pins. In this case, users must carefully consider the tolerances of the on-chip oscillators as noted in the Oscillators Characteristics section in the MCU Hardware User's Manual.

# 5.1 Reset Conditions

After reset, RA0 MCUs begin running with the high-speed on-chip oscillator (HOCO) as the main clock source. At reset, the main clock oscillator is stopped by default and the pins are set to port mode. The SOSC, LOCO, MOCO, are stopped by default after reset. The IWDT may be on or off depending on the settings in the Option-Setting Memory (see section 4).

# 5.2 Clock Frequency Requirements

Minimum and maximum frequencies are shown in the following tables. Details can be found in the Overview section of the Clock Generation Circuit chapter in the MCU Hardware User's Manual, including external and internal clock source specifications. Additional details on the tolerances of each clock input source can be found in the Oscillator Characteristics section of the Electrical Characteristics chapter in the MCU Hardware User's Manual.

### Table 5. Frequency Range for RA0 MCU Internal Clocks

|                    |     | RTCCLK | IWDTCLK | SWCLK | CLKOUT | SYSTICCLK |

|--------------------|-----|--------|---------|-------|--------|-----------|

| Max Frequency [Hz] | 32M | 32768  | 16384   | 12.5M | 16M    | 32768     |

| Min Frequency [Hz] |     | 128    | 16384   | —     | —      | 32768     |

Note 1: ICLK must run at a frequency of at least 1 MHz when programming or erasing ROM or data flash.

# 5.2.1 Requirements for Programming and Erasing ROM or Data Flash

For all RA0 devices, the ICLK must be at least 1 MHz to perform programming and erasing on internal ROM and data flash.

# 5.3 Lowering Clock Generation Circuit (CGC) Power Consumption

To aid in saving power, set the dividers for any unused clocks to the highest possible value whenever possible. Also, if not using a clock, then make sure that it has been stopped by setting the appropriate register(s). The registers for controlling each clock source are shown in the table below.

| Oscillator                  | Register | Description                        |

|-----------------------------|----------|------------------------------------|

| Main clock                  | MOSCCR   | Starts/stops main clock oscillator |

| Sub-clock                   | SOSCCR   | Starts/stops sub-clock oscillator  |

| High-speed on-chip (HOCO)   | HOCOCR   | Starts/stops HOCO                  |

| Middle-speed on-chip (MOCO) | MOCOCR   | Starts/stops MOCO                  |

| Low-speed on-chip (LOCO)    | LOCOCR   | Starts/stops LOCO                  |

### Table 6. Clock Source Configuration Registers

After a clock source has been started, a wait period is required to be observed before using it as a source for an internal clock. The status of the wait period can be read and controlled through registers available in the CGC peripheral block such as HOCOSF, and OSTSB.

All internal clocks can be output to the Clock/Buzzer output pins. This allows measuring the clock frequency accurately.

The frequency of all internal on-chip oscillator sources can be trimmed using special function registers HIOTRM, MIOTRM, and LIOTRM. The clock correction resolution of trimming registers, along with other applicable parameters, are specified in the On-chip Oscillators Characteristics sub-section of the Electrical Characteristics.

# 5.4 Writing the System Clock Control Registers

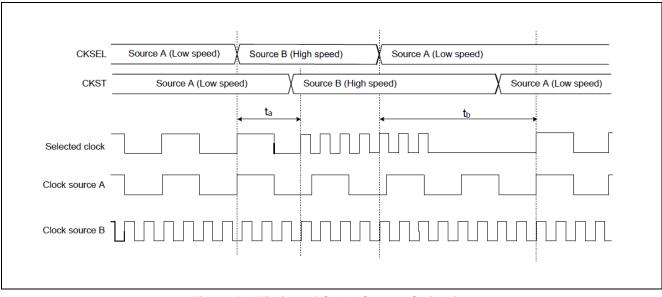

Care should be taken when writing to the individual bit fields in the clock control registers. Follow the register list, ICLK source diagram and timing diagram for clock source switching shown in the section *System Clock* (*ICLK*) in the Hardware User's Manual.

When the clock source of the system clock (ICLK) is switched, the duration of the system clock cycle becomes longer during the clock source transition period. See Figure 5.

To ensure correct processing after the clock frequency changes, first write to the relevant Clock Control registers to change the frequency, then read the value from the register, and finally perform the subsequent processing.

Figure 5. Timing of Clock Source Switching

# 5.5 Clock Setup Example

Renesas FSP provides a simple, visual clock configuration tool for all RA0 MCUs. An example for RA0E1 MCU group is shown below. This configurator configures code in the board support package to initialize the Clock Generation Circuit based on user selection, with proper precautions as indicated in the MCU Hardware User's Manual.

| Clocks Configura |                                                   | Generate Project Conten |

|------------------|---------------------------------------------------|-------------------------|

|                  |                                                   | Restore Defaul          |

| HOCO 32MHz       | HOCO Div /1 V VICLK Src: HOCO V                   |                         |

| MOCO 4MHz        | -> MOCO Div /1 -> TAU CK00 Div /1 -> TAU CK00 32M | 1Hz                     |

| X1 20MHz         | >TAU CK01 Div /1                                  | 1Hz                     |

| SUBCLK 32768Hz   | TAU CK02 Div /2 V TAU CK02 16M                    | 1Hz                     |

| LOCO 32768Hz     | → TAU CK03 Div /256 V → TAU CK03 125              | kHz                     |

|                  | CLKOUT Disabled V CLKOUT Div /1 V CLKOUT 0Hz      |                         |

|                  | VARTA Src: HOCO V VUARTA UTA0 3                   | 2MHz                    |

|                  | TML32 FITL0 Disabled V TML32 FITL0 0              | Hz                      |

|                  | > TML32 FITL1 Disabled V > TML32 FITL1 0          | Hz                      |

|                  | → TML32 FITL2 Disabled v → TML32 FITL2 0          | Hz                      |

|                  | → FSXP Src: SUBCLK →                              | łz                      |

Figure 6. Clock Settings Using Renesas FSP Configurator

# 5.6 HOCO Accuracy

The internal high-speed on-chip oscillator (HOCO) runs at 24 MHz or 32 MHz for RA0 devices. Once the HOCO Clock Oscillation Stabilization Flag (HOCOSF) has been set to 1, the HOCO will have a typical accuracy of +/-1% or better. See the Electrical Characteristics of the *Hardware User's Manual* for the clock accuracy specifications.

The HOCO may be used as an input to the clock generation circuit. When the HOCO is used this way, no external oscillator is required. This may be an advantage when space constraints or other limitations require a reduced component count in a PCB design. However, there are performance tradeoffs and limitations due to the clock accuracy which should be evaluated for your application.

# 5.7 Flash Interface Clock

For RA0 devices, the System Clock (ICLK) is used as the operating clock when programming and erasing the internal flash.

Therefore, the frequency setting of the relevant clock will have a direct impact on the amount of time it takes to read from the data flash. If the user's program is reading from the data flash, or performing programming or erasures on internal flash, then using the maximum ICLK frequency is recommended.

The system clock must run at a frequency of at least 1 MHz when writing or erasing ROM or data flash. Please note that the clock frequency does not have any impact upon reading from ROM or reading and writing to RAM.

# 5.8 Board Design

Refer to the Usage Notes section of the Clock Generation Circuit (CGC) chapter in the Hardware User's Manual for more information on using the CGC and for board design recommendations.

In general, place the crystal resonator and its load capacitors as close to the MCU clock pins (X1/X2, XCIN/XCOUT) as possible. Avoid routing any other signals between the crystal resonator and the MCU. Minimize the number of connecting vias used on each trace.

# 5.9 External Crystal Resonator Selection

An external crystal resonator may be used as the main clock source for most RA0 devices. The external crystal resonator is connected across the EXTAL and XTAL pins of the MCU. The frequency of the external crystal resonator must be in the frequency range of the main clock oscillator.

Selection of a crystal resonator will be largely dependent on each unique board design. Due to the large selection of crystal resonators available that may be suitable for use with RA0 MCU devices, carefully evaluate the electrical characteristics of the selected crystal resonator to determine the specific implementation requirements.

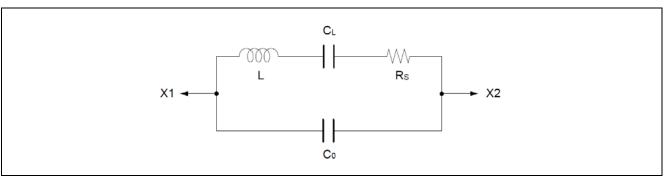

The following diagram shows a typical example of a crystal resonator connection.

Figure 7. Example of Crystal Resonator Connection

Careful evaluation must be used when selecting the crystal resonator and the associated capacitors. The external feedback resistor ( $R_f$ ) and damping resistor ( $R_d$ ) may be added if recommended by the crystal resonator manufacturer.

Selection of the capacitor values for CL1 and CL2 will affect the accuracy of the internal clock. To understand the impact of the values for CL1 and CL2, the circuit should be simulated using the equivalent circuit of the crystal resonator in the figure above. For more accurate results, also take into account the stray capacitance associated with the routing between the crystal resonator components. The Renesas RA Family Design Guide for Sub-Clock Circuits provides details on board design specification for both the external crystal and sub-clock oscillator.

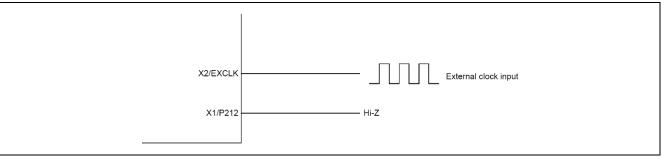

### 5.10 External Clock Input

A digital clock input may be used as the main clock source for most RA0 devices. Figure 9 shows an example of connecting an external clock input. To operate the oscillator with an external clock signal, set the CMC:MOSEL[1:0] bits to 11b. The X1 pin becomes high impedance.

Figure 9. Equivalent circuit for external clock

Note: The frequency of the external clock input can only be changed when the main clock oscillator is stopped. Do not change the frequency of the external clock input when the setting of the Main Clock Oscillator Stop bit (MOSCCR.MOSTP) is 0.

### 6. Reset Requirements and the Reset Circuit

There are 7 types of resets for RA0 Arm<sup>®</sup> Cortex<sup>®</sup>-M23 devices.

### Table 7. RA0 Device Resets

| Reset Name                       | Source                                                         |

|----------------------------------|----------------------------------------------------------------|

| Pin reset                        | RES is driven low                                              |

| Power-on reset                   | VCC rises (voltage detection: VPOR)                            |

| Independent watchdog timer reset | The independent watchdog timer underflows, or a refresh occurs |

| Voltage monitor 0 reset          | VCC falls (voltage detection Vdet0)                            |

| Voltage monitor 1 reset          | VCC falls (voltage detection Vdet1)                            |

| SRAM parity error reset          | SRAM parity error detection                                    |

| Software reset                   | Register setting                                               |

### 6.1 Pin Reset

When the RES pin is driven low, all processing is aborted and the MCU enters a reset state. To reset the MCU while it is running, hold RES low for the specified reset pulse width. Refer to the Reset Timing section of the *Electrical Characteristics* chapter of the *Hardware User's Manual* for more detailed timing

requirements. Also refer to section 2, Emulator Support for details on reset circuitry in relation to debug support.

There is no need to use an external capacitor on the RES line because the POR circuit holds it low internally for a good reset and a minimum reset pulse is required to initiate this process.

Once the power is turned on, P206 functions as the RES input. The PORTSELB bit of the option select register1 (OFS1) defines whether this port operates as P206 or RES. When this pin is set to P206, do not input the low level to this pin during a reset by the power-on-reset (POR) circuit and during the period from release from the reset by the POR circuit to the start of normal operation. If input of the low level continues during this period, the chip will remain in the reset state in response to the external reset. The on-chip pull-up resistor is enabled after power is turned on.

### 6.2 Power-On Reset

There are two conditions that will generate a power-on reset (POR):

- 1. If the RES pin is in a high-level state when power is supplied.

- 2. If the RES pin is in a high-level state when VCC is below VPOR.

After VCC has exceeded the power-on reset voltage (V<sub>POR</sub>) and the power-on reset time (t<sub>POR</sub>) has elapsed, the chip is released from the power-on reset state. The power-on reset time is a period that allows for stabilization of the external power supply and the MCU. Refer to the POR and LVD Characteristics section of the *Electrical Characteristics* chapter of the *Hardware User's Manual* for voltage level and timing details.

Because the POR circuit relies on having RES high concurrently with VCC, don't place a capacitor on the reset pin. This will slow the rise time of RES in relation to VCC, preventing the POR circuit from properly recognizing the power-on condition.

If the RES pin is high when the power supply (VCC) falls to or below  $V_{POR}$ , a power-on reset is generated. The chip is released from the power-on state after VCC has risen above  $V_{POR}$  and the trong has elapsed.

After a power on reset, the PORF bit in PORSR is set to 0. To properly detect a power on reset, this bit must be set to 1 by the user before a power on reset occurs.

### 6.3 Independent Watchdog Timer Reset

This is an internal reset generated by the Independent Watchdog Timer (IWDT).

When the IWDT underflows, an independent watchdog timer reset is optionally generated (NMI can be generated instead) and the IWDTRF bit in RSTSR1 is set to a 1. After a short delay the IWDT reset is canceled. Refer to MCU User's Manual for the specific timing.

### 6.4 Voltage-Monitoring Resets

The RA0 MCU family includes circuitry that allows the MCU to protect against unsafe operation during brownouts. On-board comparators check the supply voltage against two reference voltages, V<sub>det0</sub> and V<sub>det1</sub>. As the supply dips below each reference voltage an interrupt or a reset can be generated. The detection voltage V<sub>det0</sub> is selectable from 6 different levels in the OFS1 register. The detection voltage V<sub>det1</sub> is selectable from 18 different levels in the LVD1CR register.

When VCC subsequently rises above  $V_{det0}$  or  $V_{det1}$ , release from the voltage-monitoring reset proceeds after a stabilization time has elapsed.

Low Voltage Detection is disabled after a power on reset. Voltage monitoring can be enabled by using the Option Function Select register (OFS1) for  $V_{det0}$ , or the LVD1CR register for  $V_{det1}$ . For more details, see the chapter Low Voltage Detection (LVD) in the Hardware User's Manual.

After an LVD Reset, the LVIRF bit in RESF is set to 1.

### 6.5 Software Reset

The software reset is an internal reset generated by a software setting of the SYSRESETREQ bit in the AIRCR register in the Arm core. When the SYSRESETREQ bit is set to 1, a software reset is generated. When the internal reset time (tRESW2) elapses after the software reset is generated, the internal reset is canceled and the CPU starts the reset exception handling. Refer to MCU User's Manual for the specific timing.

For details on the SYSRESETREQ bit, see the Arm<sup>®</sup> Cortex<sup>®</sup>-M23 Technical Reference Manuals.

# 6.6 Other Resets

Peripheral functions within the MCU can generate a reset under specific fault conditions. No hardware configuration is required to enable these resets. Refer to the relevant chapters in the *Hardware User's Manual* for details of the conditions that will generate a reset for each peripheral function.

# 6.7 Determination of Cold/Warm Start

The RA0 MCUs allow the user to determine the cause of the reset processing. The PORSR.PORF register flag indicates whether a power on reset caused the reset processing (cold start) or a reset signal input during operation caused the reset processing (warm start.)

The flag is set to 0 when a power on reset occurs. Otherwise, the flag is not set to 0. The flag is set to 1 when 1 is written to it through software. It is not set to 0 even when 0 is written to it.

# 6.8 Determining the Reset Source

The RA0 MCUs allow the user to determine the reset signal generation source. Read the RESF register to determine which reset was the source of the reset. Refer to the *Hardware User's Manual* table for *Reset detect flags initialized by each reset source* for more information on which flags are modified depending on the source of the interrupt.

The following sample code shows how to determine if a reset is caused by Power On Reset or Software Reset using CMSIS based register structure in Renesas FSP.

```

/* Power on Reset */

if(1 == R_SYSTEM->PORSR_b.PORF)

{

/* Do something */

}

...

/* Software Reset */

if(1 == R_SYSTEM->RESF_b.SWRF)

{

/* Do something */

}

```

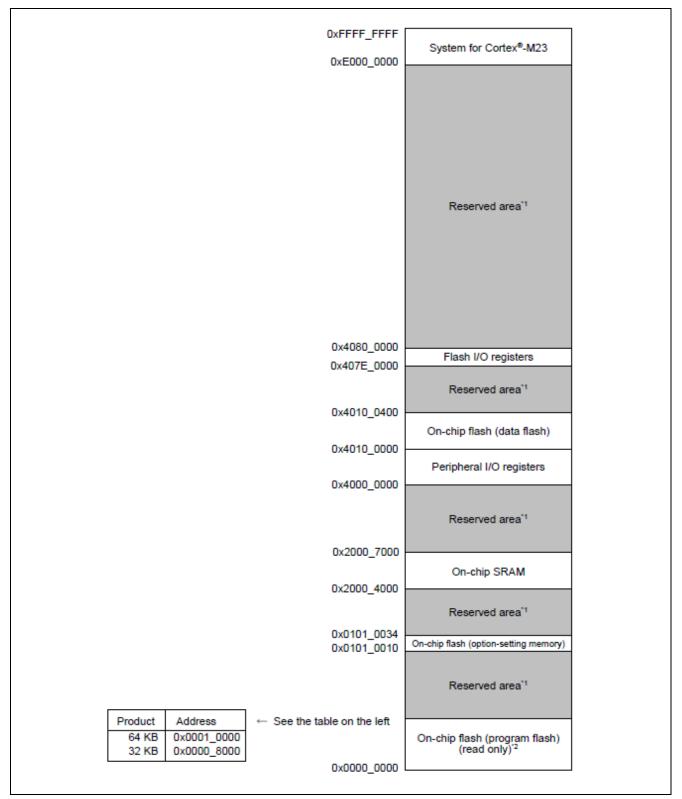

# 7. Memory

The RA0 MCUs support a 4 GB linear address space ranging from 0000 0000h to FFFF FFFFh that can contain program, and data. Program and data memory share the address space. Separate buses are used to access each, increasing performance and allowing same-cycle access of program and data. Contained within the address space are regions for on-chip RAM, peripheral I/O registers, program code flash, and data flash. All reserved areas are off-limits during execution. Undefined behavior may occur if reserved areas are accessed.

Figure 10. RA0E1 Memory Map

# 7.1 SRAM

The RA0 MCUs provide on-chip SRAM modules. The following table lists the SRAM specifications for RA0E1 MCU. The SRAM capacity varies by device. Consult the *Hardware User's Manual* for specifics.

| Table 27.1 SRAM specification | ons                                          |                                   |  |  |  |

|-------------------------------|----------------------------------------------|-----------------------------------|--|--|--|

| Parameter                     | Description                                  |                                   |  |  |  |

| SRAM capacity                 | SRAM0: 12 KB                                 |                                   |  |  |  |

| SRAM address                  | SRAM0: 0x2000_4000 to 0x2000_6FFF            | SRAM0: 0x2000_4000 to 0x2000_6FFF |  |  |  |

| Access <sup>*1</sup>          | 0 wait for both reading and writing          |                                   |  |  |  |

| Parity                        | Even parity with 8-bit data and 1-bit parity |                                   |  |  |  |

| Error checking                | Even parity error check                      | Even parity error check           |  |  |  |

### Figure 11. RA0E1 SRAM Specification

# 7.2 Peripheral I/O Registers

Blocks of peripheral I/O registers appear at various locations in the address space depending on the device and the current operating mode. The majority of peripheral I/O registers occupy a region from address 4000 0000h to 400F FFFFh. However, this may vary in location and size by device. Consult the *Hardware User's Manual* for specifics. Details can be found in the appendix, and also in the register descriptions for each peripheral function. This region contains registers that are available at all times in all modes of operation. Flash I/O registers to control access flash memory occupy the region from 407E 0000h to 407F FFFFh.

The Renesas FSP provide C header files in CMSIS data structure that map all of the peripheral I/O registers for a specific device to easily accessible I/O data structures.

# 7.3 On-Chip Flash Memory

The RA0 MCUs feature two flash memory sections: code flash and data flash, which vary in size and programmable cycle capacity by device. The Flash Control Block (FCBU) controls programming and erasure of flash memory. The Flash Application Command Interface (FACI) controls the FCU in accordance with the specified FACI commands.

The code flash is designed to store user application code and constant data. The data flash is designed to store information that may need frequent updates such as configuration parameters, user settings, or logged data. The units of programming and erasure in the data flash area are smaller than that of the code flash. For example, on RA0E1 devices, the code flash memory uses 32-bit units for programming and 2 KB units for erasure, while the data flash memory uses 8-bit units for programming and 256B units for erasure. The unit sizes vary by device. See the Flash Memory chapter in the *Hardware User's Manual* for details.

Both the data flash and code flash areas can be programmed or erased by application code. This mode is called self-programming. This enables field firmware updates without having to connect an external programming tool. In self-programming, it is necessary to supply a stable HOCO clock to the flash memory to generate the program voltage and erase voltage. Therefore, if the HOCO is stopped where another clock source is selected as the system clock, it is necessary to start the HOCO operation and ensure that the oscillation is in a stable state before executing the self-programming.

Renesas FSP provides HAL layer drivers for both code flash memory and data flash memory.

The following figure shows example specifications of code flash memory and data flash memory.

| Parameter                        | Code flash memory                                                                                                                                                                                                                                                                                                       | Data flash memory                                                                                          |  |  |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Memory capacity                  | <ul> <li>64-KB/32-KB of user area</li> <li>Configuration setting area (See section 6, Option-Setting Memory)</li> </ul>                                                                                                                                                                                                 | 1-KB of data area                                                                                          |  |  |  |  |

| Read cycle                       | A read operation takes 2 cycles                                                                                                                                                                                                                                                                                         | A read operation takes 6 cycles                                                                            |  |  |  |  |

| Value after erasure              | 0xFF                                                                                                                                                                                                                                                                                                                    | 0xFF                                                                                                       |  |  |  |  |

| Programming/erasing method       | <ul> <li>Programming and erasure of code and d<br/>specified in the registers</li> <li>Programming of flash memory by user pr</li> </ul>                                                                                                                                                                                | ata flash memory through the FCB commands                                                                  |  |  |  |  |

| Security function                | ty function Protection against illicit tampering with or reading of data in flash memory                                                                                                                                                                                                                                |                                                                                                            |  |  |  |  |

| Protection                       | Protection against erroneous overwriting of flash memory                                                                                                                                                                                                                                                                |                                                                                                            |  |  |  |  |

| Background operation (BGO)       | Code flash memory can be read during data flash memory programming                                                                                                                                                                                                                                                      |                                                                                                            |  |  |  |  |

| Units of programming and erasure | <ul> <li>32-bit units for programming in user area</li> <li>2-KB units for erasure in user area.</li> </ul>                                                                                                                                                                                                             | <ul> <li>8-bit units for programming in data area</li> <li>256B units for erasure in data area.</li> </ul> |  |  |  |  |

| Other functions                  | Interrupts accepted during self-programming                                                                                                                                                                                                                                                                             |                                                                                                            |  |  |  |  |

|                                  | Option-setting memory can be set in the initial MCU settings                                                                                                                                                                                                                                                            |                                                                                                            |  |  |  |  |

| On-board programming             | <ul> <li>Programming in on-chip debug mode:</li> <li>SWD interface used</li> <li>Dedicated hardware not required.</li> <li>Programming by a routine for code and data flash memory programming within the user program:</li> <li>Allows code and data flash memory programming without resetting the system.</li> </ul> |                                                                                                            |  |  |  |  |

| Table 28.1 | Code flash memory | / and data flash | memory specifications |

|------------|-------------------|------------------|-----------------------|

|------------|-------------------|------------------|-----------------------|

Figure 12. Specifications of Code Flash Memory and Data Flash Memory on RA0E1 MCU

### 7.3.1 Background Operation

RA0 MCUs support background operations (BGO) for data flash. This means that when a program or erase starts, the user can keep executing and accessing memory from memory areas other than the one being operated on. For example, the CPU can execute application code from code flash while the data flash memory is being erased or programmed.

### 7.3.2 ID Code Protection

RA0 MCUs have a 128-bit memory in option-setting memory area that is used as an ID code. If this ID code is left blank (0xFF's) then no protection is enabled and access to the MCU is allowed using the on-chip debugger. If the ID code is set, then the user can control access to these modes. The user can choose to always disallow connections or can choose to allow connections when a matching ID code is input. Refer to the OCD/Serial Programmer ID Setting Register (OSIS) and ID Code Protection and sections of RA0 MCU Hardware User's Manual for more information.

Renesas FSP configurator provides options to set up ID code protection for RA0 MCUs as shown in Figure 13.

| PB-RAC  | DE1                                 |                                         |

|---------|-------------------------------------|-----------------------------------------|

| ettings | Property                            | Value                                   |

|         | ✓ R7FA0E1073CFJ                     |                                         |

|         | part_number                         | R7FA0E1073CFJ                           |

|         | rom_size_bytes                      | 65536                                   |

|         | ram_size_bytes                      | 12288                                   |

|         | data_flash_size_bytes               | 1024                                    |

|         | package_style                       | LQFP                                    |

|         | package_pins                        | 32                                      |

|         | ✓ RA0E1                             |                                         |

|         | series                              | 0                                       |

|         | ✓ RA0E1 Family                      |                                         |

|         | > OFS0 register settings            |                                         |

|         | > OFS1 register settings            |                                         |

|         | Enable inline BSP IRQ functions     | Disabled                                |

|         | Main Oscillation Stabilization Time | 2^18/X1                                 |

|         | Use Low Voltage Mode                | Not Supported                           |

|         | ID Code Mode                        | Unlocked (Ignore ID)                    |

|         | ID Code (32 Hex Characters)         | FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF |

|         | Fill Flash Gap                      | Fill gap                                |

### Figure 13. ID Code Setup for RA0E1 Using Renesas FSP Configurator

Note: ID code protection settings must be handled carefully to prevent mistakes that may result in blocking access to the MCU.

### 7.4 Restriction on Endianness

Memory space must be little-endian to execute code on the Arm<sup>®</sup> Cortex<sup>®</sup>-M core.

#### **Register Write Protection** 8.

The register write protection function protects important registers from being overwritten because of software errors. The registers to be protected are set with the Protect Register (PRCR). Table 8 lists the association between the PRCR bits and the registers to be protected.

| b15 | b14                     | b13 | b12  | b11    | b10 | b9 | b8 | b7 | b6 | b5 | b4 | b3   | b2 | b1   | b0   |

|-----|-------------------------|-----|------|--------|-----|----|----|----|----|----|----|------|----|------|------|

|     |                         |     | PRKE | Y[7:0] |     |    |    |    |    |    |    | PRC3 |    | PRC1 | PRC0 |

|     | Figure 14 BBCB Begister |     |      |        |     |    |    |    |    |    |    |      |    |      |      |

Figure 14. PRCR Register

| PRCR bit   | Description                                                                                                                                                                                                                       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PRC0       | <ul> <li>Registers related to the Clock Generation Circuit:<br/>CMC, SOMRG, FOCOSCR, FMAINSCR, FSUBSCR, ICLKSCR, MOSCCR,<br/>SOSCCR, LOCOCR, HOCOCR, MOCOCR, OSTS, HOCODIV, MOCODIV,<br/>MOSCDIV, OSMC, LIOTRM, MIOTRM</li> </ul> |

| PRC1       | <ul><li>Registers related to the low power modes:</li><li>SBYCR, PSMCR, SYOCDCR</li></ul>                                                                                                                                         |

| PRC3       | Registers related to the LVD:<br>LVD1CR, LVD1MKR, LVD1SR                                                                                                                                                                          |

| PRKEY[7:0] | These bits control write access to the PRCR register. To modify the PRCR register, write A5h to the eight higher-order bits and the wanted value to the eight lower-order bits as a 16-bit unit.                                  |

### Table 8. PRCR Protection Bits

Note: Not all registers may be included on all RA0 devices. Please refer to the Register Write Protection section of the Hardware User's Manual for more details.

Renesas FSP supplies two APIs (R\_BSP\_RegisterProtectEnable and

R\_BSP\_RegisterProtectDisable) to enable and disable Register Write Protection respectively.

### 9. I/O Port Configuration

The I/O Ports section of the Hardware User's Manual describes exact pin configurations based on peripheral selection and other register settings. Some general information is listed as follows.

It is important to note that after a reset, each pin will be in the default state for that pin until the configuration is applied. For RA0 devices, all I/O pins operate as input pins immediately after a reset. There may be a small period where some pins may be in an undesirable state. This will be true regardless of what configuration approach is used. The user should consider the impact this may have for each application. including how this may affect other system features.

The IO Port Configuration may be set by either directly writing to registers or using the FSP Pin Configurator.

#### Multifunction Pin Selection Design Strategies 9.1

Most ports on the RA0 Series of MCUs can have multiple peripheral functions. Tools, such as the Pin Configurator in FSP, are available from Renesas to assist with port selection for each RA0 device. When several peripheral functions are needed, use the following design strategies to help with port function selection.

- Assign peripheral functions with only one port option first. For example, there is only one port option for each debug signal in the debug function. When this function is needed, assign these ports first.

- Assign peripheral functions with limited port options next. For example, the CLKOUT function only has three options for the CLKOUT signal on RA0E1.

- Assign peripheral functions with multiple port options last. One example would be the Serial Array Unit (SAU) which typically has several available port options.

- The Pin Lists section in the RA0 Hardware User's Manuals show some peripheral port functions with a suffix (such as "\_A") at the end of the function name. For RA0 devices, this type of suffix can be ignored when assigning port functions for most peripheral. Please see the I/O Ports section, Peripheral Select

Settings for Each Product in the RA0 *Hardware User's Manual* for details. Also see section 9.3 in this document.

# 9.2 Setting Up and Using a Port as GPIO

There are two methods for setting up and using a port as GPIO, either using the Port Control Registers (PODRm, PDRm, PIDRm, POSRm, EORRm, EOSRm), or the PmnPFS registers.

### Method 1: Port Control Registers

- Select a pin as an output by writing a 1 to the appropriate bit of the Port Direction Register (PDRm).

- The Port Direction bits (PDRn) are read/write. Setting the value to a 1 selects the pin as an output. Default state for I/O Ports is 0 (input). The port direction registers can be read on the RA0 MCUs.

- The Port Output Data bits (PODRn) in the corresponding Port Output Data Register (PODRm) are read/write. When the PODR is read the state of the output data latch (not the pin level) is read.

- The Port Input bits (PIDRn) in Port State Register (PIDRm) are read only. Read the PIDRn bit in the PIDRm register to read the pin state.

### Method 2: Port mn Pin Function Select (PmnPFS) Registers

- The Port Mode Registers are read/write. They are used to specify whether individual pins function as GPIO or as peripheral pins.

- When setting a pin as an output, it is recommended that the desired output value of the port be written to the data latch first, then the direction register should be set to an output. Though not important in all systems, this prevents an unintended output glitch when the port is set up.

In general, using the Port Control Registers to configure a port will provide faster access but will have fewer configuration features available. Using the PmnPFS registers will have more configuration features available but will have slower access.

Renesas FSP provides a Pin Configurator to configure the GPIO pin after reset as shown in Figure 15. Configuring P008 as Output and Low using FSP Configurator. After the GPIO is configured, it can be controlled using HAL layer APIs in FSP.

| Symbolic Name LED1<br>Comment GREEN_ARDUINO_A4 |     |

|------------------------------------------------|-----|

| Comment GREEN ARDUINO A4                       |     |

| Mode Output mode (Initial Low                  | 0   |

| Output Type CMOS                               | /   |

| Input/Output                                   |     |

| Poos                                           | (c) |

Figure 15. Configuring P008 as Output and Low using FSP Configurator

# 9.2.1 Internal Pull-Ups

- Most port pins can enable a pull-up resistor. The pull-up is controlled by the Pull-Up bit (PCR) bit in each Port mn Pin Function Select (PmnPFS) register. The PCR bit in each PmnPFS register controls the corresponding pin on the port.

- The pin must first be set as an input with the associated bit in the PmnPFS register. Set the PCR bit to 1 to enable the pull-up and to 0 to disable it.

- Out of reset most PCR registers are cleared to 0, therefore the pull-up resistors are disabled. See the *Hardware User's Manual* for exceptions.

- The pull-up is automatically turned off whenever a pin is designated as an external bus pin, a GPIO output, or a peripheral function output pin.

# 9.2.2 Open-Drain Output

- Pins configured as outputs normally operate as CMOS outputs.

- Most pins on ports 0 through 9 can be configured as an NMOS open-drain output.

- The N-channel open-drain control (NCODR) bit in each Port mn Pin Function Select (PmnPFS) Register controls which pins operate in open-drain mode. Setting the applicable bit in each register to a 1 makes the output open-drain. Setting the applicable bit in each register to a 0 sets the port to CMOS output.

# 9.3 Setting Up and Using Port Peripheral Functions

The Port mn Pin Function Select Registers (PmnPFS) are used to configure the characteristics of each port. The PSEL bits select the peripheral function selected for each port.

- Since most pins have multiple functions, the RA0 MCUs have Pin Function Control Registers (PmnPFS) that allow you to change the function assigned to a pin.

- Each pin has its own PmnPFS register.

- Each PmnPFS register allows a pin to be used for peripheral function (PSEL bits), as an IRQ input pin (ISEL bit), or as an analog input pin (PMC bit). To use a pin as an analog function, set the Pin Mode Control bit (PMC) to 1, the N-Channel Open-Drain Control bit (NCODR) to 0, and the Port Direction bit (PDR) to 0 in the Port mn Pin Function Select Register PmnPFS\_A.

- Refer to the Peripheral Select Settings for each Product section in the I/O Ports chapter of the Hardware User's Manual.

- All PmnPFS registers are write protected out of reset. In order to write to these registers, first enable writing using the Write-Protect Register (PWPR).

- Care should be taken when setting PmnPFS registers so that a single function is not assigned to multiple pins. The user should not do this but the MCU will allow it. If this occurs the function on the pins will be undefined.

Figure 16 shows an example of enabling SAU\_SPI1 pins using FSP Pin configuration.

| Name                                          | Value                    | Lock                                  | Link              |   |

|-----------------------------------------------|--------------------------|---------------------------------------|-------------------|---|

| Pin Group Selection                           | Mixed                    |                                       |                   |   |

| Operation Mode                                | Simple SPI               |                                       |                   |   |

| ✓ Input/Output                                |                          |                                       | $\langle \rangle$ |   |

| SCK11                                         | ✓ P407                   | <b>_</b>                              | $\Rightarrow$     |   |

| SI11                                          | ✓ P212                   | E C                                   | $\Rightarrow$     |   |

| SO11                                          | ✓ P213                   | i i i i i i i i i i i i i i i i i i i | $\Rightarrow$     |   |

| <                                             |                          |                                       |                   | > |

| Module name: SAU_SPI11<br>Usage: For SPI, sai | me Pin Group recommended |                                       |                   |   |

### Figure 16. Enabling SPI0 pins Using Pin Configurator in Renesas FSP

### 9.4 Setting Up and Using IRQ Pins

- Certain port pins can be used as hardware interrupt lines (IRQ). See the Peripheral Select Settings for each Product section in the I/O Ports chapter of the Hardware User's Manual for information on which pins are available for your MCU.

- To set a port pin to be used as an IRQ pin, the Interrupt Input Function Select bit (ISEL) in the pin's PFS register must be set to 1.

- Pins can be used for both IRQ and peripheral functions simultaneously. To enable this, set both the ISEL and PSEL bits in the pin's PFS register.

- IRQ functions of the same number must only be enabled on one pin.

- IRQ pins can trigger interrupts on detection of:

- Falling edge

- Rising edge

- Rising and falling edges

The IRQ Control Registers (IRQCRi) controls which trigger is selected.

Figure 17 and Figure 18 show examples of enabling and configuring IRQ pins using Renesas FSP.

| Name                | Value  | Lock | Link          |  |

|---------------------|--------|------|---------------|--|

| Pin Group Selection | Mixed  |      |               |  |

| Operation Mode      | Custom |      |               |  |

| ✓ Input/Output      |        |      |               |  |

| IRQ0                | ✓ P200 |      | $\Rightarrow$ |  |

| IRQ1                | ✓ P015 |      | $\Rightarrow$ |  |

| IRQ2                | None   |      | $\Rightarrow$ |  |

| IRQ3                | None   |      | $\Rightarrow$ |  |

| IRQ4                | None   |      | $\rightarrow$ |  |

| IRQ5                | None   |      | $\Rightarrow$ |  |

| <                   |        |      |               |  |

| Module name: IRQ    |        |      |               |  |

Figure 17. Enable P200 and P015 as IRQ0 and IRQ1 Input Using Pin Configurator in Renesas FSP

| Stacks Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Generate Project Content                                     | g_extern             | al_irq0 External IRQ (r_icu)                                                                                                                                                                       |                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| Threads     New Thread     Remove       Image: HAL/Common     Image: Grade and G | Generate Project Content<br>g_external IRQ<br>(r_icu) Stacks | Settings<br>API Info | Property  Common Parameter Checking  Channel Trigger Digital Filtering Digital Filtering Channel Channel Trigger Digital Filtering Digital Filtering Digital Filtering Pin Interrupt Priority Pins | Value<br>Default (BSP)<br>g_external_irq0<br>0<br>Rising<br>Not Supported<br>callback_irq0<br>Priority 2 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                              |                      | V Pins<br>IRQ0                                                                                                                                                                                     | P200                                                                                                     |

Figure 18. Configure IRQ0 Using Renesas FSP Configurator

### 9.5 Unused Pins

Note: Some pins require specific termination: See the *Handling of Unused Pins* section of the *Hardware User's Manual* for specific recommendations.

Unused pins that are left floating can consume extra power and leave the system more susceptible to noise problems. Terminate unused pins with one of the methods detailed here:

- The first option is to set the pin to an input (the default state after reset) and connect the pin to VCC or VSS using a resistor. There is no difference to the MCU between one connection or another; however, there may be an advantage from a system noise perspective. VSS is probably the most typical choice. Avoid connecting a pin directly to VCC or VSS since an accidental write to the port's direction register that sets the pin to an output could create a shorted output.

- 2. A second method is to set the pin to an output. The pin level may be set high or low. However, setting the pin as an output and making the output low connects the pin internally to the ground plane. This may help with overall system noise concerns. A disadvantage of setting unused pins to outputs is that the configuration of the port must be done via software control. While the MCU is held in reset and until the direction register is set for output, the pin will be a floating input and may draw extra current. If the extra current can be tolerated during this time, this method eliminates the external resistors required in the first method.

- 3. A variation on leaving the pins as inputs and terminating them with external resistors uses the internal pull-ups available on many ports of the MCU. This has the same limitation as setting the pins to outputs

(requires the program to set up the port) but it does limit the effect of accidental pin shorts to ground, adjacent pins or VCC since the device will not be driving the pin.

# 9.6 Nonexistent Pins

Each RA0 MCU group is available in multiple package sizes, with different total pin counts. For any package smaller than the largest package for that MCU group (typically 24 pins, 20 pins, or 16 pins), set the corresponding bits of nonexistent ports in the PDR register to 0 and in the PODR register to 0. The user can see which ports are available on each MCU package by reviewing the Specifications of I/O Ports table in the I/O Ports section of the Hardware User's Manual. Note that no additional handling of nonexistent pins is required.

# 9.7 Electrical Characteristics

Normal GPIO ports typically require CMOS level inputs (High  $\ge$  0.8 \* VCC, Low  $\le$  0.2 \* VCC). Some GPIO ports have Schmitt Trigger inputs, which have slightly different input requirements. See the *Hardware User's Manual* section *Electrical Characteristics* for more information.

# **10. Module Stop Function**

To maximize power efficiency, the RA0 series of MCUs allow on-chip peripherals to be stopped individually by writing to the Module Stop Control Registers (MSTPCRi, i=A, B, C, D). Once a module stops, access to the module registers is not possible.

After a reset, most of the modules are placed in module-stop state, except for DTC. See *Hardware User's Manual* for details.

Before accessing any of the registers for a peripheral, the peripheral must be enabled by taking it out of stop mode by writing a 0 to the corresponding bit in the MSTPCRi register.

Peripherals may be stopped by writing a 1 to the proper bit in the MSTPCRi register.

HAL drivers in Renesas FSP handle module start/stop function automatically.

# **11. Interrupt Control Unit**