# **RL78/G1C**

ユーザーズマニュアル ハードウェア編

16 ビット・シングルチップ・マイクロコントローラ

本資料に記載の全ての情報は本資料発行時点のものであり、ルネサス エレクトロニクスは、 予告なしに、本資料に記載した製品または仕様を変更することがあります。 ルネサス エレクトロニクスのホームページなどにより公開される最新情報をご確認ください。

## ご注意書き

- 1. 本資料に記載された回路、ソフトウェアおよびこれらに関連する情報は、半導体製品の動作例、応用例を説明するものです。回路、ソフトウェアおよびこれらに関連する情報を使用する場合、お客様の責任において、お客様の機器・システムを設計ください。これらの使用に起因して生じた損害(お客様または第三者いずれに生じた損害も含みます。以下同じです。)に関し、当社は、一切その責任を負いません。

- 2. 当社製品または本資料に記載された製品データ、図、表、プログラム、アルゴリズム、応用回路例等の情報の使用に起因して発生した第三者の特許権、 著作権その他の知的財産権に対する侵害またはこれらに関する紛争について、当社は、何らの保証を行うものではなく、また責任を負うものではあり ません。

- 3. 当社は、本資料に基づき当社または第三者の特許権、著作権その他の知的財産権を何ら許諾するものではありません。

- 4. 当社製品を組み込んだ製品の輸出入、製造、販売、利用、配布その他の行為を行うにあたり、第三者保有の技術の利用に関するライセンスが必要となる場合、当該ライセンス取得の判断および取得はお客様の責任において行ってください。

- 5. 当社製品を、全部または一部を問わず、改造、改変、複製、リバースエンジニアリング、その他、不適切に使用しないでください。かかる改造、改変、 複製、リバースエンジニアリング等により生じた損害に関し、当社は、一切その責任を負いません。

- 6. 当社は、当社製品の品質水準を「標準水準」および「高品質水準」に分類しており、各品質水準は、以下に示す用途に製品が使用されることを意図しております。

標準水準: コンピュータ、OA 機器、通信機器、計測機器、AV 機器、家電、工作機械、パーソナル機器、産業用ロボット等

高品質水準:輸送機器(自動車、電車、船舶等)、交通制御(信号)、大規模通信機器、金融端末基幹システム、各種安全制御装置等

当社製品は、データシート等により高信頼性、Harsh environment 向け製品と定義しているものを除き、直接生命・身体に危害を及ぼす可能性のある機器・システム(生命維持装置、人体に埋め込み使用するもの等)、もしくは多大な物的損害を発生させるおそれのある機器・システム(宇宙機器と、海底中継器、原子力制御システム、航空機制御システム、プラント基幹システム、軍事機器等)に使用されることを意図しておらず、これらの用途に使用することは想定していません。たとえ、当社が想定していない用途に当社製品を使用したことにより損害が生じても、当社は一切その責任を負いません。

- 7. あらゆる半導体製品は、外部攻撃からの安全性を 100%保証されているわけではありません。当社ハードウェア/ソフトウェア製品にはセキュリティ 対策が組み込まれているものもありますが、これによって、当社は、セキュリティ脆弱性または侵害(当社製品または当社製品が使用されているシステムに対する不正アクセス・不正使用を含みますが、これに限りません。)から生じる責任を負うものではありません。当社は、当社製品または当社製品が使用されたあらゆるシステムが、不正な改変、攻撃、ウイルス、干渉、ハッキング、データの破壊または窃盗その他の不正な侵入行為(「脆弱性問題」といいます。)によって影響を受けないことを保証しません。当社は、脆弱性問題に起因しまたはこれに関連して生じた損害について、一切責任を負いません。また、法令において認められる限りにおいて、本資料および当社ハードウェア/ソフトウェア製品について、商品性および特定目的との合致に関する保証ならびに第三者の権利を侵害しないことの保証を含め、明示または黙示のいかなる保証も行いません。

- 8. 当社製品をご使用の際は、最新の製品情報(データシート、ユーザーズマニュアル、アプリケーションノート、信頼性ハンドブックに記載の「半導体デバイスの使用上の一般的な注意事項」等)をご確認の上、当社が指定する最大定格、動作電源電圧範囲、放熱特性、実装条件その他指定条件の範囲内でご使用ください。指定条件の範囲を超えて当社製品をご使用された場合の故障、誤動作の不具合および事故につきましては、当社は、一切その責任を負いません。

- 9. 当社は、当社製品の品質および信頼性の向上に努めていますが、半導体製品はある確率で故障が発生したり、使用条件によっては誤動作したりする場合があります。また、当社製品は、データシート等において高信頼性、Harsh environment 向け製品と定義しているものを除き、耐放射線設計を行っておりません。仮に当社製品の故障または誤動作が生じた場合であっても、人身事故、火災事故その他社会的損害等を生じさせないよう、お客様の責任において、冗長設計、延焼対策設計、誤動作防止設計等の安全設計およびエージング処理等、お客様の機器・システムとしての出荷保証を行ってください。特に、マイコンソフトウェアは、単独での検証は困難なため、お客様の機器・システムとしての安全検証をお客様の責任で行ってください。

- 10. 当社製品の環境適合性等の詳細につきましては、製品個別に必ず当社営業窓口までお問合せください。ご使用に際しては、特定の物質の含有・使用を規制する RoHS 指令等、適用される環境関連法令を十分調査のうえ、かかる法令に適合するようご使用ください。かかる法令を遵守しないことにより生じた損害に関して、当社は、一切その責任を負いません。

- 11. 当社製品および技術を国内外の法令および規則により製造・使用・販売を禁止されている機器・システムに使用することはできません。当社製品および技術を輸出、販売または移転等する場合は、「外国為替及び外国貿易法」その他日本国および適用される外国の輸出管理関連法規を遵守し、それらの定めるところに従い必要な手続きを行ってください。

- 12. お客様が当社製品を第三者に転売等される場合には、事前に当該第三者に対して、本ご注意書き記載の諸条件を通知する責任を負うものといたします。

- 13. 本資料の全部または一部を当社の文書による事前の承諾を得ることなく転載または複製することを禁じます。

- 14. 本資料に記載されている内容または当社製品についてご不明な点がございましたら、当社の営業担当者までお問合せください。

- 注 1. 本資料において使用されている「当社」とは、ルネサス エレクトロニクス株式会社およびルネサス エレクトロニクス株式会社が直接的、間接的に 支配する会社をいいます。

- 注 2. 本資料において使用されている「当社製品」とは、注1において定義された当社の開発、製造製品をいいます。

(Rev.5.0-1 2020.10)

## 本社所在地

〒 135-0061 東京都江東区豊洲 3-2-24 (豊洲フォレシア)

www.renesas.com

## 商標について

ルネサスおよびルネサスロゴはルネサス エレクトロニクス株式会社の 商標です。すべての商標および登録商標は、それぞれの所有者に帰属し ます。

## お問合せ窓口

弊社の製品や技術、ドキュメントの最新情報、最寄の営業お問合せ窓口 に関する情報などは、弊社ウェブサイトをご覧ください。

www.renesas.com/contact/

## 製品ご使用上の注意事項

ここでは、マイコン製品全体に適用する「使用上の注意事項」について説明します。個別の使用上の注意事項については、本ドキュメントおよびテクニカルアップデートを参照してください。

#### 1. 静電気対策

CMOS 製品の取り扱いの際は静電気防止を心がけてください。CMOS 製品は強い静電気によってゲート絶縁破壊を生じることがあります。運搬や保存の際には、当社が出荷梱包に使用している導電性のトレーやマガジンケース、導電性の緩衝材、金属ケースなどを利用し、組み立て工程にはアースを施してください。プラスチック板上に放置したり、端子を触ったりしないでください。また、CMOS 製品を実装したボードについても同様の扱いをしてください。

#### 2. 電源投入時の処置

電源投入時は、製品の状態は不定です。電源投入時には、LSIの内部回路の状態は不確定であり、レジスタの設定や各端子の状態は不定です。外部リセット端子でリセットする製品の場合、電源投入からリセットが有効になるまでの期間、端子の状態は保証できません。同様に、内蔵パワーオンリセット機能を使用してリセットする製品の場合、電源投入からリセットのかかる一定電圧に達するまでの期間、端子の状態は保証できません。

#### 3. 電源オフ時における入力信号

当該製品の電源がオフ状態のときに、入力信号や入出力プルアップ電源を入れないでください。入力信号や入出力プルアップ電源からの電流注入により、誤動作を引き起こしたり、異常電流が流れ内部素子を劣化させたりする場合があります。資料中に「電源オフ時における入力信号」についての記載のある製品は、その内容を守ってください。

#### 4. 未使用端子の処理

未使用端子は、「未使用端子の処理」に従って処理してください。CMOS製品の入力端子のインピーダンスは、一般に、ハイインピーダンスとなっています。未使用端子を開放状態で動作させると、誘導現象により、LSI周辺のノイズが印加され、LSI内部で貫通電流が流れたり、入力信号と認識されて誤動作を起こす恐れがあります。

#### 5. クロックについて

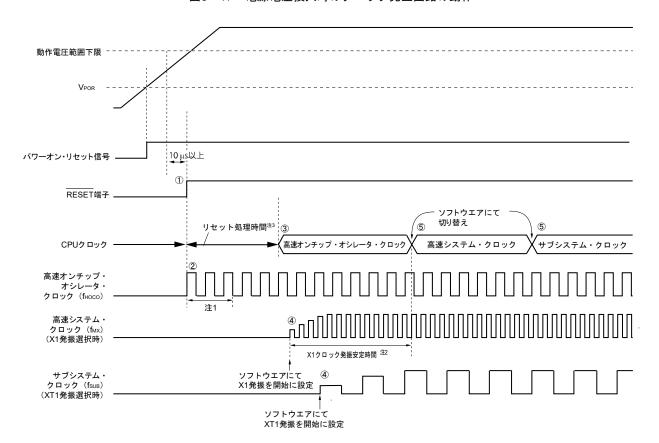

リセット時は、クロックが安定した後、リセットを解除してください。プログラム実行中のクロック切り替え時は、切り替え先クロックが安定した後に切り替えてください。リセット時、外部発振子(または外部発振回路)を用いたクロックで動作を開始するシステムでは、クロックが十分安定した後、リセットを解除してください。また、プログラムの途中で外部発振子(または外部発振回路)を用いたクロックに切り替える場合は、切り替え先のクロックが十分安定してから切り替えてください。

#### 6. 入力端子の印加波形

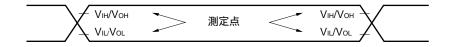

入力ノイズや反射波による波形歪みは誤動作の原因になりますので注意してください。CMOS 製品の入力がノイズなどに起因して、 $V_{\rm IL}$  (Max.) から  $V_{\rm IH}$  (Min.) までの領域にとどまるような場合は、誤動作を引き起こす恐れがあります。入力レベルが固定の場合はもちろん、 $V_{\rm IL}$  (Max.) から  $V_{\rm IH}$  (Min.) までの領域を通過する遷移期間中にチャタリングノイズなどが入らないように使用してください。

#### 7. リザーブアドレス (予約領域) のアクセス禁止

リザーブアドレス (予約領域) のアクセスを禁止します。アドレス領域には、将来の拡張機能用に割り付けられている リザーブアドレス (予約領域) があります。これらのアドレスをアクセスしたときの動作については、保証できませんので、アクセスしないようにしてください。

#### 8. 製品間の相違について

型名の異なる製品に変更する場合は、製品型名ごとにシステム評価試験を実施してください。同じグループのマイコンでも型名が違うと、フラッシュメモリ、レイアウトパターンの相違などにより、電気的特性の範囲で、特性値、動作マージン、ノイズ耐量、ノイズ幅射量などが異なる場合があります。型名が違う製品に変更する場合は、個々の製品ごとにシステム評価試験を実施してください。

# このマニュアルの使い方

対 象 者 このマニュアルはRL78/G1Cの機能を理解し、その応用システムや応用プログラムを設計、開発するユ ーザのエンジニアを対象としています。

対象製品は、次に示す各製品です。

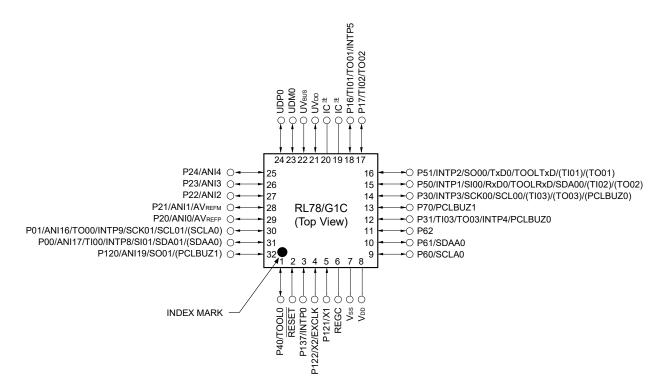

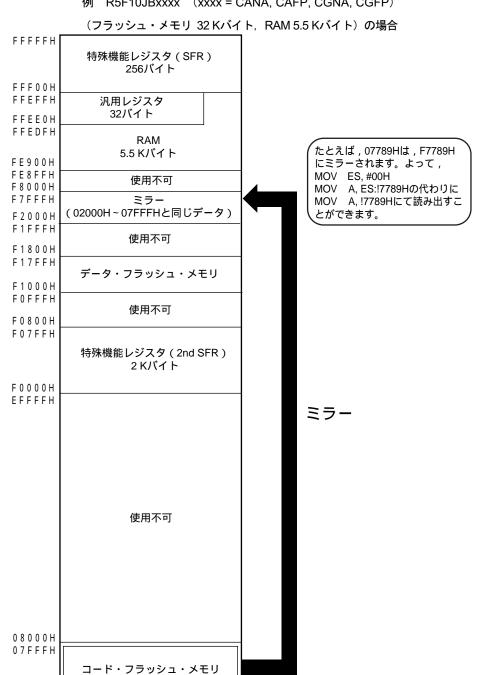

・32ピン: R5F10JBxxxx (xxxx =, CANA, CAFP, CGNA, CGFP)

R5F10KBxxxx (xxxx =, CANA, CAFP, CGNA, CGFP)

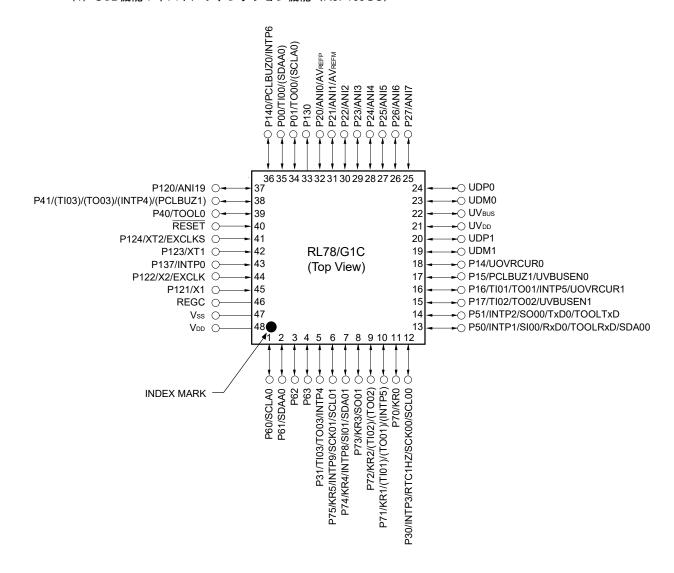

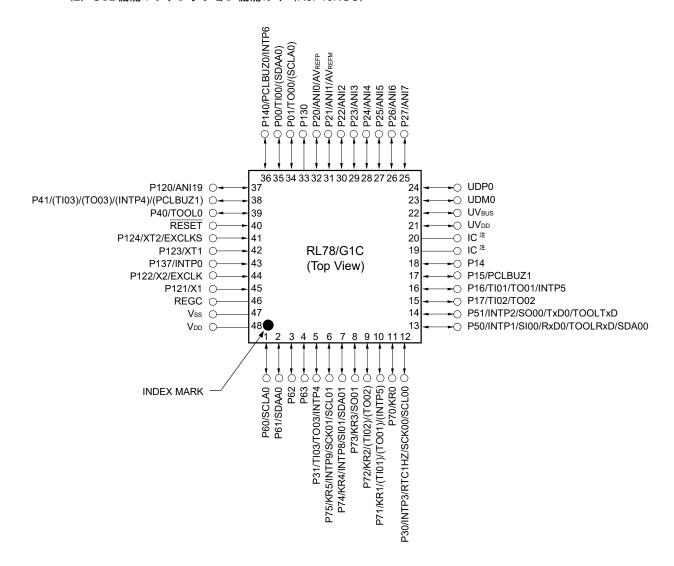

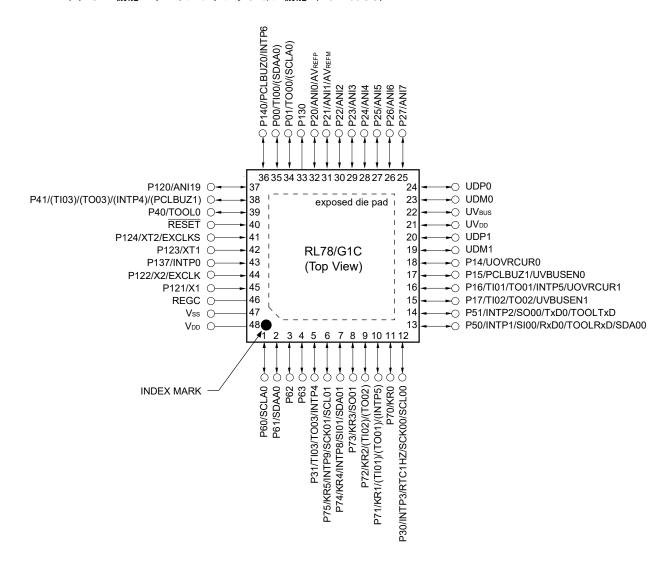

・48ピン: R5F10JGxxxx (xxxx =, CANA, CAFB, CGNA, CGFB)

R5F10KGxxxx (xxxx =, CANA, CAFB, CGNA, CGFB)

このマニュアルは、次の構成に示す機能をユーザに理解していただくことを目的としています。 目 的

構 成 RL78/G1Cのマニュアルは、このマニュアルとソフトウェア編(RL78ファミリ共通)の2冊に分かれて います。

> RL78/G1C ユーザーズ・マニュアル ハードウェア編

●端子機能

●内部ブロック機能

●割り込み

●その他の内蔵周辺機能

●電気的特性

RL78ファミリ ユーザーズ・マニュアル ソフトウェア編

●CPU機能

●命令セット

●命令の説明

- 読み方 このマニュアルを読むにあたっては、電気、論理回路、マイクロコントローラの一般知識を必要とします。

- □一通りの機能を理解しようとするとき

- →目次に従って読んでください。本文欄外の★印は、本版で改訂された主な箇所を示しています。 この"★"をPDF上でコピーして「検索する文字列」に指定することによって、改版箇所を容易に 検索できます。

- □レジスタ・フォーマットの見方

- →ビット番号を□で囲んでいるものは、そのビット名称がアセンブラでは予約語に、コンパイラでは#pragma sfr指令で、sfr変数として定義されているものです。

- □RL78/G1Cマイクロコントローラの命令機能の詳細を知りたいとき

- →別冊のRL78ファミリ ユーザーズ・マニュアル ソフトウェア編 (R01US0015J) を参照してください。

凡 例 データ表記の重み : 左が上位桁、右が下位桁

アクティブ・ロウの表記 : ××× (端子, 信号名称に上線)

注:本文中につけた注の説明

注意: 気をつけて読んでいただきたい内容

備考:本文の補足説明

数の表記 : 2進数···××××または××××B

10進数…×××× 16進数…××××H

#### 関連資料

関連資料は暫定版の場合がありますが、この資料では「暫定」の表示をしておりません。あらかじめご了承ください。

#### デバイスの関連資料

| 資料名                          |        | 資料番号 |        |       |

|------------------------------|--------|------|--------|-------|

|                              | 和      | 文    | 英      | 文     |

| RL78/G1C ユーザーズ・マニュアル ハードウェア編 | このマニ   | ニュアル | R01UH0 | )348E |

| RL78ファミリ ユーザーズ・マニュアル ソフトウェア編 | R01US0 | 015J | R01US0 | 0015E |

## フラッシュ・メモリ書き込み用の資料(ユーザーズ・マニュアル)

| 資 料 名                  |        | 資料番号  |        |       |

|------------------------|--------|-------|--------|-------|

|                        | 和      | 文     | 英      | 文     |

| PG-FP5 フラッシュ・メモリ・プログラマ | R20UT0 | 0008J | R20UT0 | 0008E |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには、必ず最新の資料をご使用ください。

#### その他の資料

| 資 料 名                       | 資料         | 番号         |  |

|-----------------------------|------------|------------|--|

|                             | 和 文        | 英 文        |  |

| ルネサス マイクロコンピュータ RL78ファミリ    | R01CP0003J | R01CP0003E |  |

| 半導体パッケージ実装マニュアル             | R50ZZ0003J | R50ZZ0003E |  |

| NEC半導体デバイスの品質水準             | C11531J    | C11531E    |  |

| 静電気放電 (ESD) 破壊対策ガイド C11892J |            | C11892E    |  |

| 信頼性ハンドブック                   | R51ZZ0001J | R51ZZ0001E |  |

注意 上記関連資料は予告なしに内容を変更することがあります。設計などには、必ず最新の資料をご使用ください。

すべての商標および登録商標は、それぞれの所有者に帰属します。

EEPROMは、ルネサス エレクトロニクス株式会社の登録商標です。

SuperFlashは、米国Silicon Storage Technology, Inc.の米国、日本などの国における登録商標です。

注意:本製品はSilicon Storage Technology, Inc.からライセンスを受けたSuperFlash®を使用しています。

# 目次

| 第1章  | 概                  | 説                                                   | 1  |

|------|--------------------|-----------------------------------------------------|----|

|      |                    |                                                     |    |

| 1. 1 |                    | 徴                                                   |    |

| 1. 2 |                    | <u></u>                                             |    |

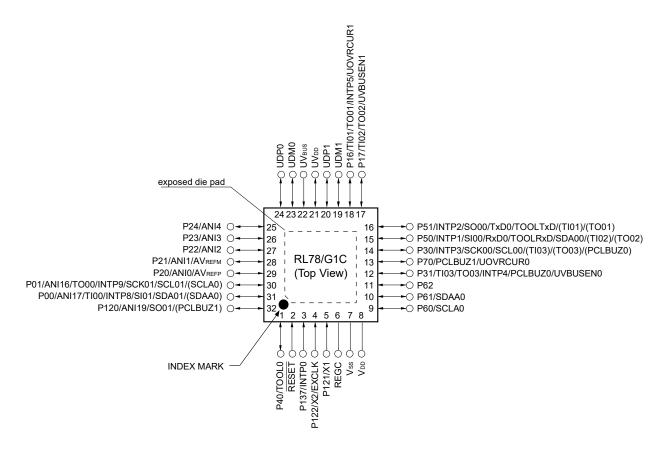

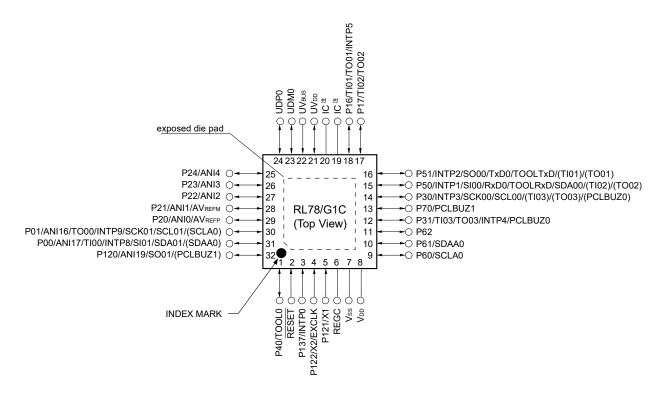

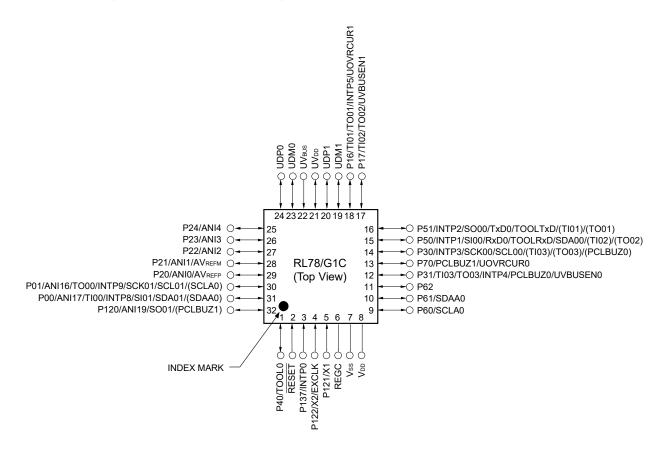

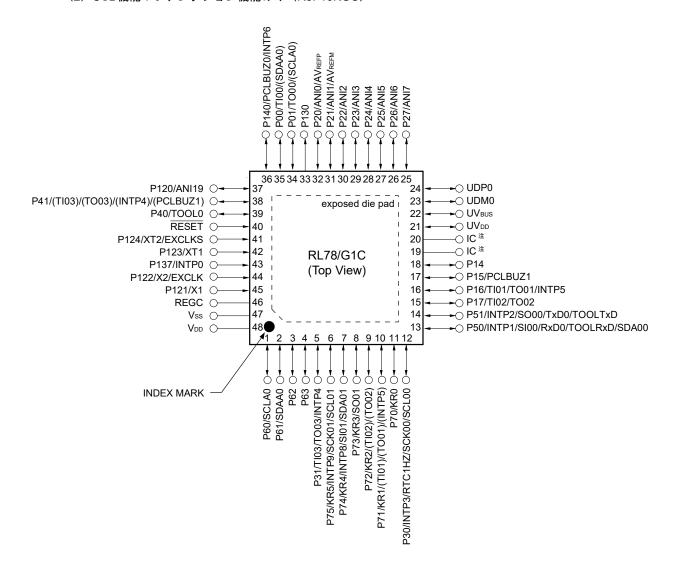

| 1. 3 |                    | 続図(Top View)                                        |    |

|      |                    | 32ピン製品                                              |    |

|      |                    | 48ピン製品                                              |    |

| 1. 4 |                    | 称                                                   |    |

| 1. 5 | ブロッ                | ク図                                                  | 14 |

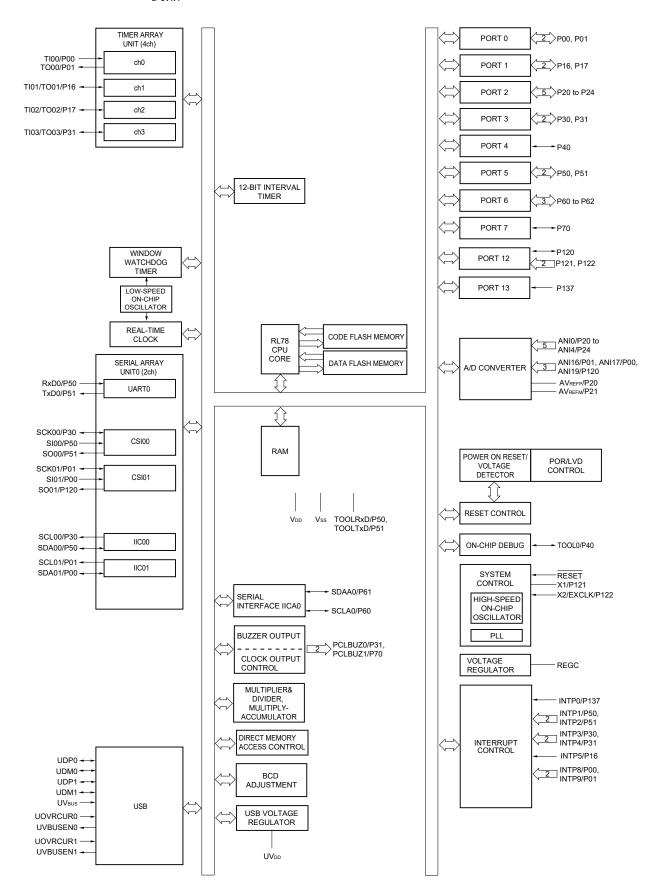

|      | 1. 5. 1            | 32ピン製品                                              | 14 |

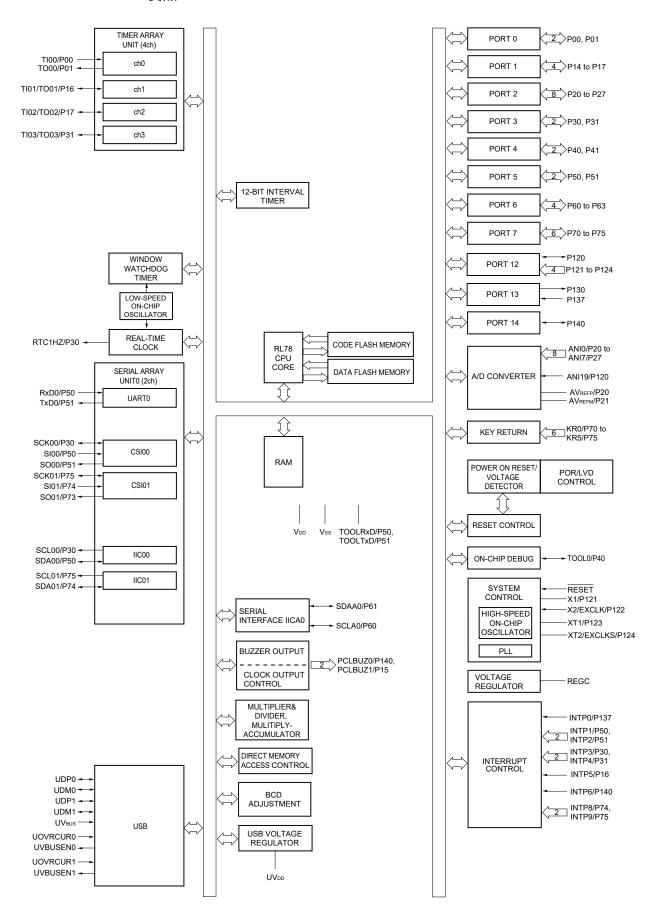

|      | 1. 5. 2            | 48ピン製品                                              | 15 |

| 1. 6 | 機能概                | 要                                                   | 16 |

| ケケヘギ | тп <del>→</del> ти |                                                     | 40 |

| 第2章  | <b></b>            | 能                                                   | 18 |

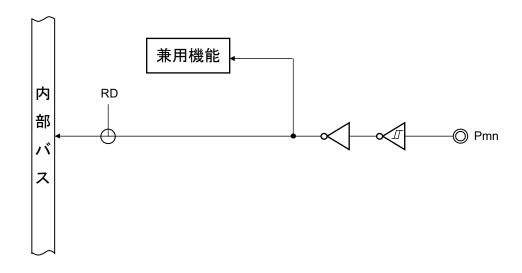

| 2. 1 | ポート                | 機能                                                  | 18 |

|      |                    | <br>32ピン製品                                          |    |

|      |                    | 48ピン製品                                              |    |

| 2.2  |                    | 以外の機能                                               |    |

| 2. 3 |                    | 端子の処理                                               |    |

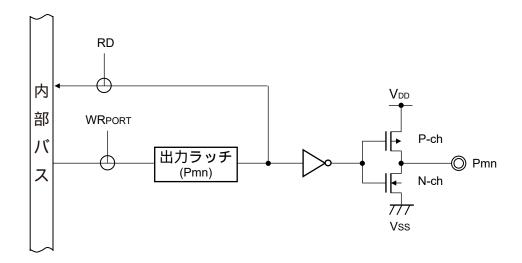

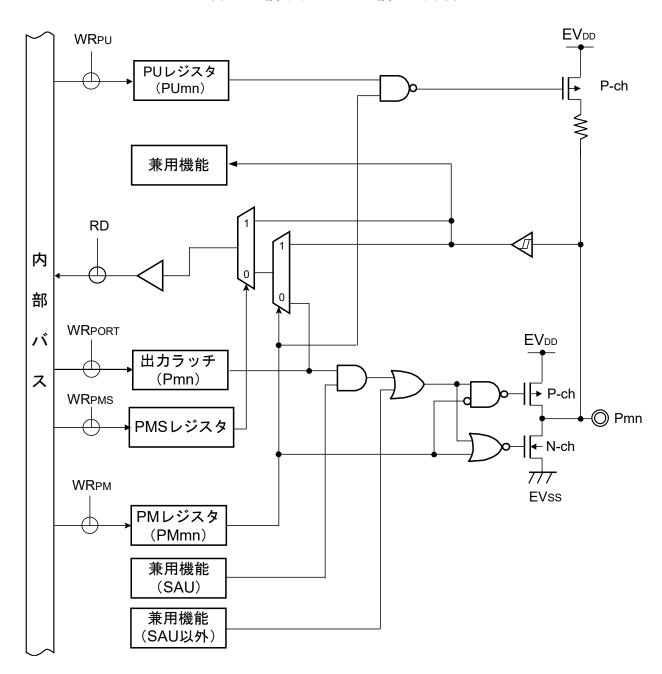

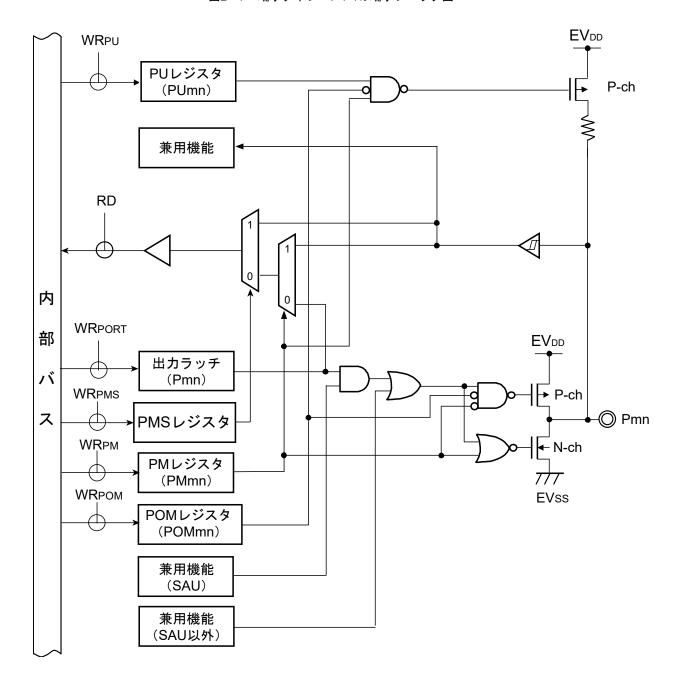

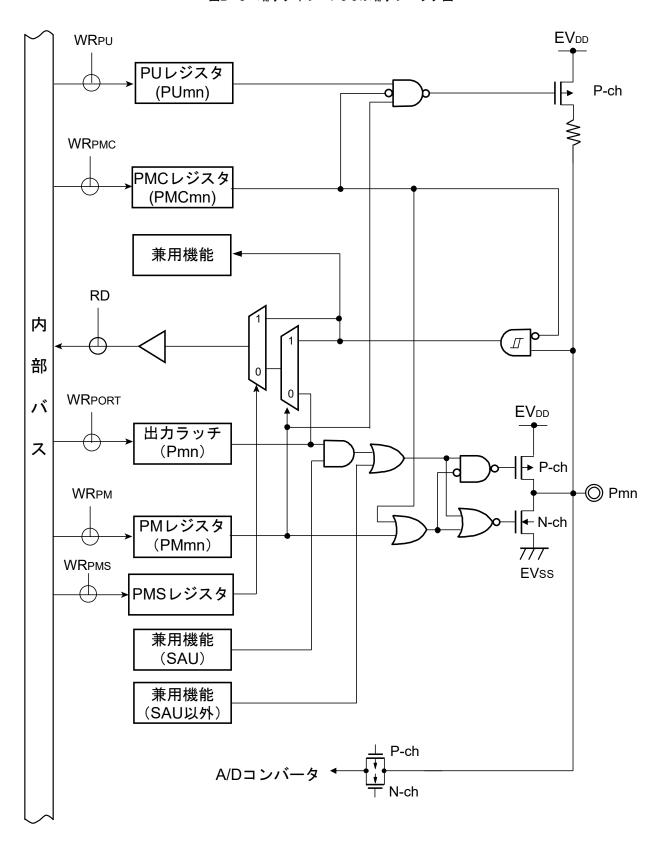

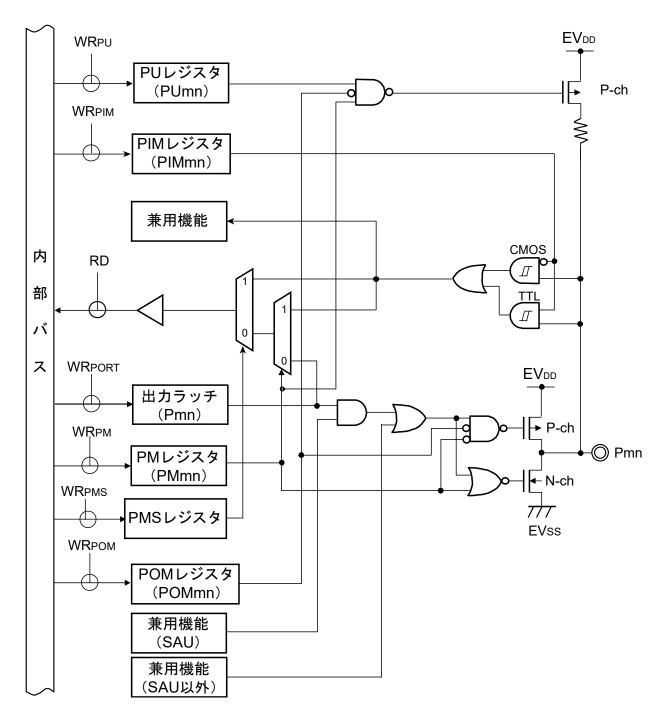

| 2. 4 |                    | ロック図                                                |    |

|      |                    |                                                     |    |

| 第3章  | CPUア               | 'ーキテクチャ                                             | 39 |

|      |                    |                                                     |    |

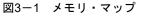

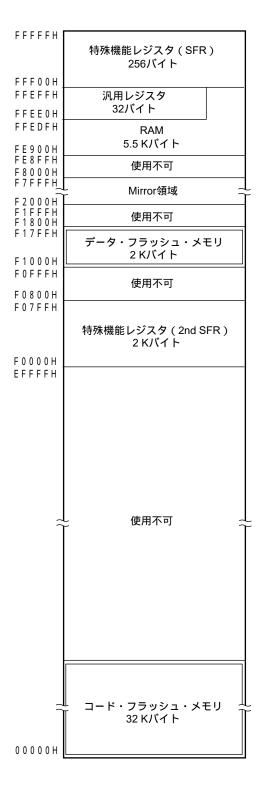

| 3. 1 |                    | 空間                                                  |    |

|      |                    | 内部プログラム・メモリ空間                                       |    |

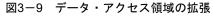

|      | 3. 1. 2            |                                                     |    |

|      | 3. 1. 3            | · · · · · · · · · · · · · · · · · · ·               |    |

|      | 3. 1. 4            | 3 / 122                                             |    |

|      | 3. 1. 5            | 拡張特殊機能レジスタ(2nd SFR:2nd Special Function Register)領域 |    |

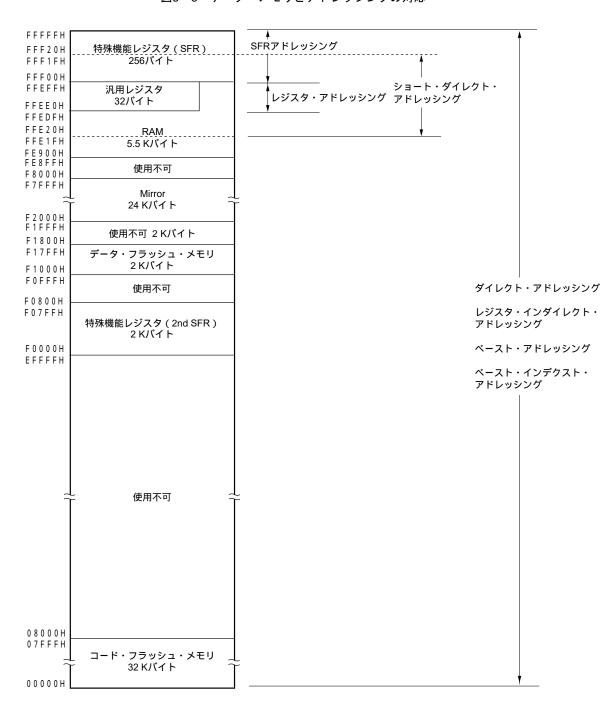

|      |                    | データ・メモリ・アドレッシング                                     |    |

| 3. 2 | プロセ                | ッサ・レジスタ                                             |    |

|      | 3. 2. 1            |                                                     |    |

|      |                    | 汎用レジスタ                                              |    |

|      | 3. 2. 3            | ES, CSレジスタ                                          |    |

|      | 3. 2. 4            | 3                                                   |    |

|      | 3. 2. 5            | 1 3                                                 |    |

| 3. 3 |                    | ドレスのアドレッシング                                         |    |

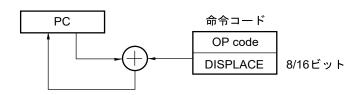

|      |                    | レラティブ・アドレッシング                                       |    |

|      | 3. 3. 2            | イミーディエト・アドレッシング                                     | 70 |

|      |                    | テーブル・インダイレクト・アドレッシング                                |    |

|      | 3. 3. 4            | レジスタ・ダイレクト・アドレッシング                                  | 72 |

| 3. 4 |                    | ータ・アドレスに対するアドレッシング                                  |    |

|      | 3. 4. 1            | インプライド・アドレッシング                                      | 73 |

|      |                    | レジスタ・アドレッシング                                        |    |

|      |                    | ダイレクト・アドレッシング                                       |    |

|      | 3. 4. 4            | ショート・ダイレクト・アドレッシング                                  | 75 |

|      | 3. 4. 5            | SFRアドレッシング                                          | 76 |

|      | 3. 4. 6 レジスタ・インダイレクト・アドレッシング                   |       |

|------|------------------------------------------------|-------|

|      | 3. 4. 7 ベースト・アドレッシング                           | 78    |

|      | 3.4.8 ベースト・インデクスト・アドレッシング                      | 82    |

|      | 3. 4. 9 スタック・アドレッシング                           | 84    |

|      |                                                |       |

| 第4章  | ポート機能                                          | 87    |

| 1 1  | ポートの機能                                         | 97    |

|      | ポートの構成                                         |       |

| 4. 2 | ルートの構成                                         |       |

|      | 4. 2. 2 ポート1                                   |       |

|      | 4. 2. 3 ポート2                                   |       |

|      | 4. 2. 4 ポート3                                   |       |

|      | 4. 2. 5 ポート4                                   |       |

|      | 4. 2. 6 ポート5                                   |       |

|      | 4. 2. 7 ポート6                                   |       |

|      | 4. 2. 8 ポート7                                   |       |

|      | 4. 2. 9 ポート12                                  |       |

|      | 4. 2. 10 ポート13                                 |       |

|      | 4. 2. 11 ポート14                                 |       |

| 4 3  | ポート機能を制御するレジスタ                                 |       |

| 0    | 4. 3. 1 ポート・モード・レジスタ (PMxx)                    |       |

|      | 4. 3. 2 ポート・レジスタ (Pxx)                         |       |

|      | 4. 3. 3 プルアップ抵抗オプション・レジスタ(PUxx)                |       |

|      | 4. 3. 4 ポート入力モード・レジスタ(PIM0, PIM3, PIM5)        |       |

|      | 4. 3. 5 ポート出力モード・レジスタ(POM0, POM3, POM5, POM7)  |       |

|      | 4. 3. 6 ポート・モード・コントロール・レジスタ0, 12 (PMC0, PMC12) |       |

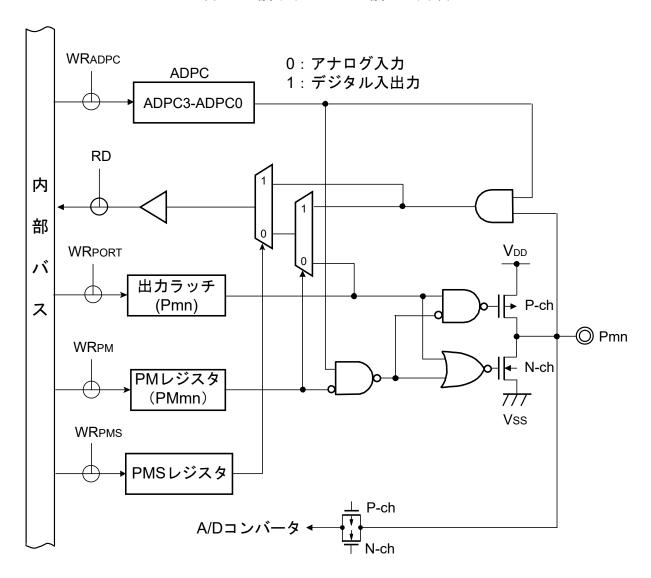

|      | 4. 3. 7 A/Dポート・コンフィギュレーション・レジスタ(ADPC)          |       |

|      | 4. 3. 8 周辺I/Oリダイレクション・レジスタ(PIOR)               | 102   |

| 4. 4 | ポート機能の動作                                       | 103   |

|      | 4.4.1 入出力ポートへの書き込み                             | 103   |

|      | 4.4.2 入出力ポートからの読み出し                            | 103   |

|      | 4. 4. 3 入出力ポートでの演算                             | 103   |

|      | 4.4.4 入出力バッファによる異電位(1.8 V系, 2.5 V系, 3 V系)対応    | 104   |

| 4. 5 | 兼用機能使用時のレジスタ設定                                 | 106   |

|      | 4. 5. 1 兼用機能使用時の基本的な考え方                        | 106   |

|      | 4.5.2 出力機能を使用しない兼用機能のレジスタ設定                    | 107   |

|      | 4.5.3 使用するポート機能および兼用機能のレジスタ設定例                 | 108   |

| 4. 6 | ポート機能使用時の注意事項                                  | 117   |

|      | 4.6.1 ポート・レジスタn (Pn) に対する1ビット・メモリ操作命令に関する注意事項  | į 117 |

|      | 4.6.2 端子設定に関する注意事項                             | 118   |

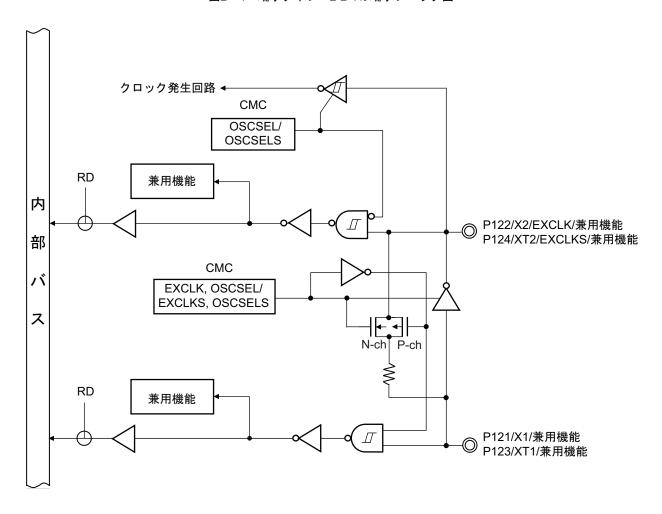

| 第5章  | クロック発生回路                                       | 119   |

|      |                                                |       |

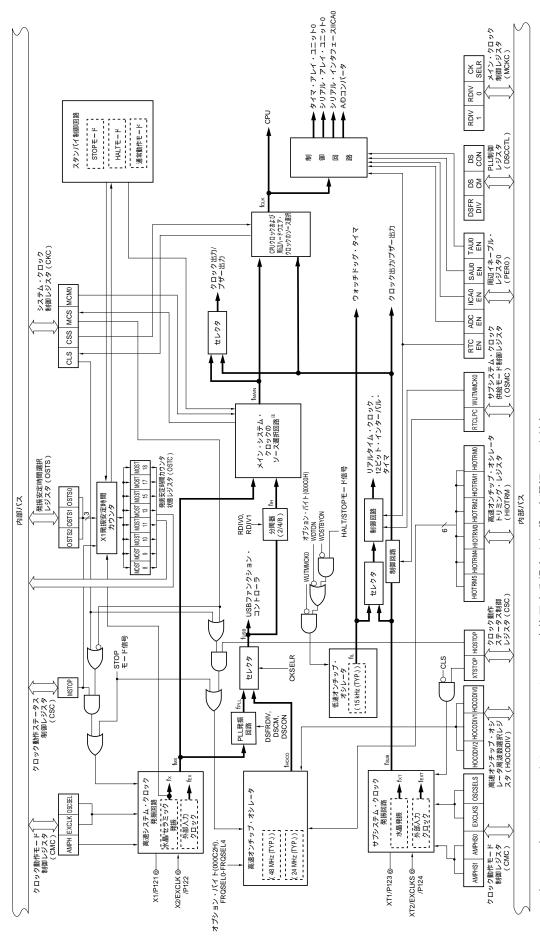

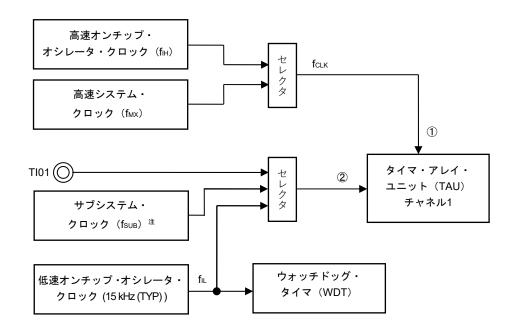

|      | クロック発生回路の機能                                    |       |

|      | クロック発生回路の構成                                    |       |

| 5. 3 | クロック発生回路を制御するレジスタ                              |       |

|      | 5. 3. 1 クロック動作モード制御レジスタ(CMC)                   |       |

|      | 5. 3. 2 システム・クロック制御レジスタ(CKC)                   |       |

|      | 5.3.3 クロック動作ステータス制御レジスタ (CSC)                  |       |

|      | 5.3.4 発振安定時間カウンタ状態レジスタ(OSTC)                   | 129   |

|            | 5.3.5 発振安定時間選択レジスタ(OSTS)                | 131 |

|------------|-----------------------------------------|-----|

|            | 5.3.6 周辺イネーブル・レジスタ0 (PERO)              | 133 |

|            | 5.3.7 サブシステム・クロック供給モード制御レジスタ(OSMC)      | 135 |

|            | 5.3.8 高速オンチップ・オシレータ周波数選択レジスタ(HOCODIV)   | 136 |

|            | 5.3.9 高速オンチップ・オシレータ・トリミング・レジスタ(HIOTRM)  | 137 |

|            | 5. 3. 10 PLL制御レジスタ(DSCCTL)              | 138 |

|            | 5. 3. 11 メイン・クロック制御レジスタ(MCKC)           | 140 |

| 5. 4       | システム・クロック発振回路                           | 141 |

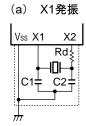

|            | 5. 4. 1 X1発振回路                          | 141 |

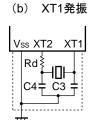

|            | 5. 4. 2 XT1発振回路                         | 141 |

|            | 5. 4. 3 高速オンチップ・オシレータ                   | 145 |

|            | 5. 4. 4 低速オンチップ・オシレータ                   | 145 |

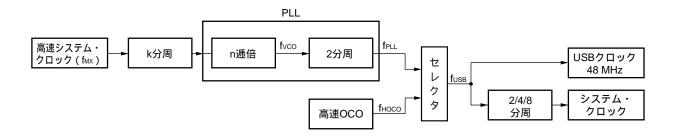

|            | 5. 4. 5 PLL (Phase Locked Loop)         | 145 |

| 5. 5       | ・<br>クロック発生回路の動作                        |     |

| 5. 6       | クロックの制御                                 | 148 |

|            | 5. 6. 1 高速オンチップ・オシレータの設定例               |     |

|            | 5. 6. 2 X1発振回路の設定例                      |     |

|            | 5. 6. 3 XT1発振回路の設定例                     | 150 |

|            | 5. 6. 4 PLL回路の設定例                       | 151 |

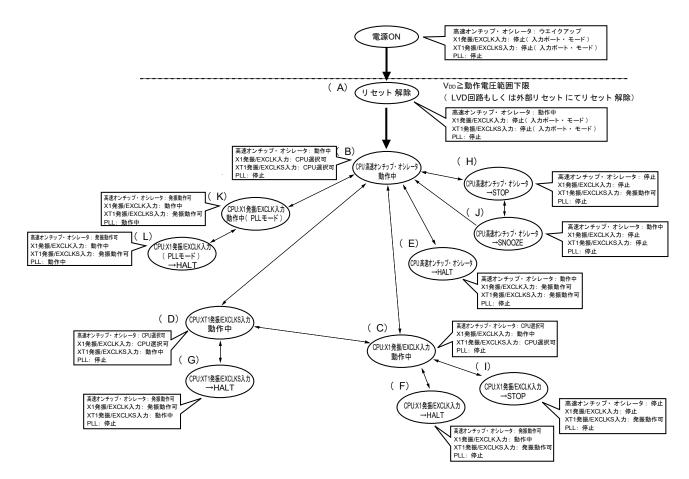

|            | 5. 6. 5 CPUクロック状態移行図                    |     |

|            | 5. 6. 6 CPUクロックの移行前の条件と移行後の処理           |     |

|            | 5.6.7 CPUクロックの切り替えとシステム・クロックの切り替えに要する時間 |     |

|            | 5. 6. 8       クロック発振停止前の条件              |     |

| 5. 7       | 発振子と発振回路定数                              |     |

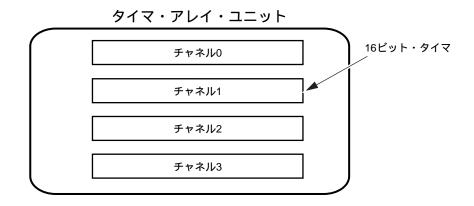

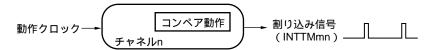

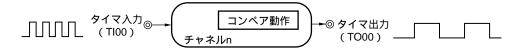

| 6. 1       | タイマ・アレイ・ユニットの機能                         | 170 |

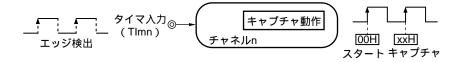

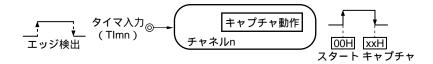

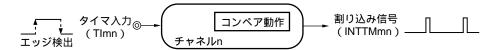

| <b>.</b> . | 6. 1. 1 単独チャネル動作機能                      |     |

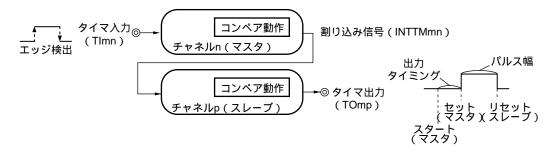

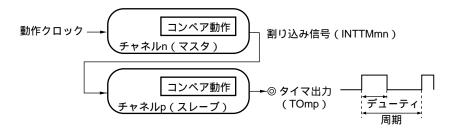

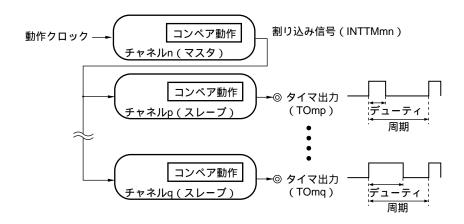

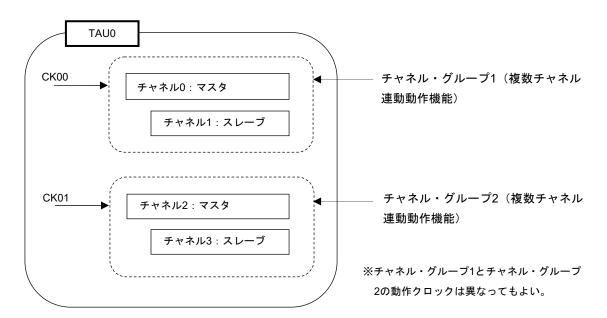

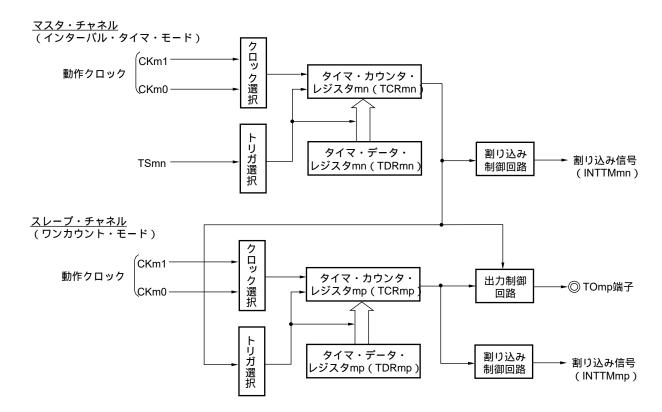

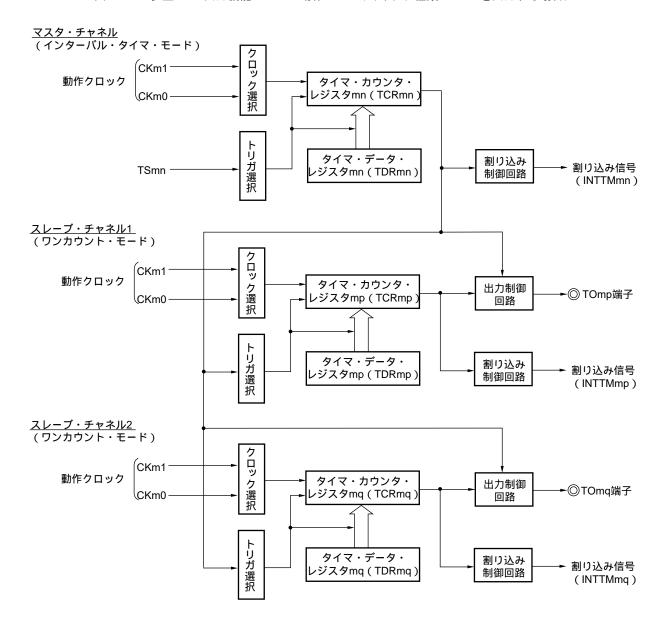

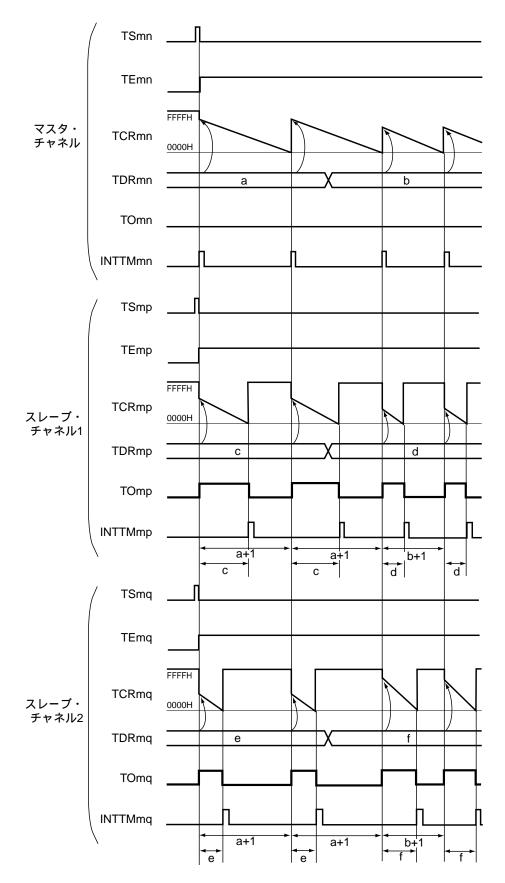

|            | 6. 1. 2 複数チャネル連動動作機能                    |     |

|            | 6.1.3 8ビット・タイマ動作機能(チャネル1,3のみ)           |     |

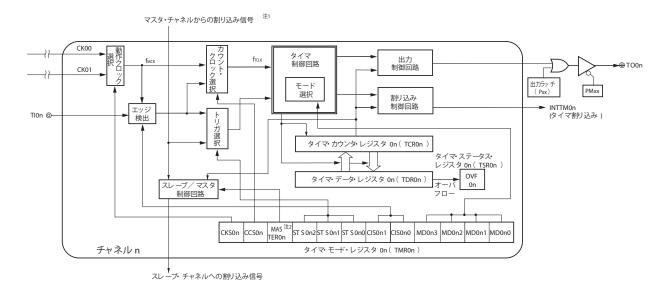

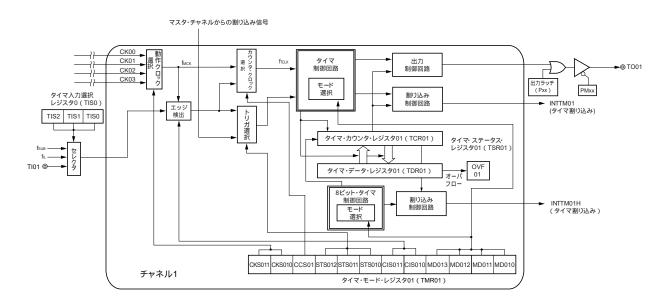

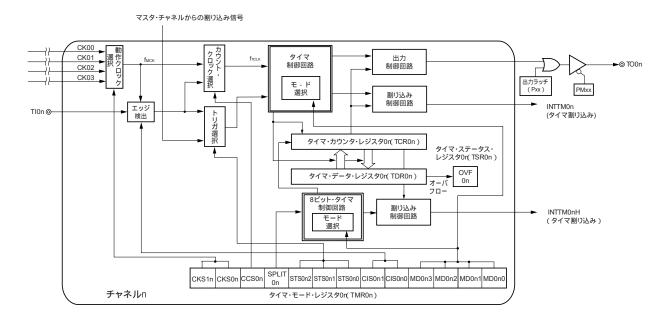

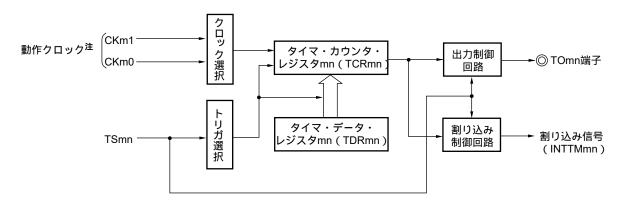

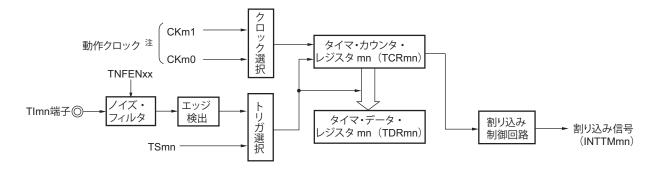

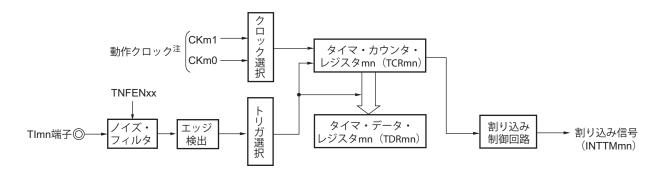

| 6. 2       | タイマ・アレイ・ユニットの構成                         |     |

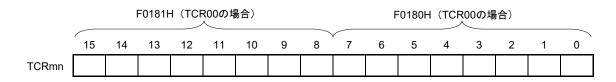

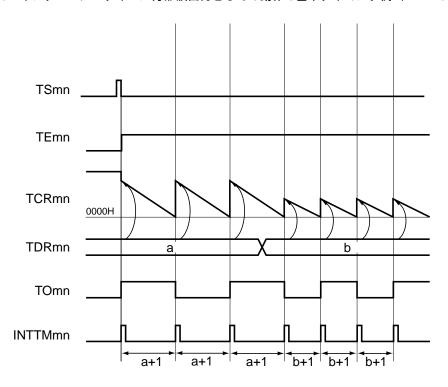

|            | 6. 2. 1 タイマ・カウンタ・レジスタmn (TCRmn)         |     |

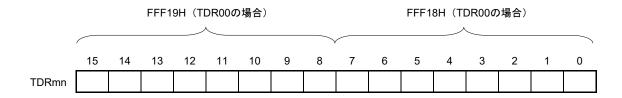

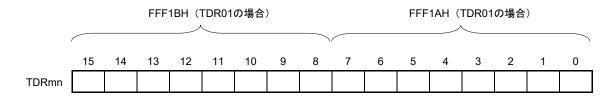

|            | 6. 2. 2 タイマ・データ・レジスタmn (TDRmn)          |     |

| 6. 3       |                                         |     |

|            | 6.3.1 周辺イネーブル・レジスタ0 (PER0)              |     |

|            | 6.3.2 タイマ・クロック選択レジスタm(TPSm)             | 182 |

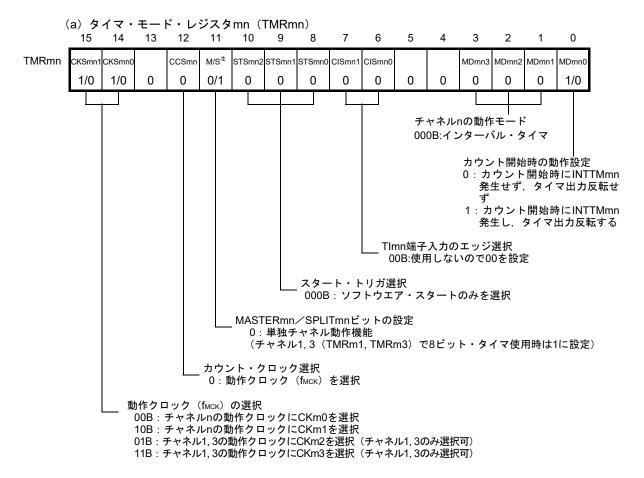

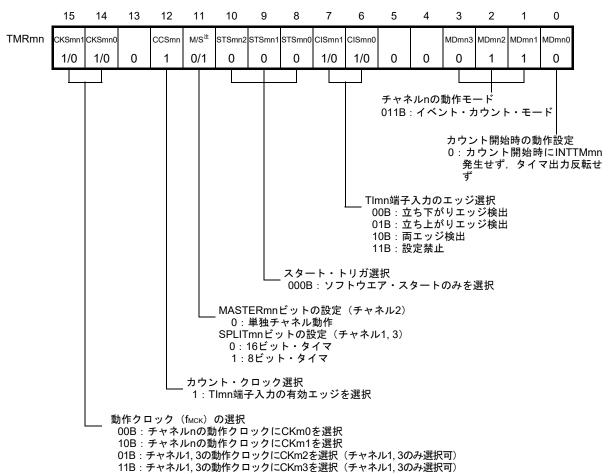

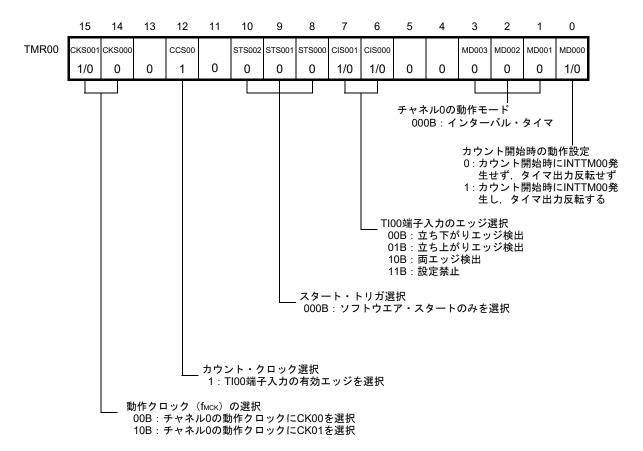

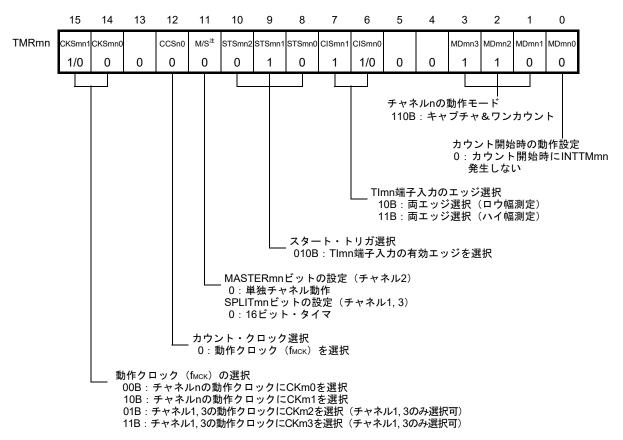

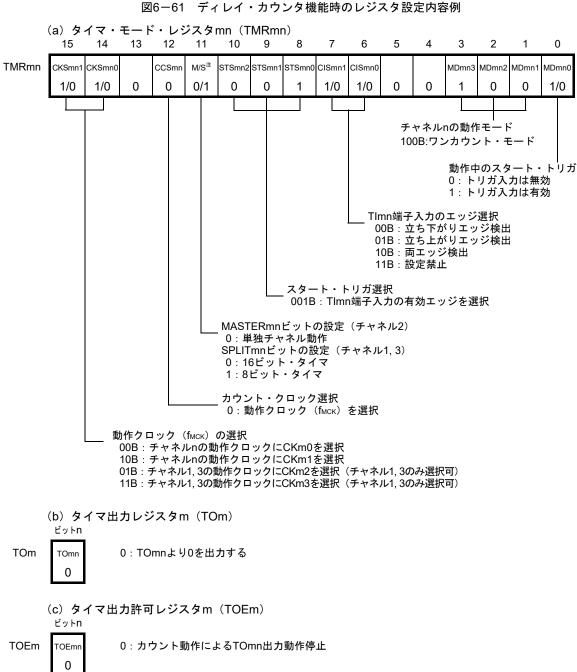

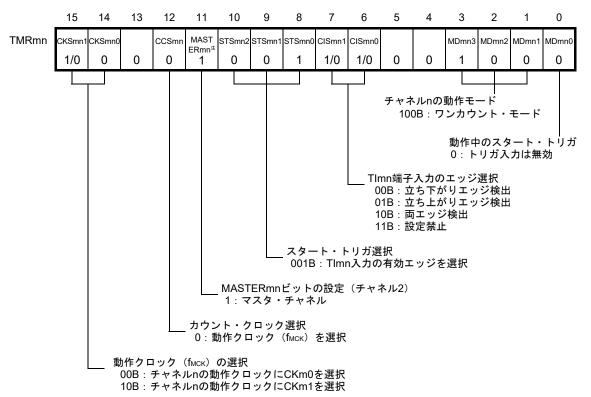

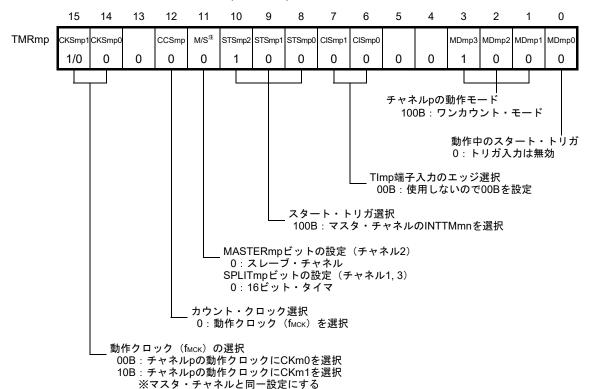

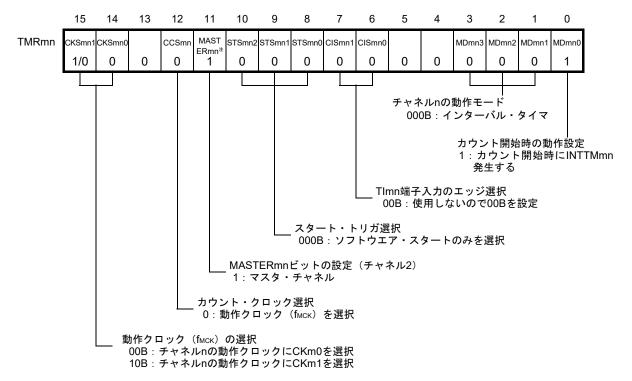

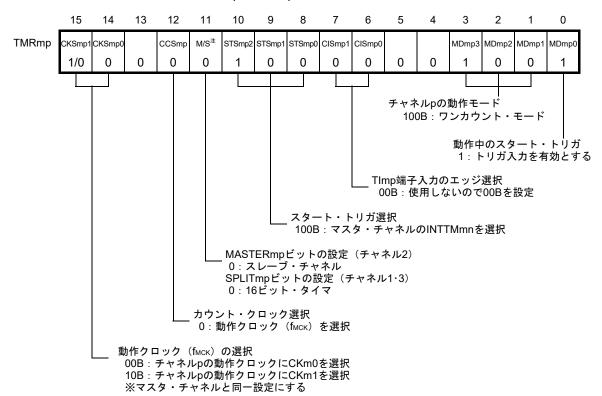

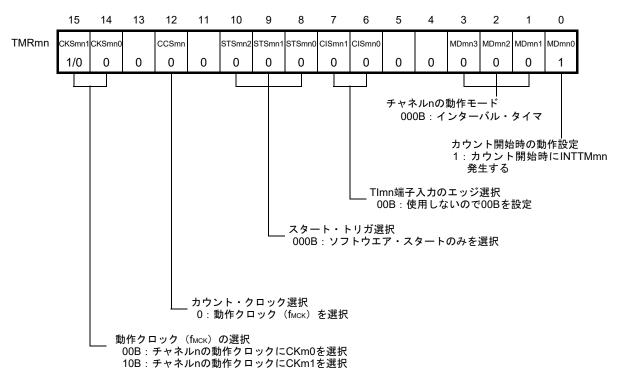

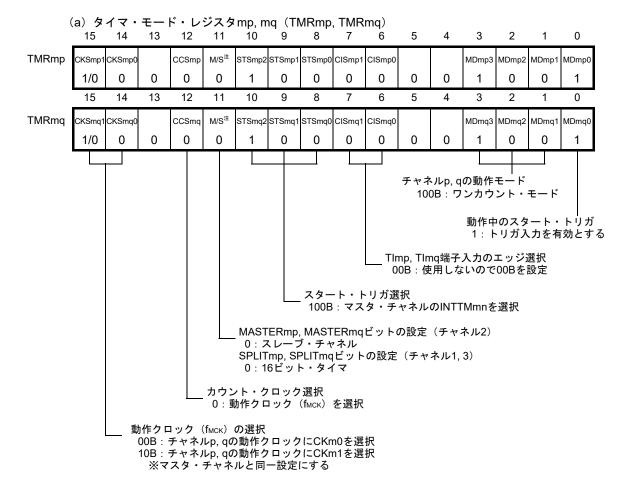

|            | 6.3.3 タイマ・モード・レジスタmn (TMRmn)            |     |

|            | 6.3.4 タイマ・ステータス・レジスタmn (TSRmn)          |     |

|            | 6.3.5 タイマ・チャネル許可ステータス・レジスタm (TEm)       |     |

|            | 6.3.6 タイマ・チャネル開始レジスタm(TSm)              |     |

|            | 6.3.7 タイマ・チャネル停止レジスタm(TTm)              | 194 |

|            | 6.3.8 タイマ入力選択レジスタ0(TISO)                |     |

|            | 6.3.9 タイマ出力許可レジスタm(TOEm)                | 196 |

|            | 6.3.10 タイマ出力レジスタm(TOm)                  |     |

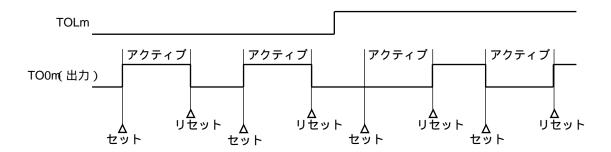

|            | 6. 3. 11 タイマ出力レベル・レジスタm(TOLm)           |     |

|            | 6.3.12 タイマ出力モード・レジスタm(TOMm)             |     |

|            | 6. 3. 13 ノイズ・フィルタ許可レジスタ1(NFEN1)         |     |

|            | 6.3.14 タイマ入出力端子のポート機能を制御するレジスタ          |     |

| 6. 4       | タイマ・アレイ・ユニットの基本ルール                      |     |

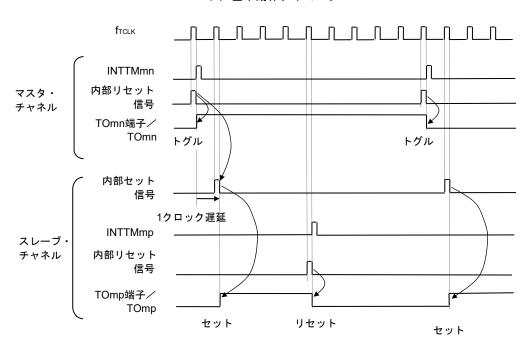

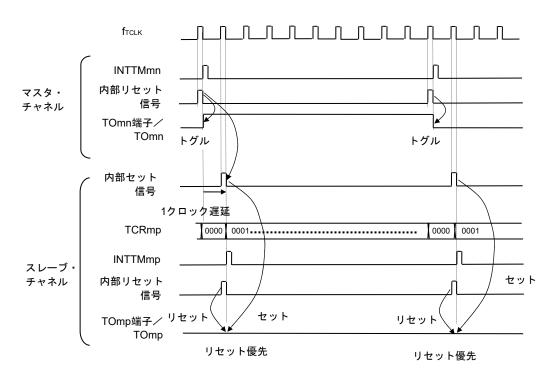

|            | 6. 4. 1 複数チャネル連動動作機能の基本ルール              |     |

|            | 6.4.2 8ビット・タイマ動作機能の基本ルール(チャネル1,3のみ)     | 204 |

| 6. 5                 | カウンタの動作                                                        | 205                                           |

|----------------------|----------------------------------------------------------------|-----------------------------------------------|

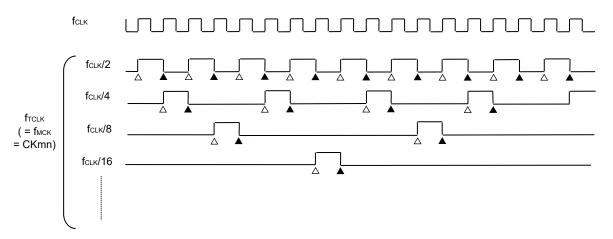

|                      | 6. 5. 1 カウント・クロック (fтсык)                                      | 205                                           |

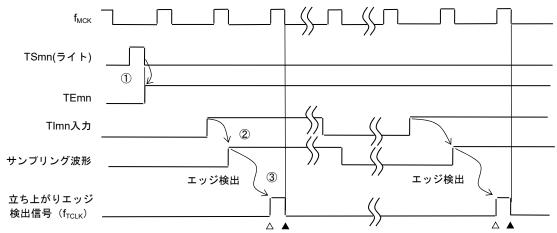

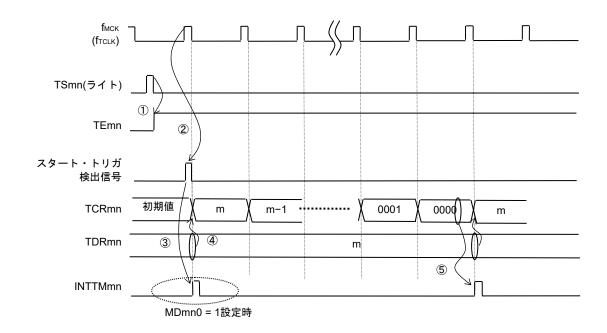

|                      | 6. 5. 2 カウンタのスタート・タイミング                                        | 207                                           |

|                      | 6. 5. 3 カウンタの動作                                                | 208                                           |

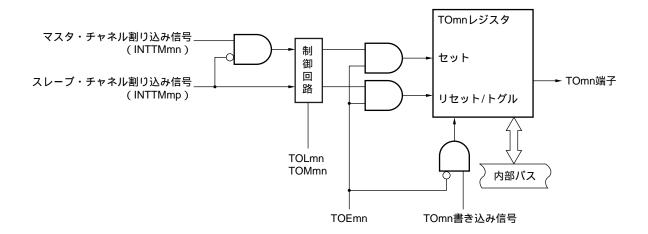

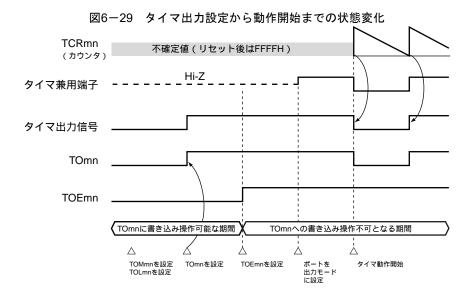

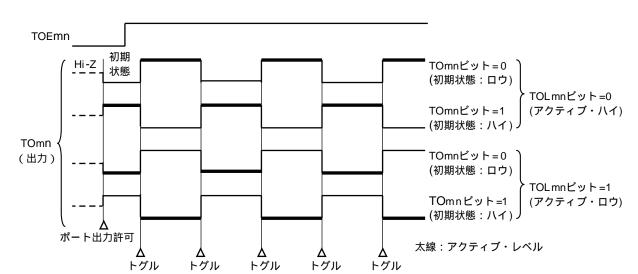

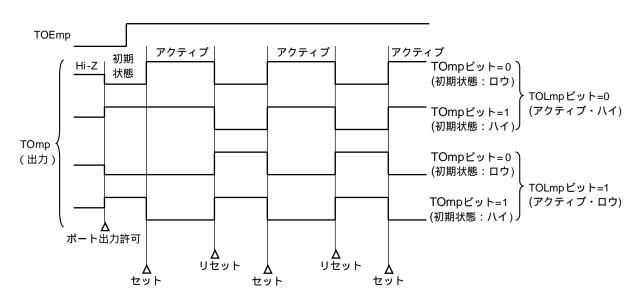

| 6. 6                 | チャネル出力(TOmn端子)の制御                                              | 213                                           |

|                      | 6. 6. 1 TOmn端子の出力回路の構成                                         | 213                                           |

|                      | 6. 6. 2 TOmn端子の出力設定                                            | 214                                           |

|                      | 6. 6. 3 チャネル出力操作時の注意事項                                         | 215                                           |

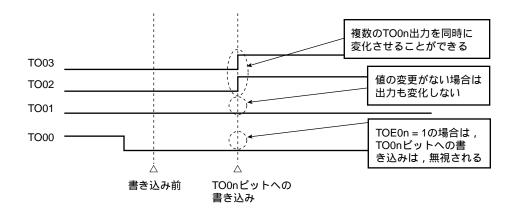

|                      | 6. 6. 4 TOmnビットの一括操作                                           | 220                                           |

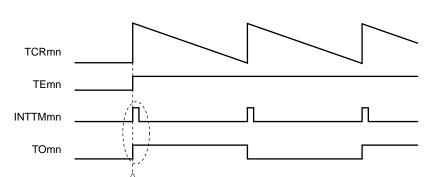

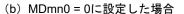

|                      | 6.6.5 カウント動作開始時のタイマ割り込みとTOmn端子出力について                           | 221                                           |

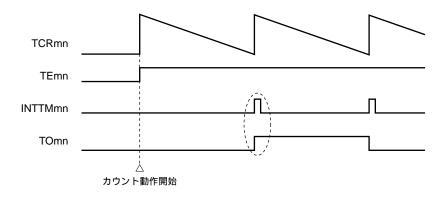

| 6. 7                 | タイマ入力(Tlmn)の制御                                                 | 222                                           |

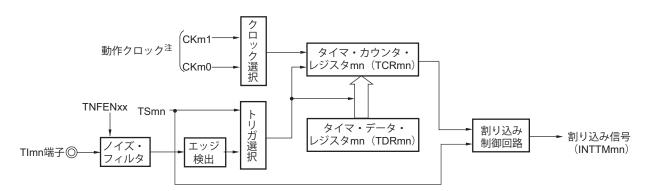

|                      | 6. 7. 1 Tlmnの入力回路構成                                            | 222                                           |

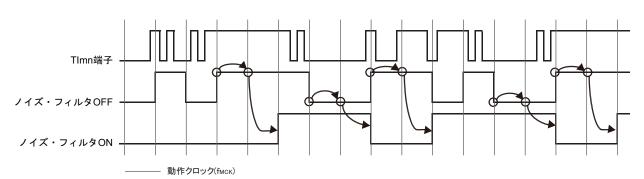

|                      | 6.7.2 ノイズ・フィルタ                                                 | 222                                           |

|                      | 6.7.3 チャネル入力操作時の注意事項                                           | 223                                           |

| 6.8                  | タイマ・アレイ・ユニットの単独チャネル動作機能                                        | 224                                           |

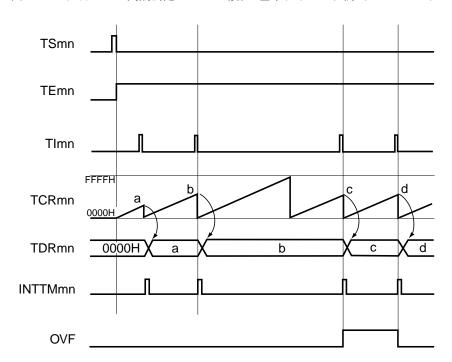

|                      | 6.8.1 インターバル・タイマ/方形波出力としての動作                                   | 224                                           |

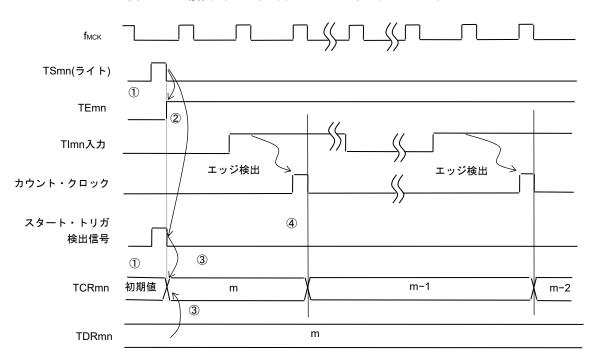

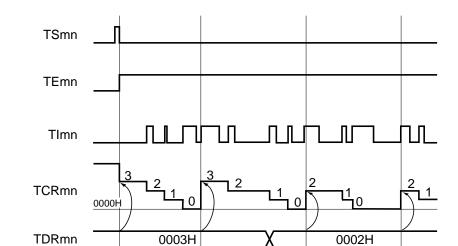

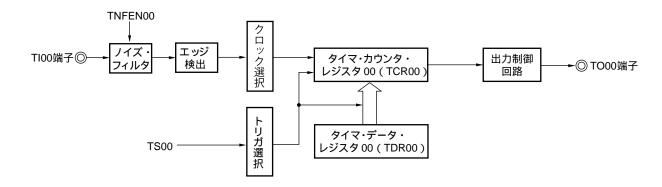

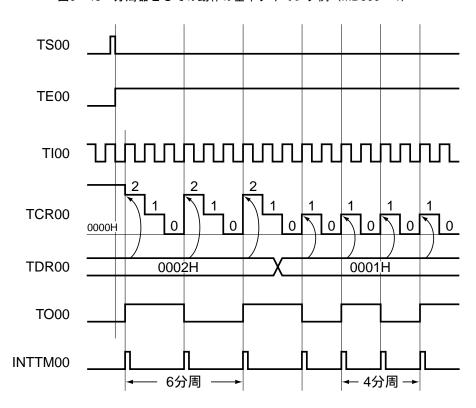

|                      | 6.8.2 外部イベント・カウンタとしての動作                                        | 229                                           |

|                      | 6.8.3 分周器としての動作(チャネル0のみ)                                       | 233                                           |

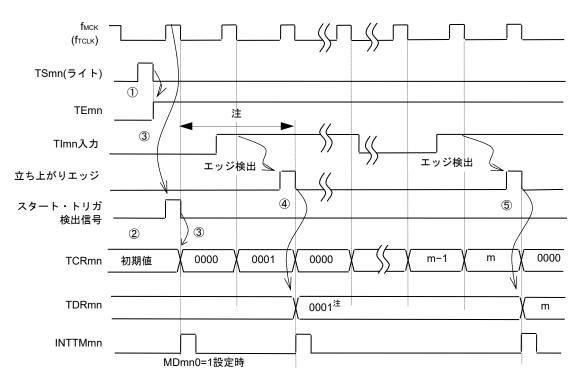

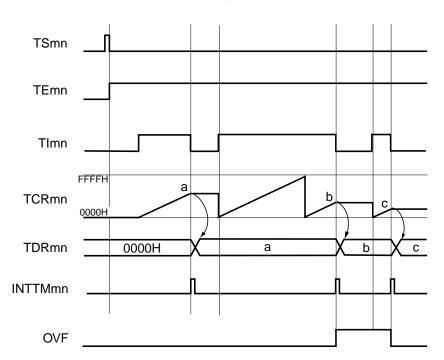

|                      | 6.8.4 入力パルス間隔測定としての動作                                          |                                               |

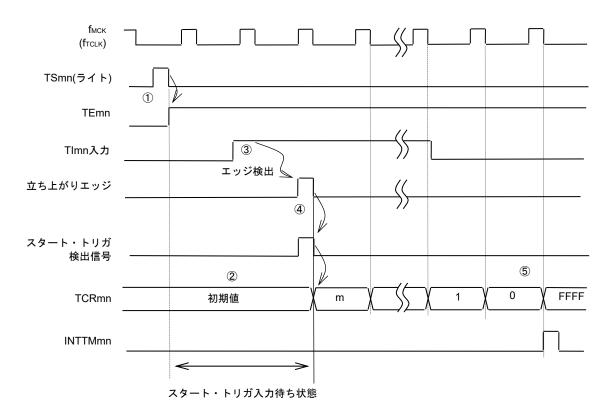

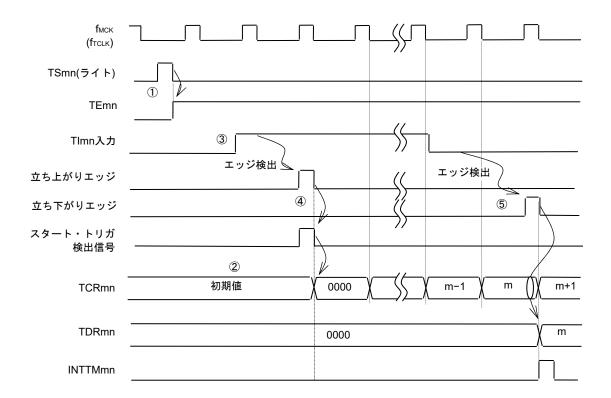

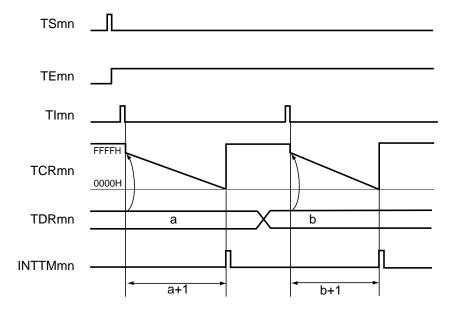

|                      | 6.8.5 入力信号のハイ/ロウ・レベル幅測定としての動作                                  | 241                                           |

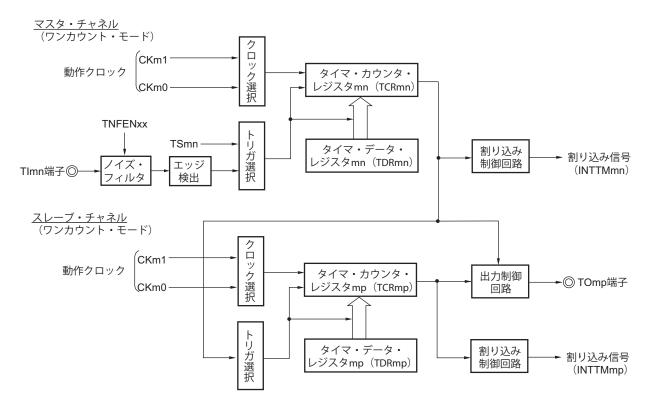

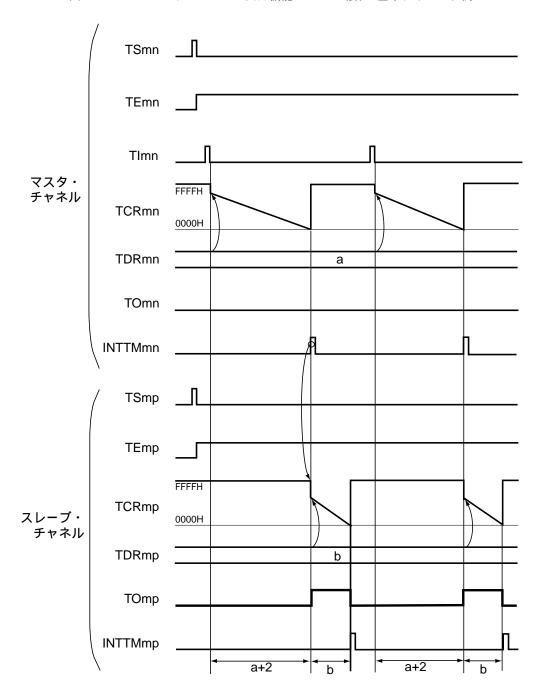

|                      | 6.8.6 ディレイ・カウンタとしての動作                                          |                                               |

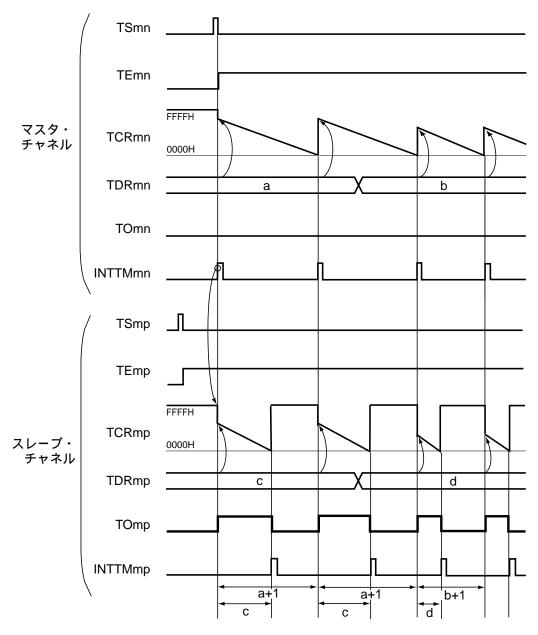

| 6. 9                 | タイマ・アレイ・ユニットの複数チャネル連動動作機能                                      |                                               |

|                      | 6.9.1 ワンショット・パルス出力機能としての動作                                     |                                               |

|                      | 6.9.2 PWM機能としての動作                                              | 256                                           |

|                      | 6. 9. 3 多重PWM出力機能としての動作                                        |                                               |

| 6. 10                | ・ タイマ・アレイ・ユニット使用時の注意事項                                         |                                               |

|                      | 6. 10. 1 タイマ出力使用時の注意事項                                         |                                               |

|                      |                                                                |                                               |

|                      |                                                                |                                               |

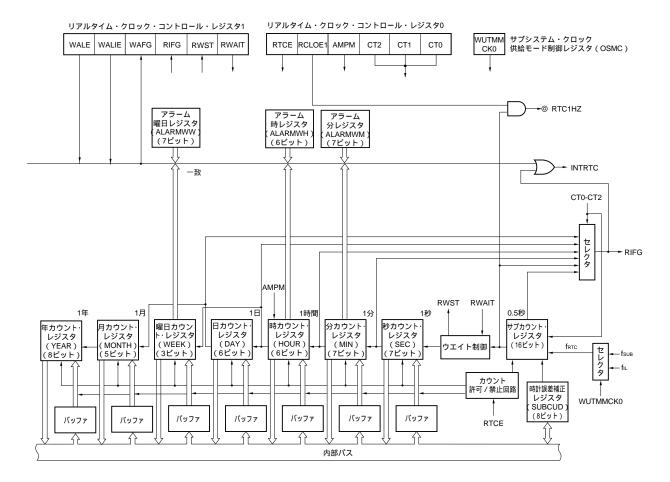

| 第7章                  | リアルタイム・クロック                                                    | 272                                           |

| 第7章                  | リアルタイム・クロック                                                    | 272                                           |

| 第7章<br>7.1           | リアルタイム・クロックリアルタイム・クロックの機能                                      |                                               |

| 7. 1                 |                                                                | 272                                           |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能                                                 | 272<br>273                                    |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成                                   | 272<br>273<br>275                             |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成リアルタイム・クロックの構成リアルタイム・クロックを制御するレジスタ | 272<br>273<br>275                             |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成リアルタイム・クロックの構成リアルタイム・クロックを制御するレジスタ | 272<br>273<br>275<br>276                      |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成リアルタイム・クロックを制御するレジスタ               | 272<br>273<br>275<br>276<br>277               |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成リアルタイム・クロックを制御するレジスタ               | 272<br>273<br>275<br>276<br>277<br>278        |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成リアルタイム・クロックを制御するレジスタ               | 272<br>273<br>275<br>276<br>277<br>278        |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成リアルタイム・クロックを制御するレジスタ               | 272273275276277278279281                      |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成リアルタイム・クロックを制御するレジスタ               | 272<br>273<br>275<br>276<br>277<br>279<br>281 |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成リアルタイム・クロックを制御するレジスタ               | 272273275276277278279281282                   |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成リアルタイム・クロックを制御するレジスタ               | 272273275276277278281281282284                |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックの構成リアルタイム・クロックを制御するレジスタ               |                                               |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能リアルタイム・クロックを制御するレジスタ                             |                                               |

| 7. 1<br>7. 2         | リアルタイム・クロックの機能                                                 |                                               |

| 7. 1<br>7. 2<br>7. 3 | リアルタイム・クロックの機能                                                 |                                               |

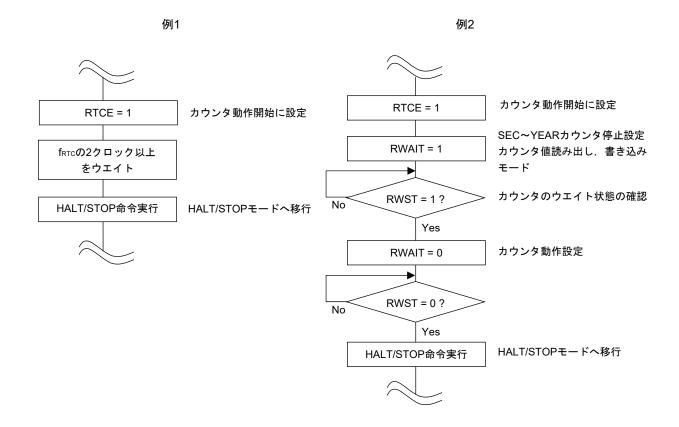

|       | 7. 4. 2 動作開始後のHALT/STOPモードへの移行          | 292  |

|-------|-----------------------------------------|------|

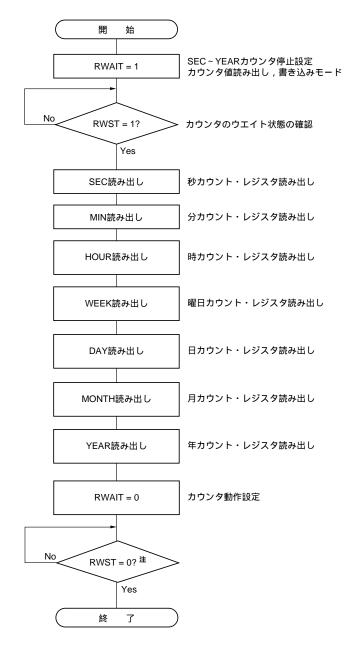

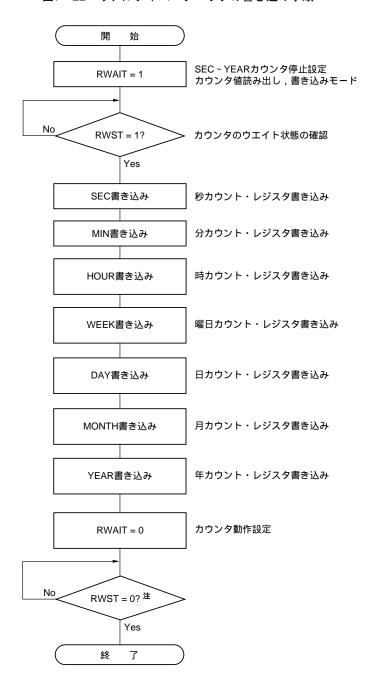

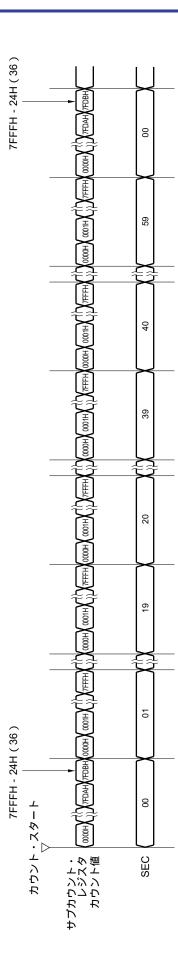

|       | 7.4.3 リアルタイム・クロックのカウンタ読み出し/書き込み         | 293  |

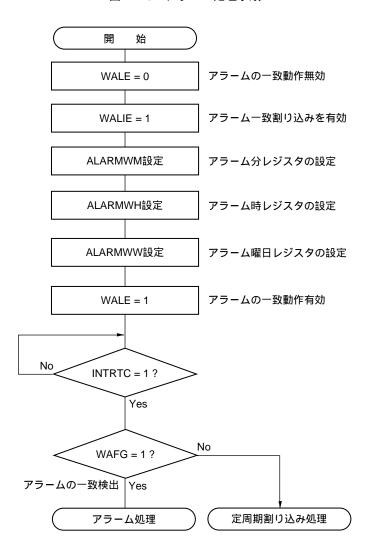

|       | 7.4.4 リアルタイム・クロックのアラーム設定                | 295  |

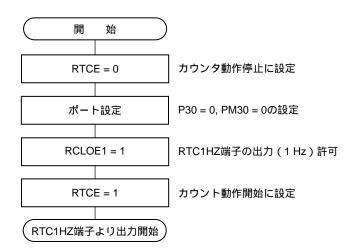

|       | 7. 4. 5 リアルタイム・クロックの1 Hz出力              | 296  |

|       | 7.4.6 リアルタイム・クロックの時計誤差補正例               | 297  |

| 笙Q音   | 12ビット・インターバル・タイマ                        | 302  |

| カロ早   | 12L9 P - 4 D3 70D - 34 4                |      |

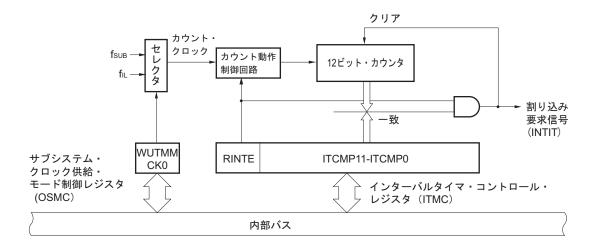

| 8. 1  |                                         |      |

| 8. 2  |                                         |      |

| 8. 3  | = · · · · · · · · · · · · · · · · · · · |      |

|       | 8.3.1 周辺イネーブル・レジスタ0(PERO)               |      |

|       | 8.3.2 サブシステム・クロック供給モード制御レジスタ(OSMC)      |      |

|       | 8.3.3 インターバル・タイマ・コントロール・レジスタ(ITMC)      |      |

| 8. 4  | 12ビット・インターバル・タイマの動作                     |      |

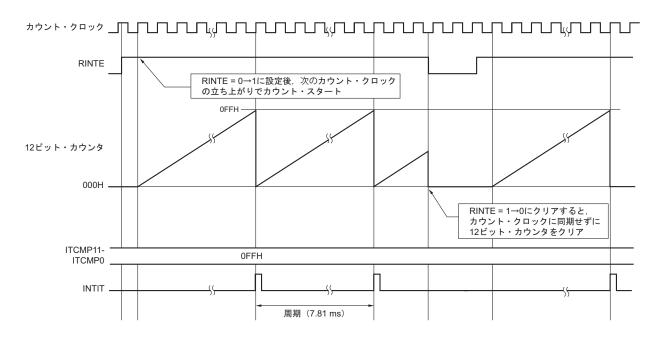

|       | 8.4.1 12ビット・インターバル・タイマの動作タイミング          | 307  |

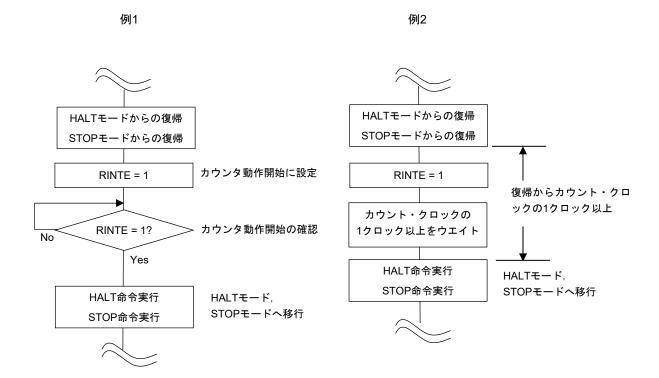

|       | 8. 4. 2 HALT/STOPモードから復帰後にカウンタ動作開始し,    |      |

|       | 再度HALT/STOPモードへの移行                      | 308  |

| 第9章   | クロック出力/ブザー出力制御回路                        | 309  |

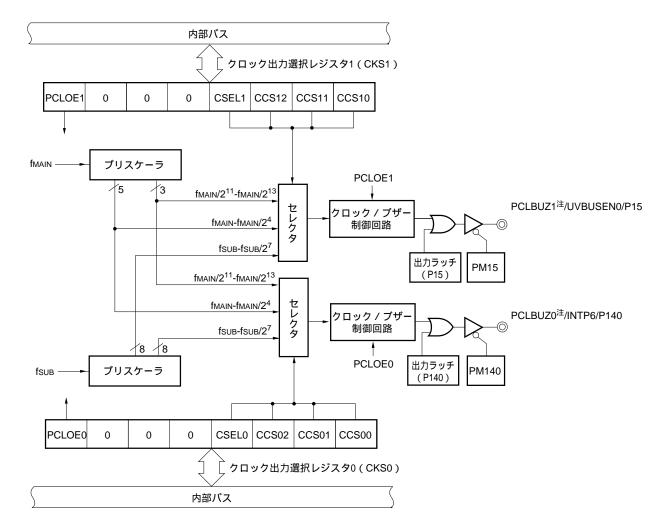

| 9. 1  | クロック出力/ブザー出力制御回路の機能                     | 309  |

| 9. 2  |                                         |      |

| 9. 3  |                                         |      |

|       | 9. 3. 1 クロック出力選択レジスタn(CKSn)             |      |

|       | 9.3.2 クロック出力/ブザー出力端子のポート機能を制御するレジスタ     |      |

| 9. 4  | クロック出力/ブザー出力制御回路の動作                     |      |

|       | 9. 4. 1 出力端子の動作                         |      |

| 9. 5  |                                         |      |

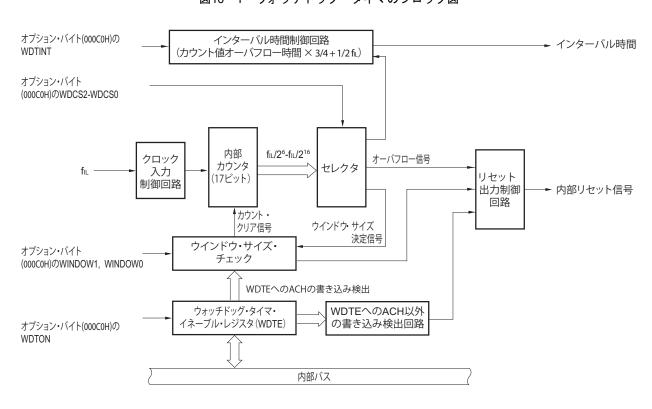

| 第10章  | ウォッチドッグ・タイマ                             | 315  |

| 10    | 1 ウォッチドッグ・タイマの機能                        | 315  |

|       | - ウォッチドッグ・タイマの構成                        |      |

|       | - ウォッチドッグ・タイマを制御するレジスタ                  |      |

|       | 10.3.1 ウォッチドッグ・タイマ・イネーブル・レジスタ(WDTE)     |      |

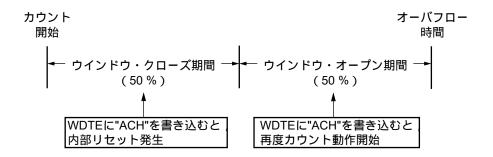

| 10. 4 | 4 ウォッチドッグ・タイマの動作                        |      |

|       | 10.4.1 ウォッチドッグ・タイマの動作制御                 |      |

|       | 10. 4. 2 ウォッチドッグ・タイマのオーバフロー時間の設定        |      |

|       | 10.4.3 ウォッチドッグ・タイマのウインドウ・オープン期間の設定      |      |

|       | 10.4.4 ウォッチドッグ・タイマのインターバル割り込みの設定        |      |

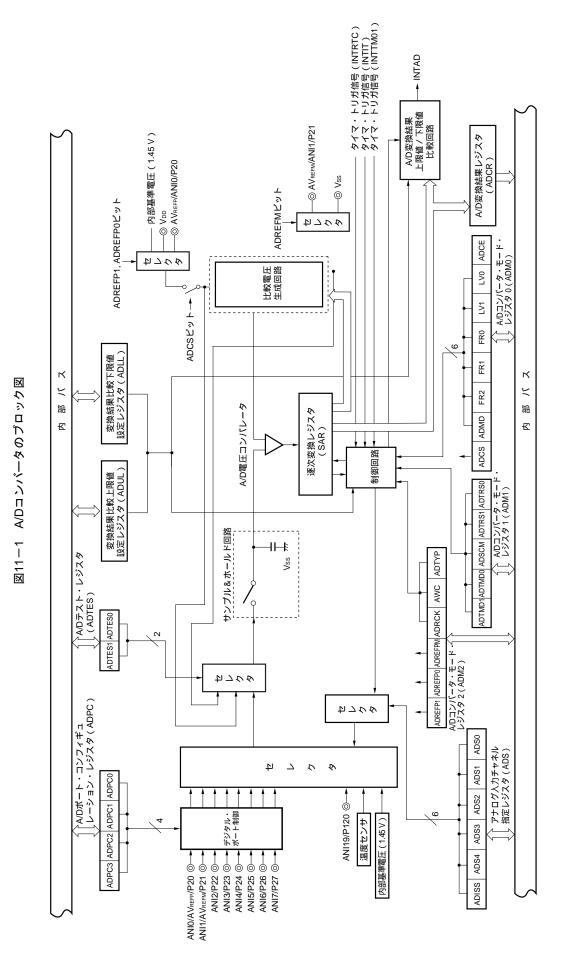

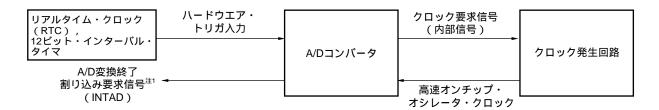

| 第11章  | A/Dコンバータ                                | 324  |

|       |                                         | 00.5 |

|       | 1 A/Dコンバータの機能                           |      |

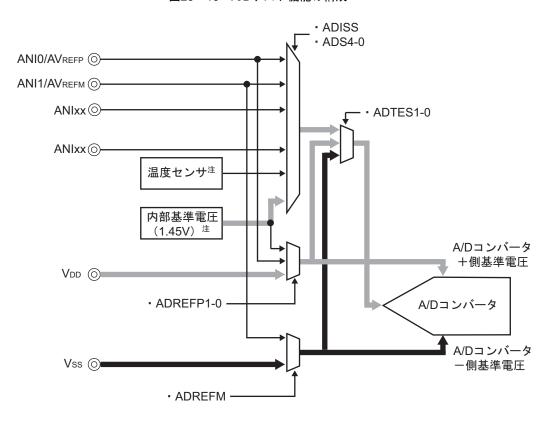

|       | 2 A/Dコンバータの構成                           |      |

| 11. 3 | 3 A/Dコンバータを制御するレジスタ                     |      |

|       | 11.3.1 周辺イネーブル・レジスタ0 (PERO)             |      |

|       | 11. 3. 2 A/Dコンバータ・モード・レジスタ0 (ADM0)      |      |

|       | 11. 3. 3 A/Dコンバータ・モード・レジスタ1 (ADM1)      |      |

|       | 11. 3. 4 A/Dコンバータ・モード・レジスタ2(ADM2)       | 341  |

| 11. 3      | 3.5 10ビットA/D変換結果レジスタ(ADCR)                            | 343  |

|------------|-------------------------------------------------------|------|

| 11. 3      | B. 6 8ビットA/D変換結果レジスタ(ADCRH)                           | 343  |

| 11. 3      | 3.7 アナログ入力チャネル指定レジスタ(ADS)                             | 344  |

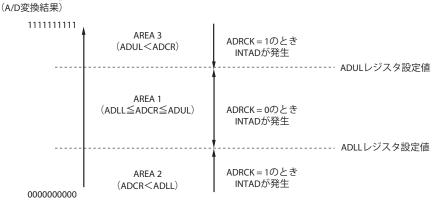

| 11. 3      | 3. 8 変換結果比較上限値設定レジスタ(ADUL)                            | 346  |

| 11. 3      | 3. 9 変換結果比較下限値設定レジスタ(ADLL)                            | 346  |

| 11. 3      | 3. 10 A/Dテスト・レジスタ(ADTES)                              | 347  |

|            | 3. 11 アナログ入力端子のポート機能を制御するレジスタ                         |      |

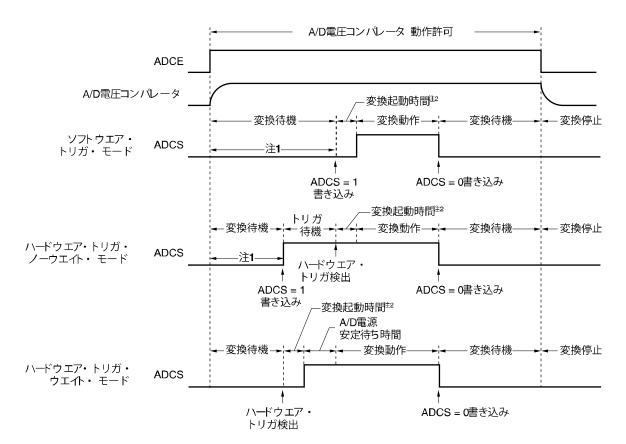

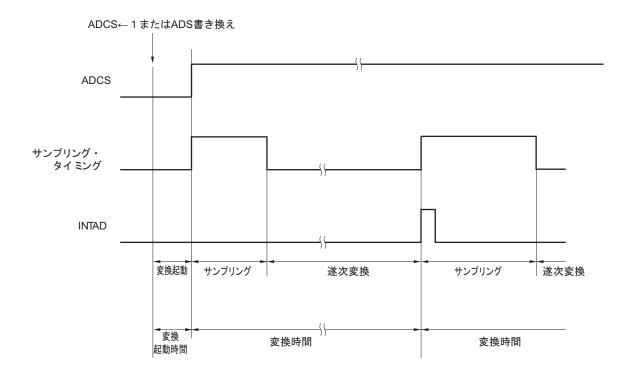

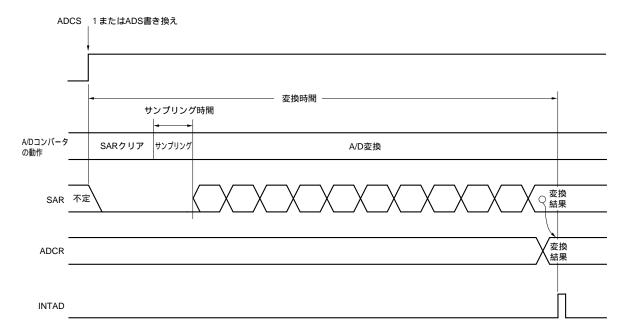

|            | )コンバータの変換動作                                           |      |

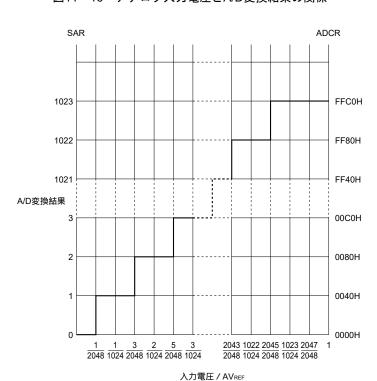

|            | 力電圧と変換結果                                              |      |

|            |                                                       |      |

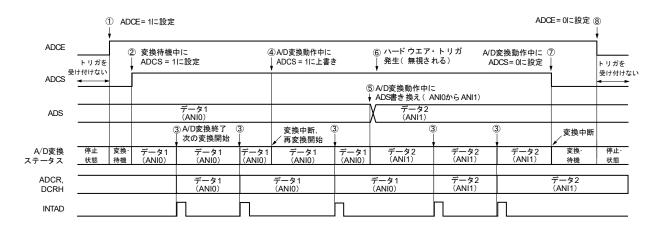

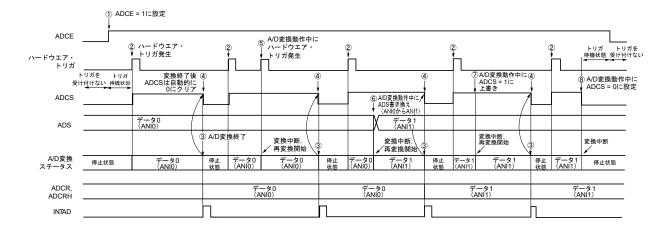

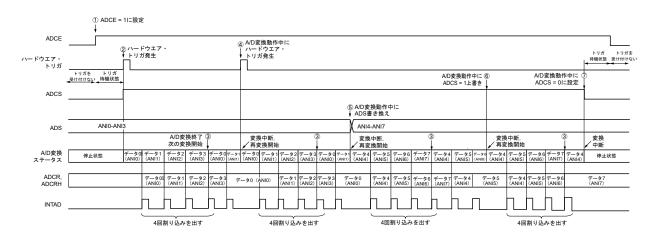

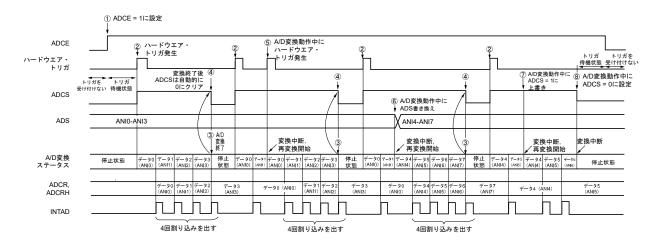

|            | 3.1 ソフトウエア・トリガ・モード(セレクト・モード,連続変換モード)                  |      |

|            | S.2 ソフトウエア・トリガ・モード                                    |      |

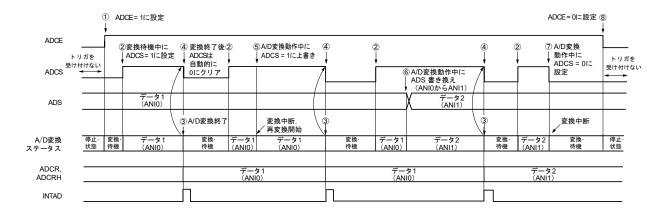

|            | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                  | 353  |

| 11 6       | S.3 ソフトウエア・トリガ・モード(スキャン・モード,連続変換モード)                  |      |

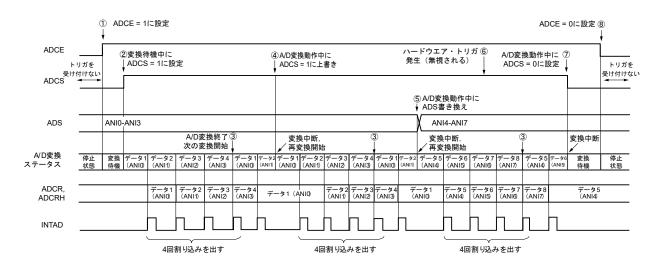

|            | 5.4 ソフトウエア・トリガ・モード                                    |      |

| 11. 0      | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                  | 355  |

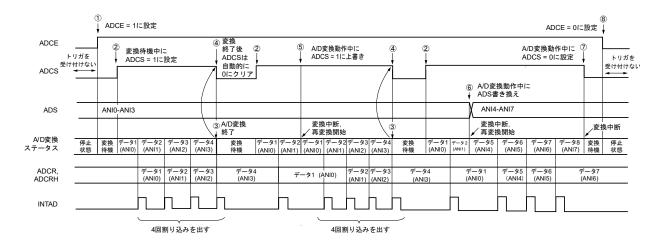

| 11 6       | · · · · · · · · · · · · · · · · · · ·                 |      |

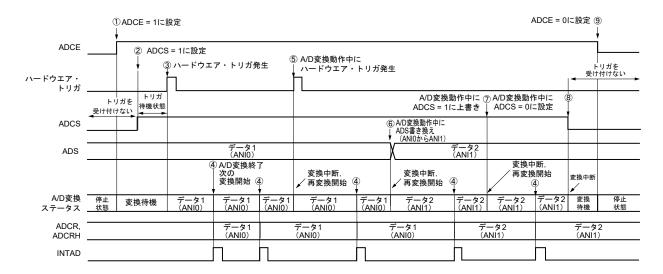

| 11. 0      | ハン・・・・ / ー / ・                                        | 356  |

| 11 6       | 、                                                     |      |

| 11.0       | パン・パープエグ イッパ グープエイイ ピーイ<br>(セレクト・モード,ワンショット変換モード)     | 357  |

| 11 6       | 、                                                     |      |

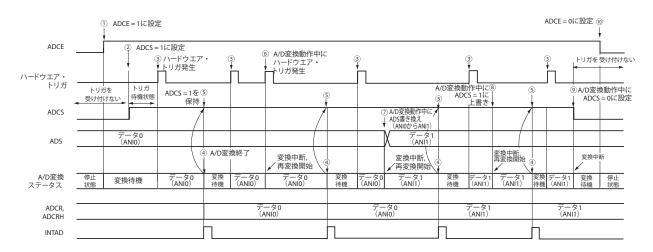

| 11.0       | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                  | 358  |

| 11 6       | 5.8 ハードウエア・トリガ・ノーウエイト・モード                             |      |

| 11.0       | スキャン・モード,ワンショット変換モード)                                 | 350  |

| 11 6       | (ハードウェア・トリガ・ウエイト・モード                                  |      |

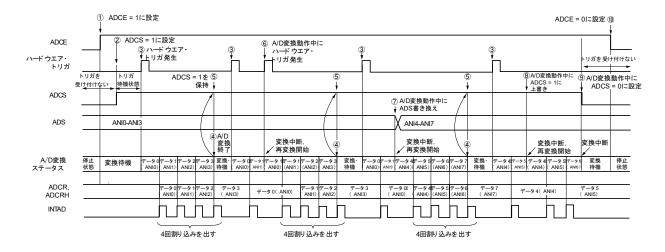

| 11. 0      | 、                                                     | 360  |

| 11 6       | (ピレノド・ピード、産机友族 ピード/                                   | 500  |

| 11. 0      | ). 10 ハートウエア・トリカ・ウエイト・モート<br>(セレクト・モード,ワンショット変換モード)   | 261  |

| 11 6       | - (ピレグド・モード, ブンショッド変換モード)<br>6.11 ハードウエア・トリガ・ウエイト・モード | 30 1 |

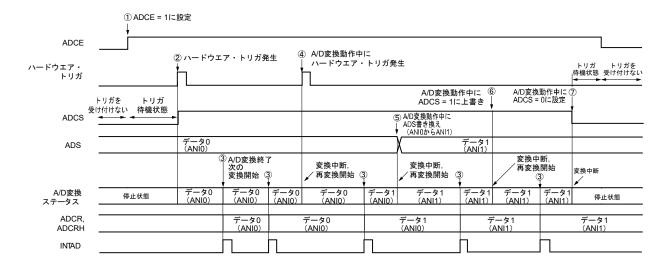

| 11. 0      |                                                       | 262  |

| 11 6       | - (ヘキャン・モート, 達械変換モート)                                 | 302  |

| 11. 0      | 5.12 ハートウエア・トリカ・ウエイト・モート<br>(スキャン・モード,ワンショット変換モード)    | 262  |

| 44 7 1/5   |                                                       |      |

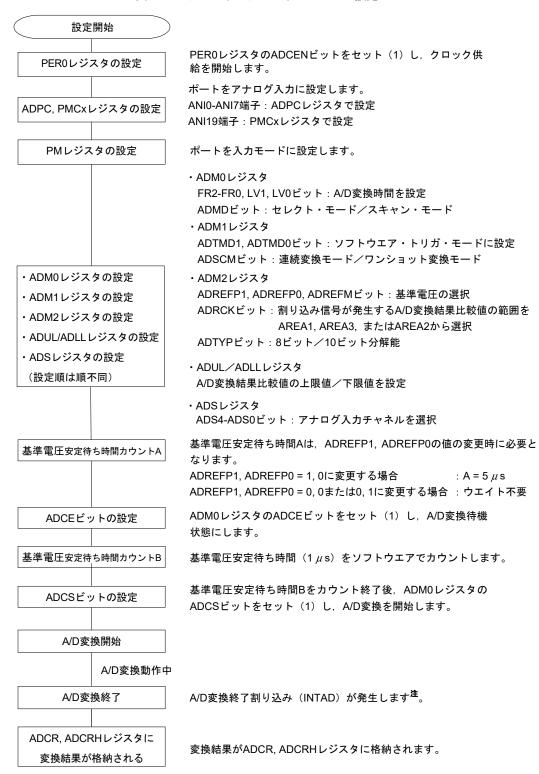

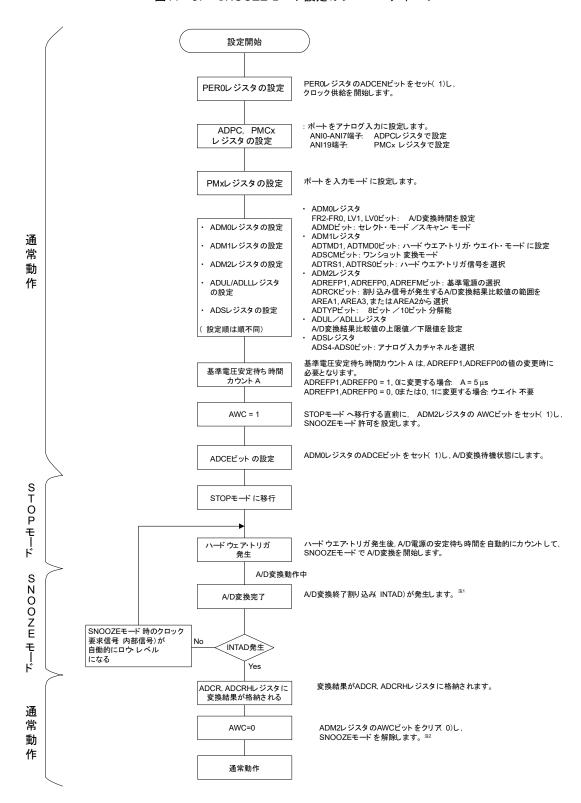

|            | )コンバータの設定フロー・チャート                                     |      |

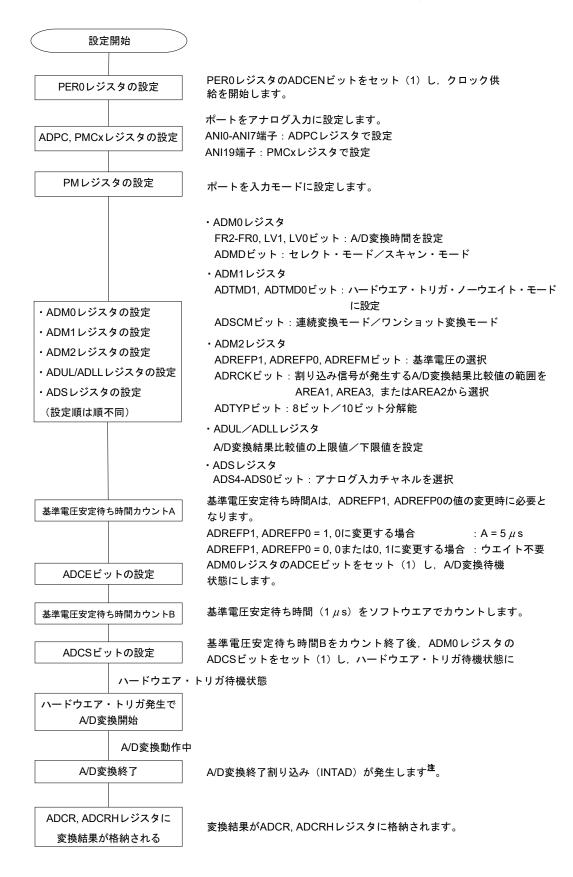

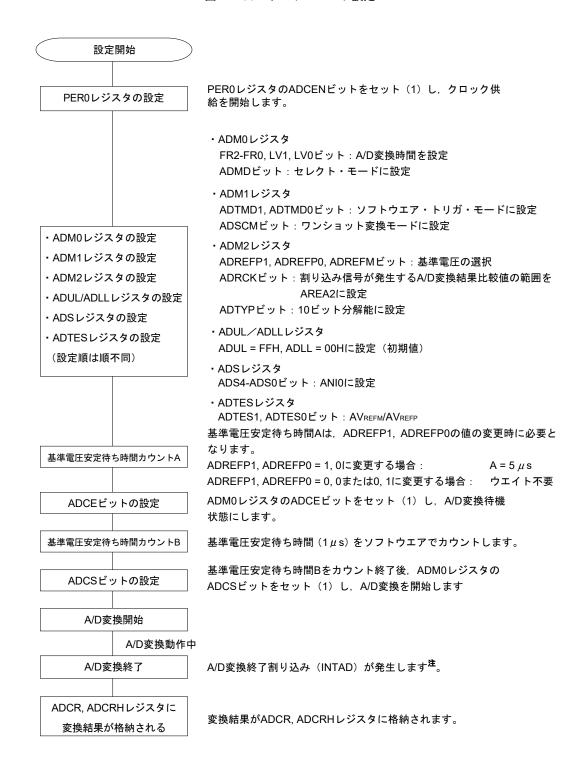

|            | 7. 1 ソフトウエア・トリガ・モード設定                                 |      |

|            |                                                       |      |

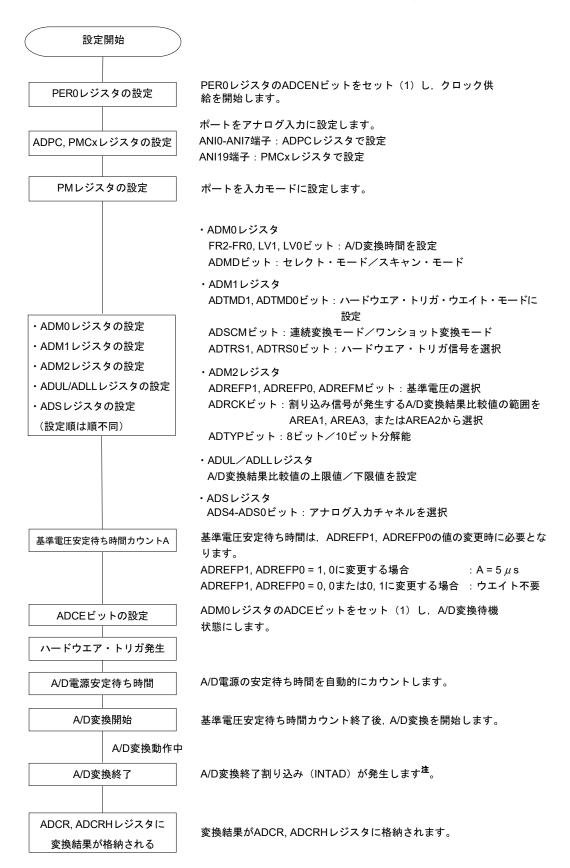

|            | 7.3 ハードウエア・トリガ・ウエイト・モード設定                             | 366  |

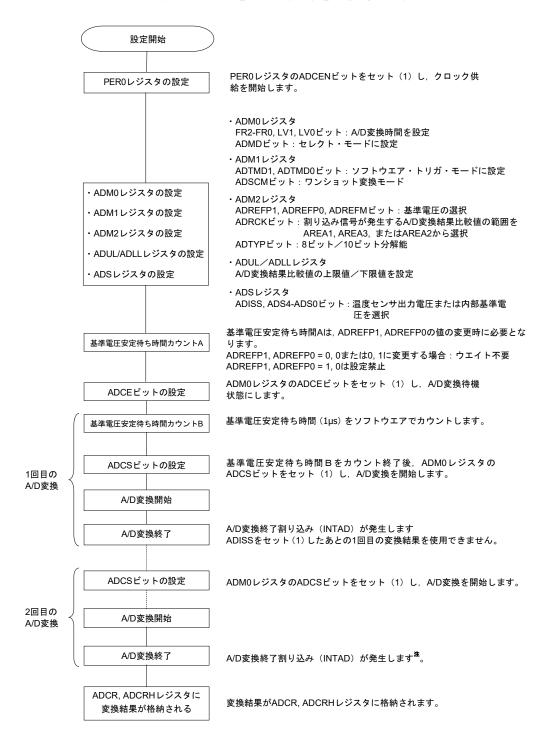

| 11. /      | 7.4 温度センサ出力電圧/内部基準電圧を選択時の設定                           |      |

| 44 -       | (例 ソフトウエア・トリガ・モード,ワンショット変換モード時)<br>*                  |      |

|            | 7.5 テスト・モード設定                                         |      |

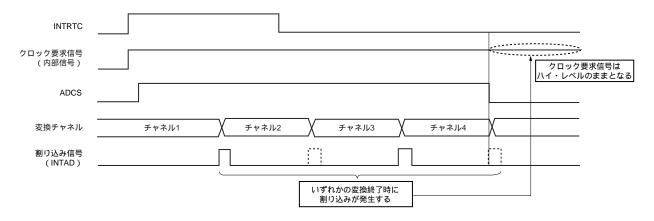

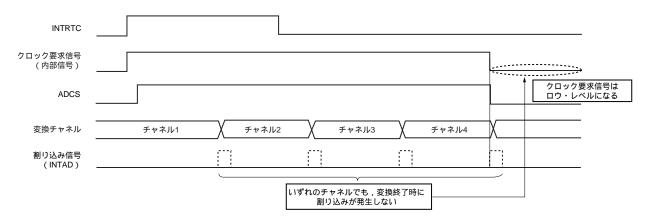

|            | OOZEモード機能                                             |      |

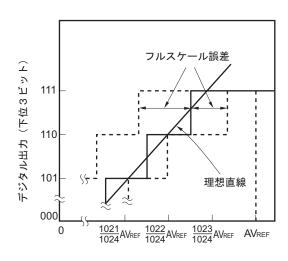

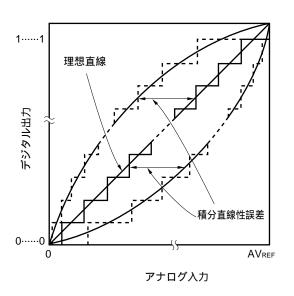

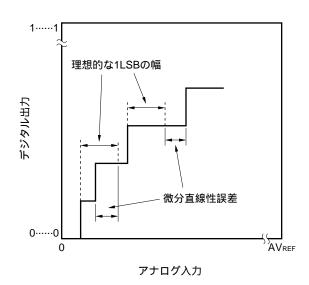

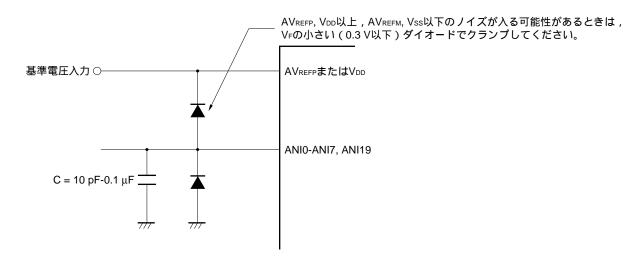

|            | )コンバータ特性表の読み方                                         |      |

| 11. 10 A/  | /Dコンバータの注意事項                                          | 376  |

| <b>然40</b> | 1 <b>-</b> 11 -1 - 1                                  | 000  |

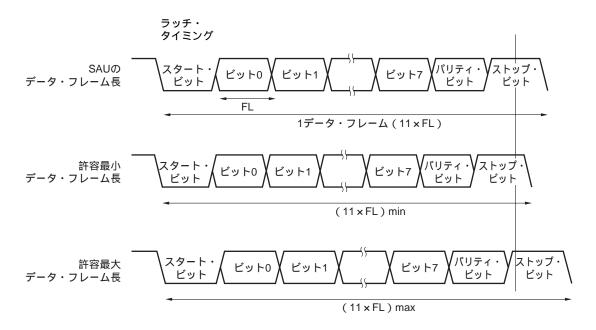

| 第12草 ン!    | Jアル・アレイ・ユニット                                          | 380  |

|            |                                                       |      |

|            | Jアル・アレイ・ユニットの機能                                       |      |

|            | I. 1 簡易SPI(CSI00, CSI01)                              |      |

|            | I. 2 UART (UART0)                                     |      |

|            | I. 3 簡易I <sup>2</sup> C(IIC00, IIC01)                 |      |

|            | Jアル・アレイ・ユニットの構成                                       |      |

|            | 2.1 シフト・レジスタ                                          |      |

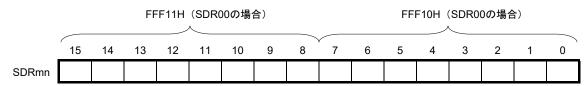

| 12. 2      | 2. 2 シリアル・データ・レジスタmn(SDRmn)の下位8/9ビット                  | 387  |

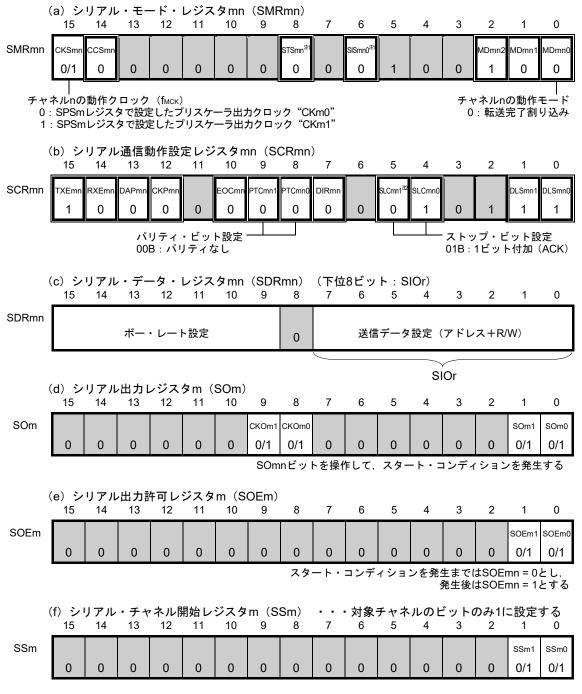

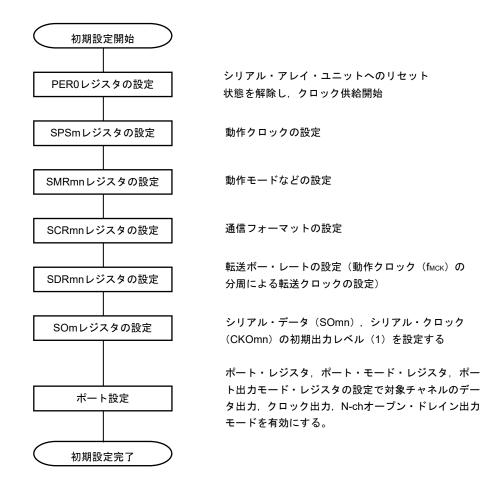

| 12. 3 | シリアル・アレイ・ユニットを制御するレジスタ                                      | 389 |

|-------|-------------------------------------------------------------|-----|

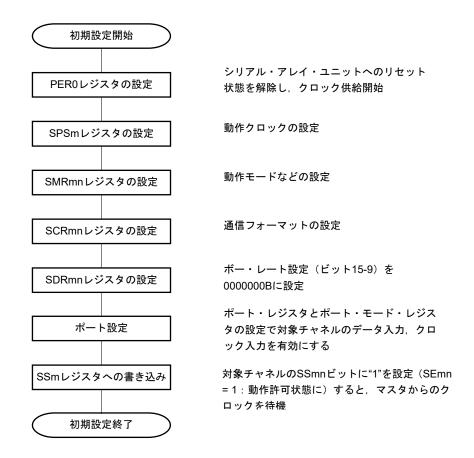

|       | 12. 3. 1 周辺イネーブル・レジスタ0(PER0)                                | 390 |

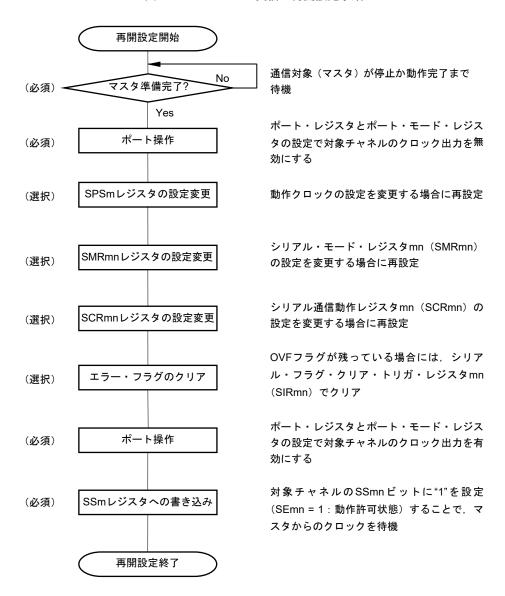

|       | 12. 3. 2 シリアル・クロック選択レジスタm(SPSm)                             | 391 |

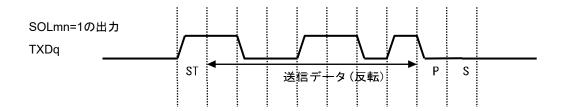

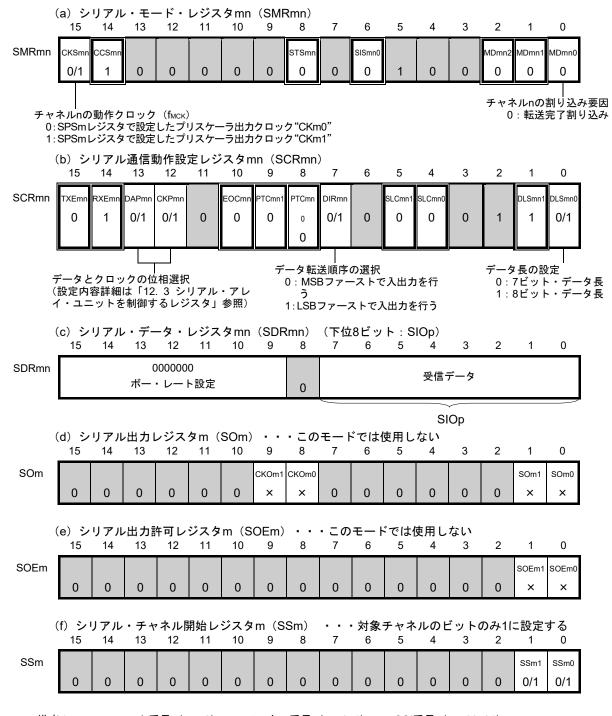

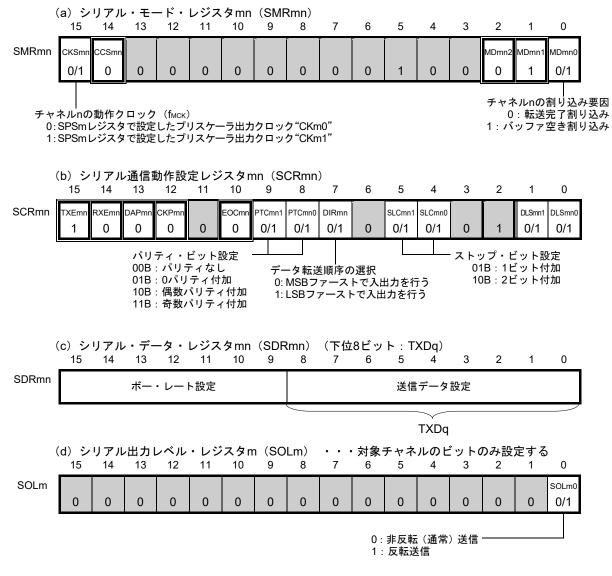

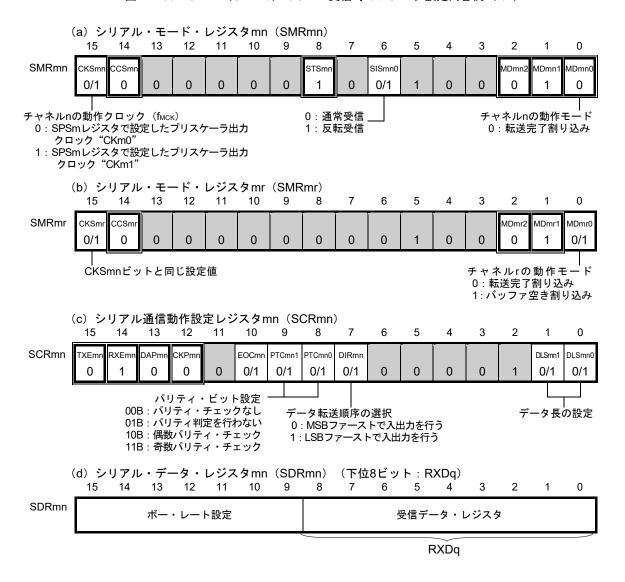

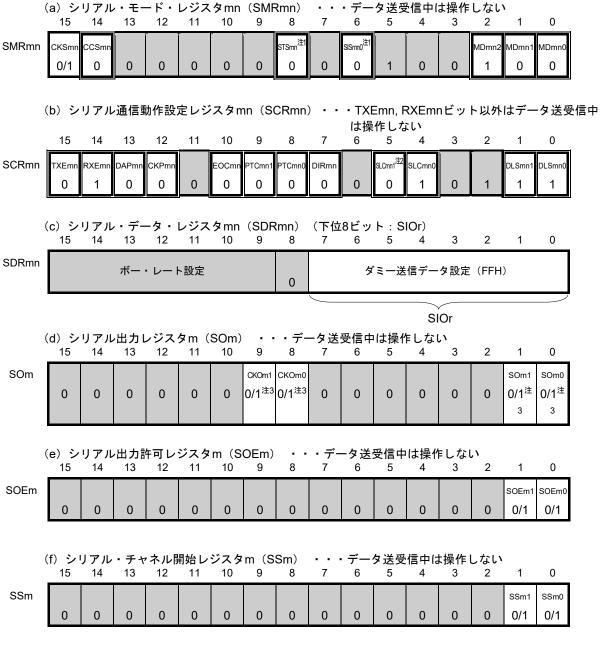

|       | 12. 3. 3 シリアル・モード・レジスタmn (SMRmn)                            | 392 |

|       | 12. 3. 4 シリアル通信動作設定レジスタmn(SCRmn)                            | 393 |

|       | 12. 3. 5 シリアル・データ・レジスタmn(SDRmn)                             | 396 |

|       | 12. 3. 6 シリアル・フラグ・クリア・トリガ・レジスタmn (SIRmn)                    | 397 |

|       | 12. 3. 7 シリアル・ステータス・レジスタmn (SSRmn)                          | 398 |

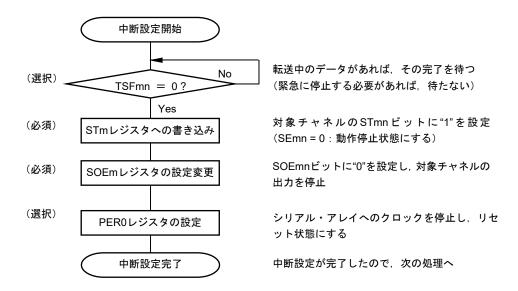

|       | 12. 3. 8 シリアル・チャネル開始レジスタm(SSm)                              | 400 |

|       | 12. 3. 9 シリアル・チャネル停止レジスタm(STm)                              | 401 |

|       | 12. 3. 10 シリアル・チャネル許可ステータス・レジスタm(SEm)                       | 402 |

|       | 12. 3. 11 シリアル出力許可レジスタm(SOEm)                               | 403 |

|       | 12. 3. 12 シリアル出力レジスタm(SOm)                                  | 404 |

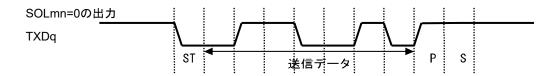

|       | 12. 3. 13 シリアル出力レベル・レジスタm(SOLm)                             | 405 |

|       | 12. 3. 14 シリアル・スタンバイ・コントロール・レジスタm(SSCm)                     | 407 |

|       | 12. 3. 15 ノイズ・フィルタ許可レジスタ0(NFENO)                            |     |

|       | 12.3.16 シリアル入出力端子のポート機能を制御するレジスタ                            | 409 |

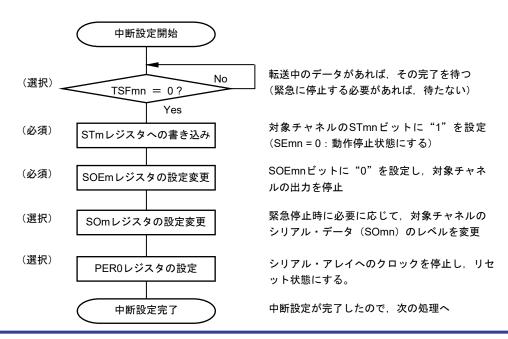

| 12. 4 | 動作停止モード                                                     |     |

|       |                                                             | 410 |

|       | 12.4.2 チャネルごとに動作停止とする場合                                     |     |

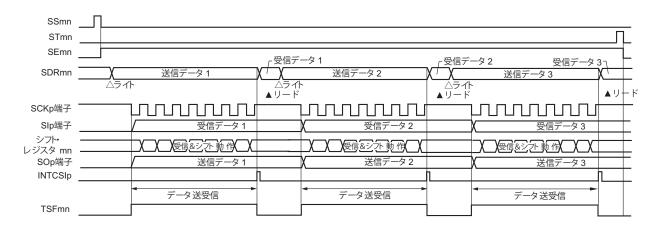

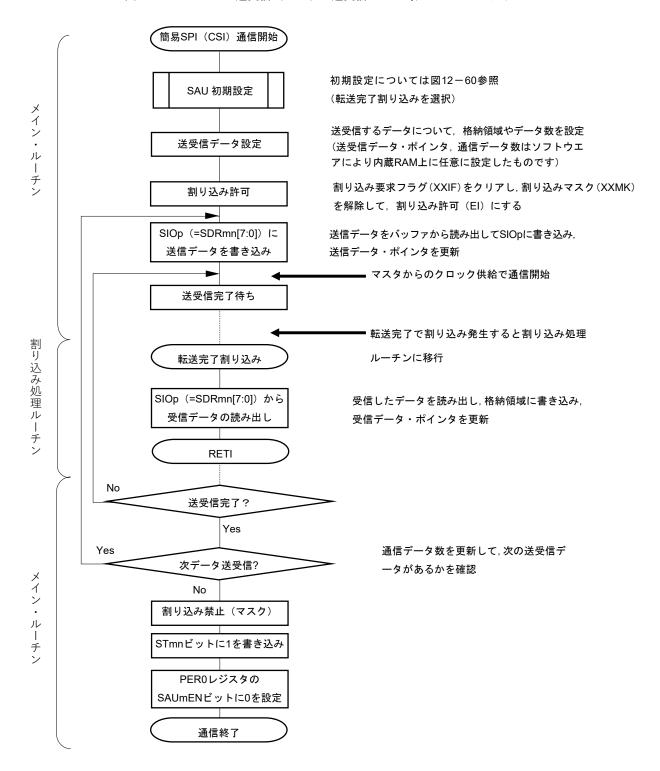

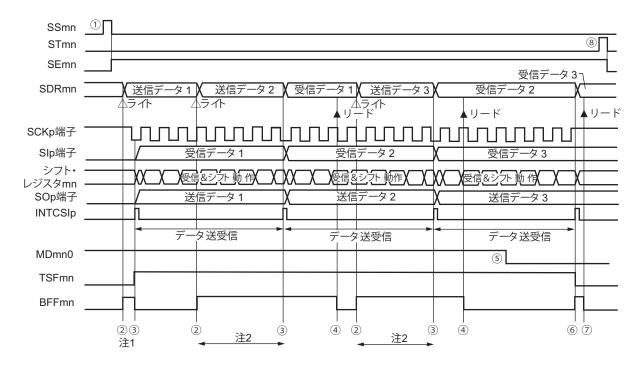

| 12. 5 | 簡易SPI(CSI00, CSI01)通信の動作                                    |     |

| 0     | 12. 5. 1 マスタ送信                                              |     |

|       | 12. 5. 2 マスタ受信                                              |     |

|       | 12.5.3 マスタ送受信                                               |     |

|       | 12. 5. 4 スレーブ送信                                             |     |

|       | 12. 5. 5 スレーブ受信                                             |     |

|       | 12. 5. 6 スレーブ送受信                                            |     |

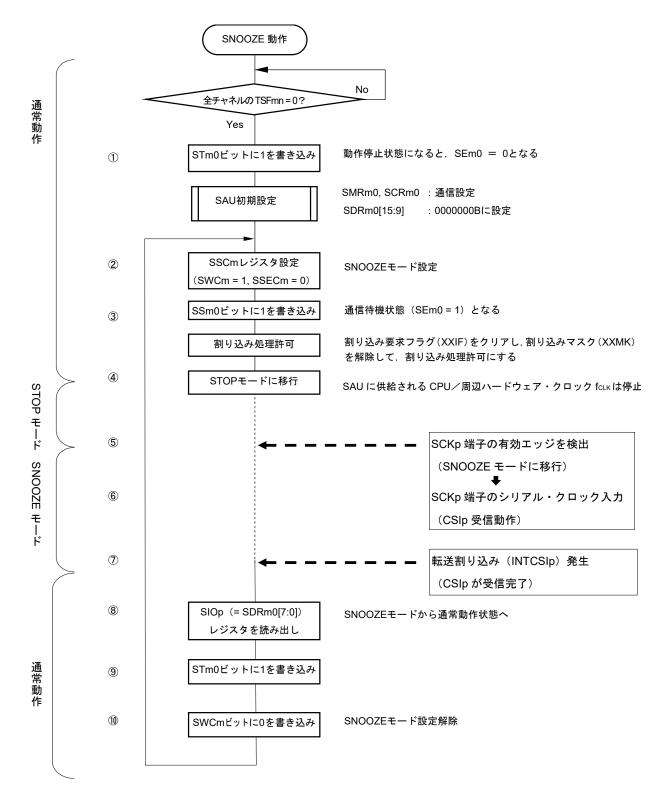

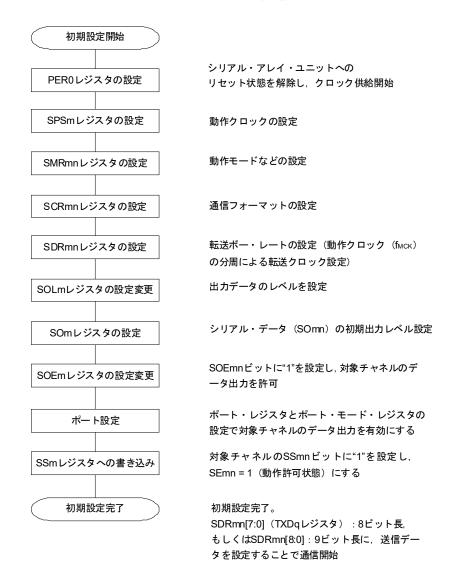

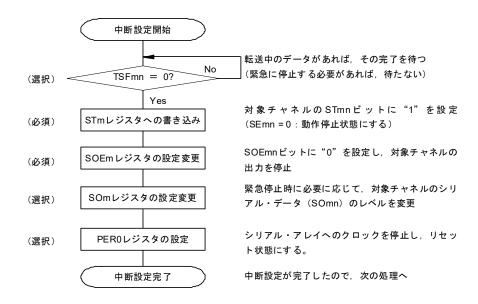

|       | 12. 5. 7 SNOOZEモード機能                                        |     |

|       | 12. 5. 8 転送クロック周波数の算出                                       |     |

|       | 12. 5. 9 簡易SPI (CSI00, CSI01) 通信時におけるエラー発生時の処理手順            |     |

| 12. 6 | UART(UARTO)通信の動作                                            |     |

| 0     | 12. 6. 1 UART送信                                             |     |

|       | 12. 6. 2 UART受信                                             |     |

|       | 12. 6. 3 ボー・レートの算出                                          |     |

|       | 12. 6. 4 UART (UARTO) 通信時におけるエラー発生時の処理手順                    |     |

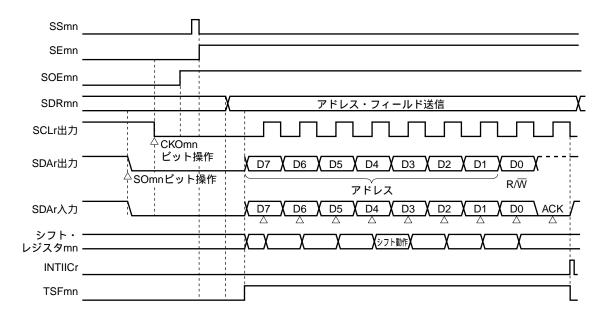

| 12 7  | 簡易I <sup>2</sup> C(IIC00, IIC01)通信の動作                       |     |

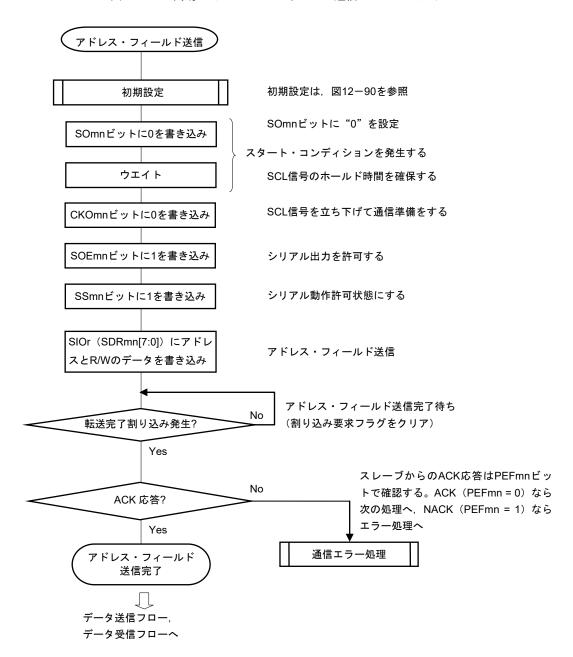

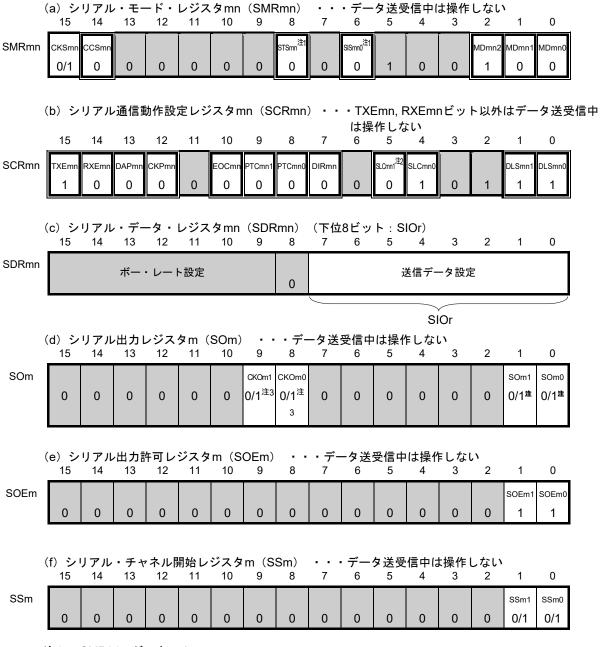

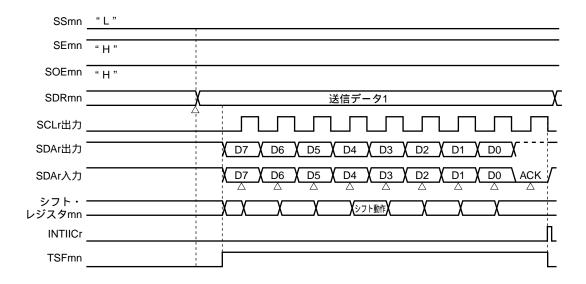

|       | 12. 7. 1 アドレス・フィールド送信                                       |     |

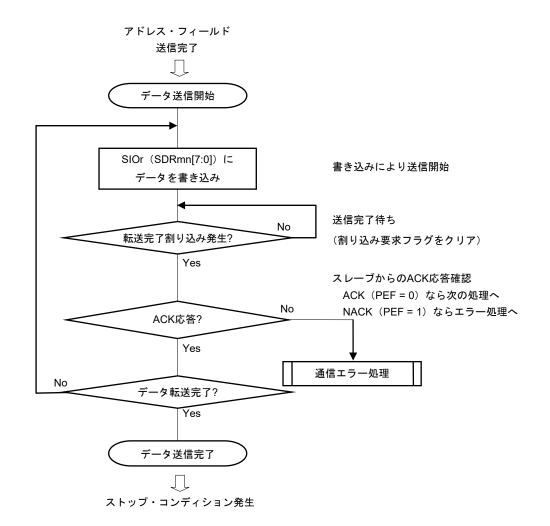

|       | 12.7.2 データ送信                                                |     |

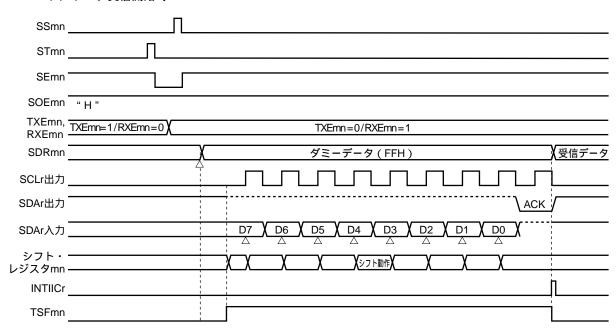

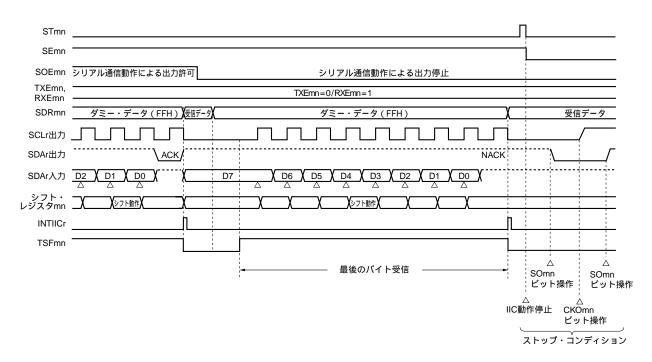

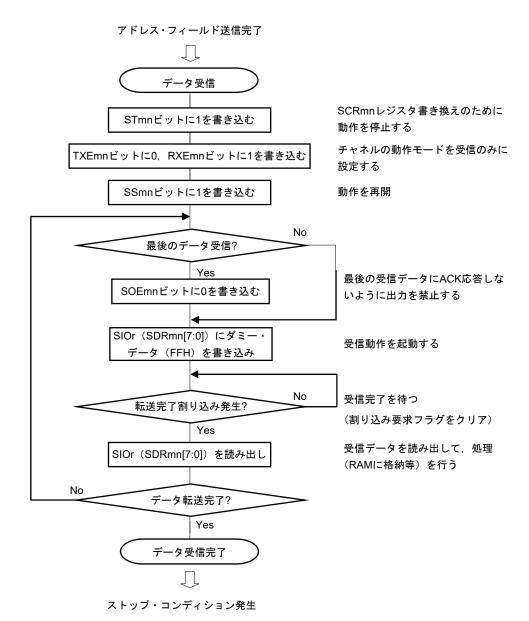

|       | 12.7.3 データ受信                                                |     |

|       | 12. 7. 4 ストップ・コンディション発生                                     |     |

|       | 12. 7. 5 転送レートの算出                                           |     |

|       | 12.7.6 簡易I <sup>2</sup> C (IIC00, IIC01) 通信時におけるエラー発生時の処理手順 |     |

|       |                                                             |     |

| 第13章  | シリアル・インタフェースIICA                                            | 509 |

|       |                                                             |     |

|       | シリアル・インタフェースIICAの機能                                         |     |

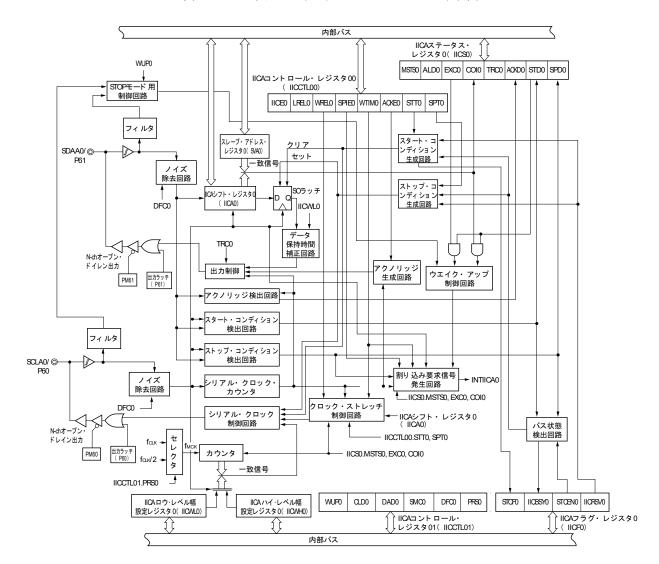

|       | シリアル・インタフェースIICAの構成                                         |     |

| 13. 3 | シリアル・インタフェースIICAを制御するレジスタ                                   |     |

|       | 13. 3. 1 周辺イネーブル・レジスタ0(PERO)                                |     |

|       | 13. 3. 2 IICAコントロール・レジスタ00 (IICCTL00)                       |     |

|       | 13. 3. 3 IICAステータス・レジスタ0 (IICS0)                            |     |

|       | 13. 3. 4 IICAフラグ・レジスタ0 (IICF0)                              | 523 |

|       | 13. 3. 5                                       | IICAコントロール・レジスタ01(IICCTL01)                                                                                                                  | 525                      |

|-------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|       | 13. 3. 6                                       | IICAロウ・レベル幅設定レジスタ0(IICWL0)                                                                                                                   | 527                      |

|       | 13. 3. 7                                       | IICAハイ・レベル幅設定レジスタ0(IICWH0)                                                                                                                   | 527                      |

|       | 13. 3. 8                                       | ポート・モード・レジスタ6(PM6)                                                                                                                           | 528                      |

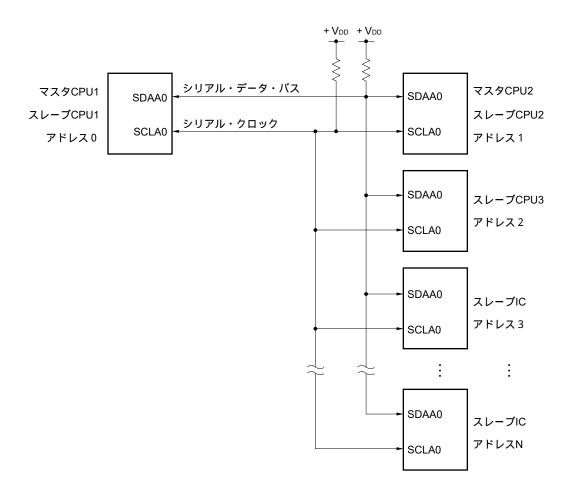

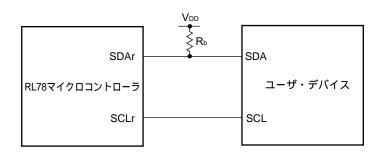

| 13. 4 | I I <sup>2</sup> Cバス                           | ・モードの機能                                                                                                                                      | 529                      |

|       | 13. 4. 1                                       | 端子構成                                                                                                                                         |                          |

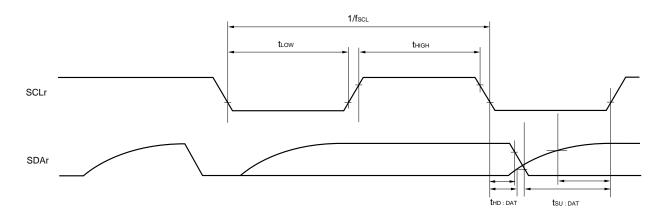

|       | -                                              | IICWL0, IICWH0レジスタによる転送クロック設定方法                                                                                                              |                          |

| 13 5  |                                                | の定義および制御方法                                                                                                                                   |                          |

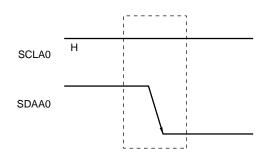

| 10. 0 | 13. 5. 1                                       | スタート・コンディション                                                                                                                                 |                          |

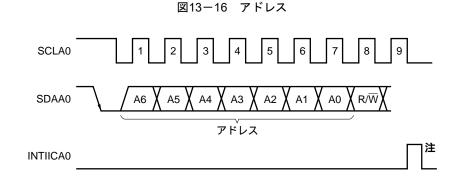

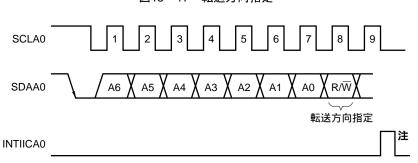

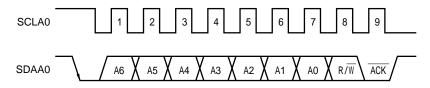

|       |                                                | アドレス                                                                                                                                         |                          |

|       | 13. 5. 2                                       | 対                                                                                                                                            |                          |

|       | 13. 5. 3                                       | #AGC/J Phi 1                                                                                                                                 |                          |

|       |                                                |                                                                                                                                              |                          |

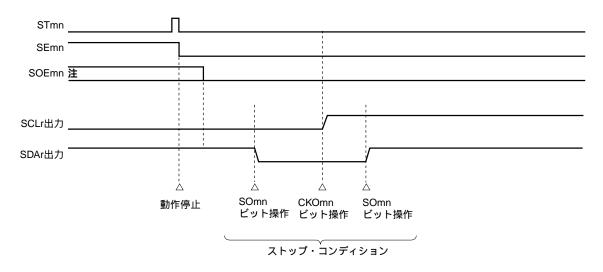

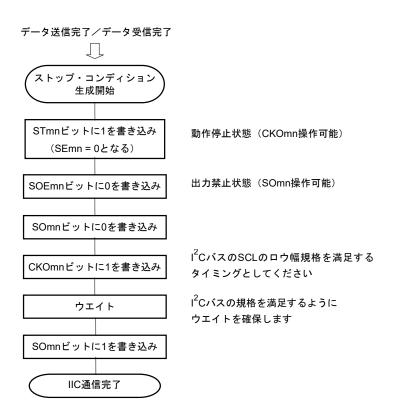

|       | 13. 5. 5                                       | ストップ・コンディション                                                                                                                                 |                          |

|       |                                                | クロック・ストレッチ                                                                                                                                   |                          |

|       | 13. 5. 7                                       | クロック・ストレッチ解除方法                                                                                                                               |                          |

|       | 13. 5. 8                                       | 割り込み要求(INTIICAO)発生タイミングおよびクロック・ストレッチ制御                                                                                                       |                          |

|       | 13. 5. 9                                       | アドレスの一致検出方法                                                                                                                                  |                          |

|       | 13. 5. 10                                      | • • • • • • • • • • • • • • • • • • • •                                                                                                      |                          |

|       | 13. 5. 11                                      | 拡張コード                                                                                                                                        | 541                      |

|       | 13. 5. 12                                      | アービトレーション                                                                                                                                    | 542                      |

|       | 13. 5. 13                                      | ウエイク・アップ機能                                                                                                                                   | 544                      |

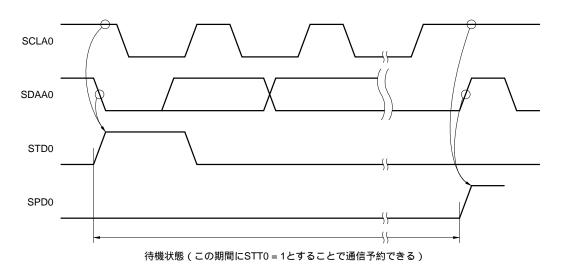

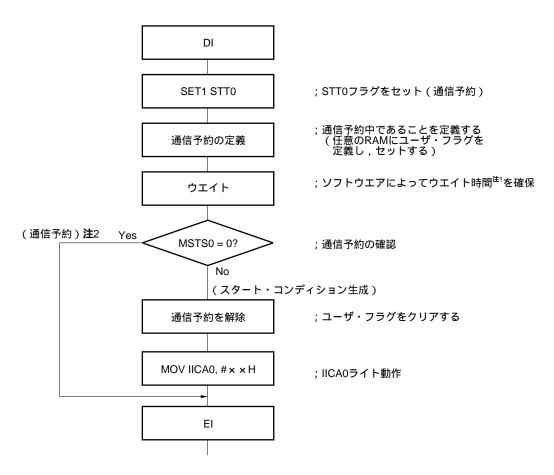

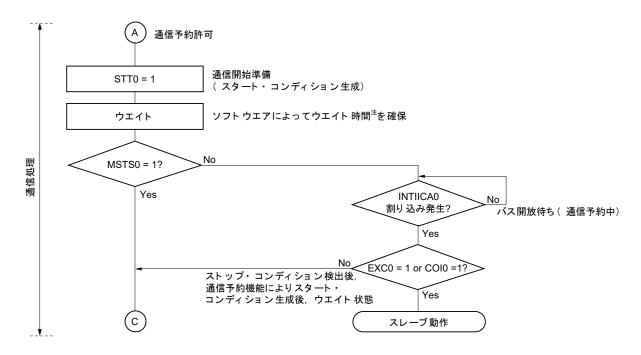

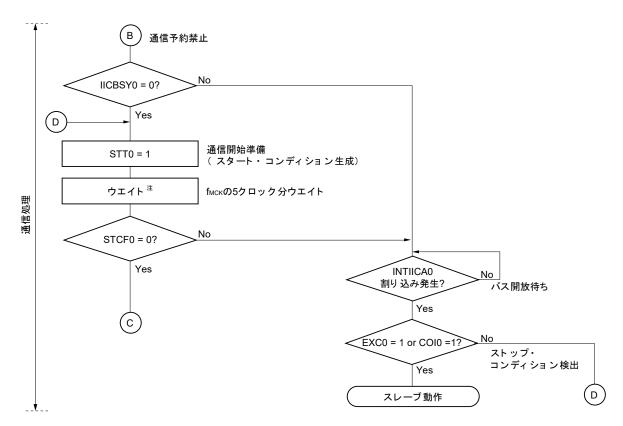

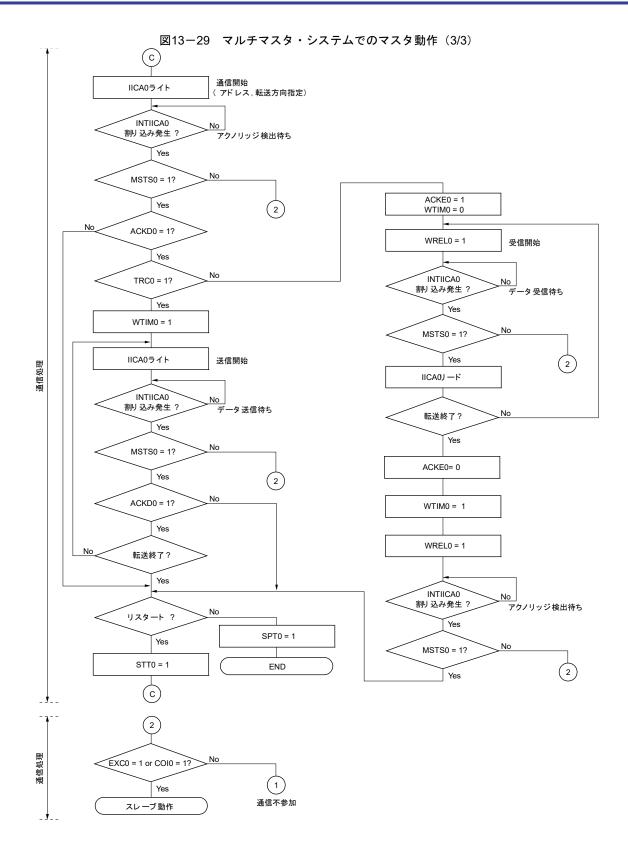

|       | 13. 5. 14                                      | 通信予約                                                                                                                                         | 547                      |

|       | 13. 5. 15                                      | その他の注意事項                                                                                                                                     | 551                      |

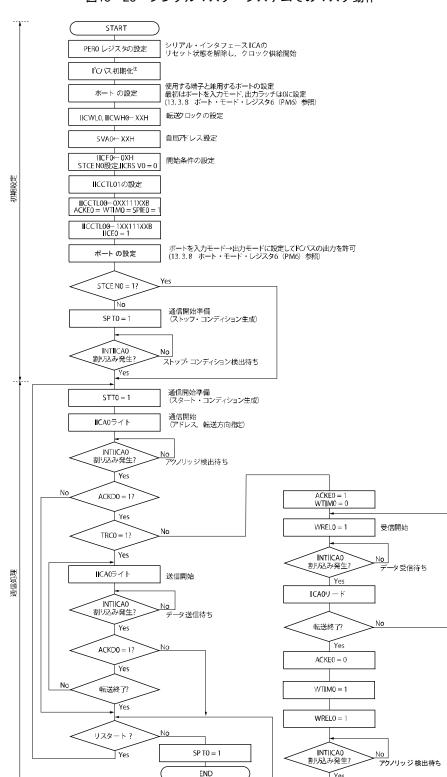

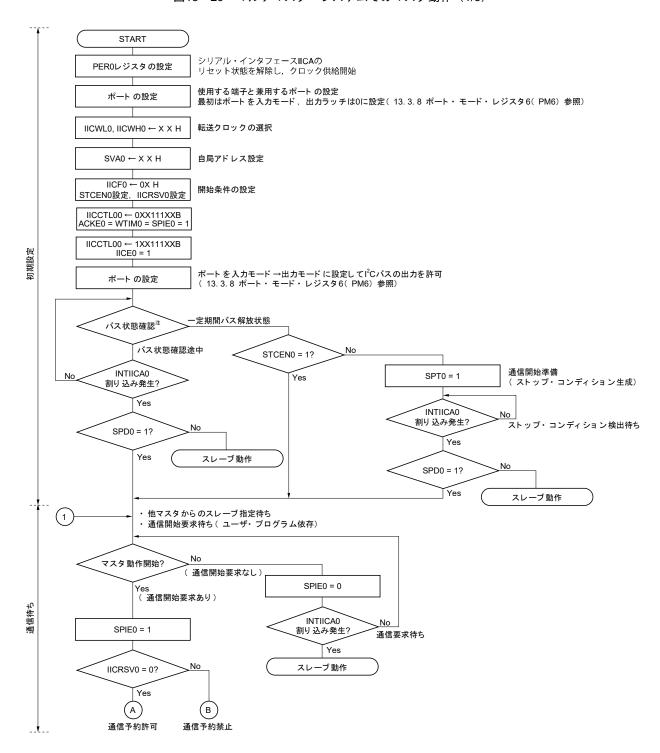

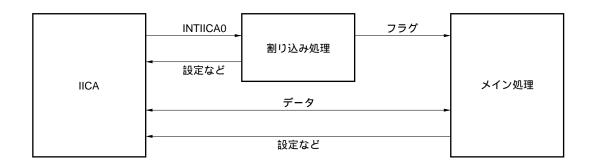

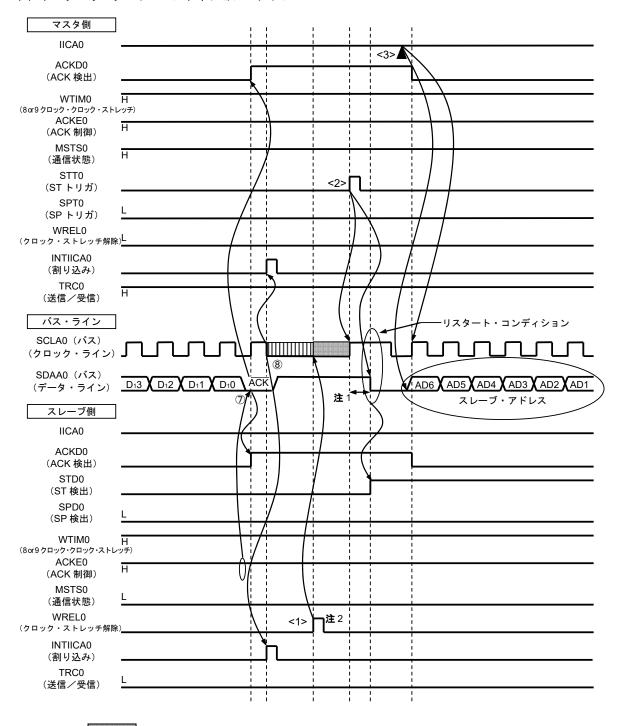

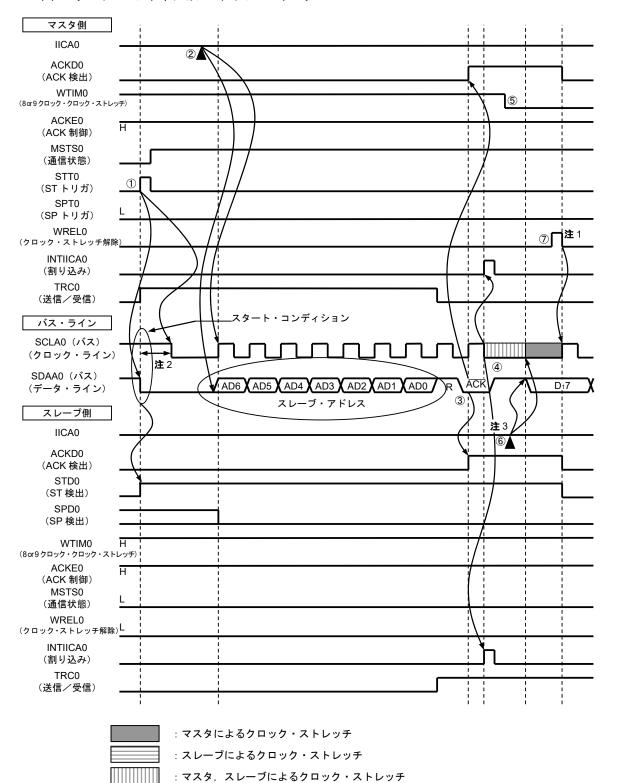

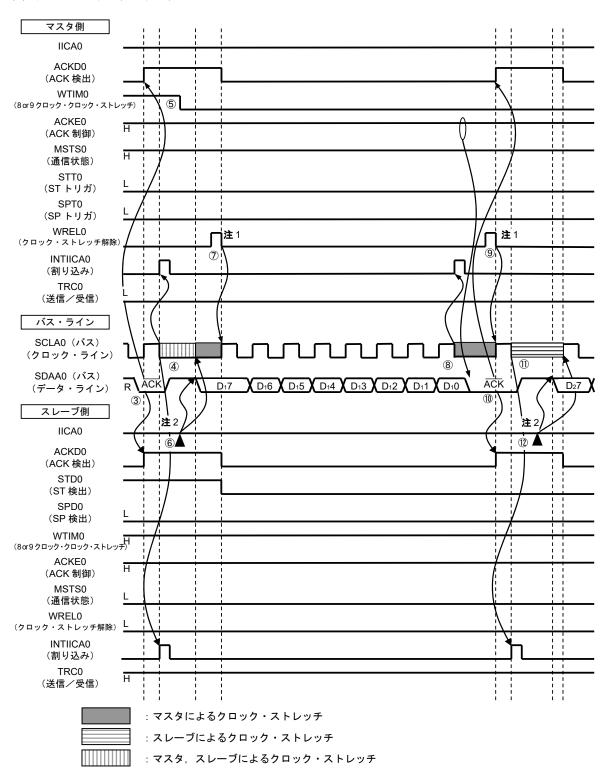

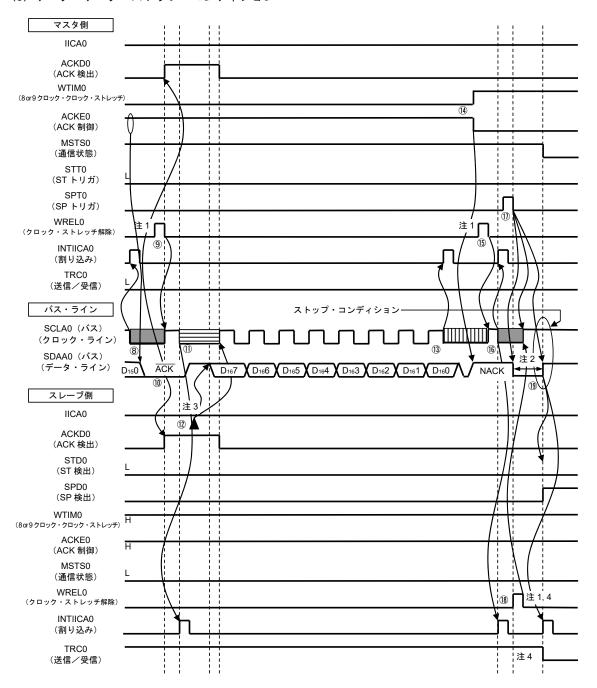

|       | 13. 5. 16                                      | 通信動作                                                                                                                                         | 552                      |

|       | 13. 5. 17                                      | I <sup>2</sup> C割り込み要求(INTIICAO)の発生タイミング                                                                                                     |                          |

| 13. 6 |                                                | ング・チャート                                                                                                                                      |                          |

| 第14章  | USB2.0                                         | Oホスト/ファンクション・モジュール(USB)                                                                                                                      | 596                      |

| 14. 1 | USB2.0                                         | ホスト/ファンクション・モジュールの機能                                                                                                                         | 596                      |

| 14. 2 | 2 USB2.0                                       | ホスト/ファンクション・モジュールの構成                                                                                                                         | 598                      |

| 14. 3 | 3 USB2.0                                       | ホスト/ファンクション・モジュールで使用するレジスタの説明                                                                                                                | 601                      |

|       | 14. 3. 1                                       | システム・コンフィグレーション・コントロール・レジスタ(SYSCFG)                                                                                                          |                          |

|       |                                                | システム・コンフィグレーション・コントロール・レジスタ1(SYSCFG1)                                                                                                        | 605                      |

|       | 14. 3. 2                                       | システム・コンフィグレーション・ステータス・レジスタn                                                                                                                  |                          |

|       |                                                | (SYSSTSn) (n = 0, 1)                                                                                                                         | 608                      |

|       | 14 3 3                                         | デバイス・ステート・コントロール・レジスタn(DVSTCTRn)(n = 0, 1)                                                                                                   |                          |

|       |                                                | DMAn-FIFOピン・コンフィグレーション・レジスタ                                                                                                                  |                          |

|       | 14. 0. 4                                       | (DMAnPCFG) (n = 0, 1)                                                                                                                        | 615                      |

|       | 1/ 2 5                                         | CFIFOポート・レジスタ(CFIFOM)                                                                                                                        | 013                      |

|       | 14. 3. 3                                       | DnFIFOポート・レジスタ(DnFIFOM)(n = 0, 1)                                                                                                            | 616                      |

|       | 11 2 6                                         | DMA転送用DnFIFOポート・レジスタ(DnFIFO)(n = 0, 1)                                                                                                       |                          |

|       | 14. 3. 0                                       | DMA転送用DIIFIFO小一下・レジスタ(DIIFIFO)(II = 0, 1)                                                                                                    | 010                      |

|       | 4407                                           |                                                                                                                                              |                          |

|       | 14. 3. 7                                       | CFIFOポート選択レジスタ(CFIFOSEL)                                                                                                                     |                          |

|       |                                                | DnFIFOポート選択レジスタ(DnFIFOSEL)(n = 0, 1)                                                                                                         | 619                      |

|       |                                                | DnFIFOポート選択レジスタ(DnFIFOSEL)(n = 0, 1)<br>CFIFOポート・コントロール・レジスタ(CFIFOCTR)                                                                       |                          |

|       | 14. 3. 8                                       | DnFIFOポート選択レジスタ(DnFIFOSEL)(n = 0, 1)                                                                                                         | 623                      |

|       | 14. 3. 8<br>14. 3. 9                           | DnFIFOポート選択レジスタ(DnFIFOSEL)(n = 0, 1)                                                                                                         | 623<br>627               |

|       | 14. 3. 8<br>14. 3. 9                           | DnFIFOポート選択レジスタ(DnFIFOSEL)(n = 0, 1)                                                                                                         | 623<br>627               |

|       | 14. 3. 8<br>14. 3. 9<br>14. 3. 10              | DnFIFOポート選択レジスタ(DnFIFOSEL)(n = 0, 1)                                                                                                         | 623<br>627<br>629        |

|       | 14. 3. 8<br>14. 3. 9<br>14. 3. 10<br>14. 3. 11 | DnFIFOポート選択レジスタ(DnFIFOSEL)(n = 0, 1)<br>CFIFOポート・コントロール・レジスタ(CFIFOCTR)<br>DnFIFOポート・コントロール・レジスタ(DnFIFOCTR)(n = 0, 1)<br>割り込み許可レジスタ0(INTENB0) | 623<br>627<br>629<br>632 |

| 14. 3. 1 | 4 SOF出力コンフィグレーション・レジスタ(SOFCFG)         | 634                      |

|----------|----------------------------------------|--------------------------|

| 14. 3. 1 | 5 割り込みステータス・レジスタO(INTSTSO)             | 635                      |

| 14. 3. 1 | 3 割り込みステータス・レジスタn (INTSTSn) (n = 1, 2) | 639                      |

| 14. 3. 1 |                                        |                          |

| 14. 3. 1 |                                        |                          |

| 14. 3. 1 |                                        |                          |

| 14. 3. 2 |                                        |                          |

| 14. 3. 2 |                                        |                          |

| 14. 3. 2 |                                        |                          |

| 14. 3. 2 |                                        |                          |

| 14. 3. 2 |                                        |                          |

| 14. 3. 2 |                                        |                          |

| 14. 3. 2 |                                        |                          |

| 14. 3. 2 |                                        |                          |

| 14. 3. 2 |                                        |                          |

| 14. 3. 2 |                                        |                          |

| 14. 3. 3 |                                        |                          |

| 14. 3. 3 |                                        |                          |

| 14. 3. 3 |                                        |                          |

| 14. 3. 3 |                                        |                          |

| 14. 3. 3 |                                        |                          |

| 14. 3. 3 | (n = 4, 5)                             |                          |

| 14. 3. 3 |                                        |                          |

| 14. 3. 3 |                                        |                          |

| 14. 3. 3 |                                        |                          |

|          | B USBモジュール制御レジスタ(USBMC)                |                          |

|          | 9 デバイス・アドレスnコンフィグレーション・レジスタ(DEVADDn)   | 00-                      |

| 11.0.0   | (n = 0~5)                              | 685                      |

| 14 4 動作説 | 明                                      |                          |

|          | システム制御                                 |                          |

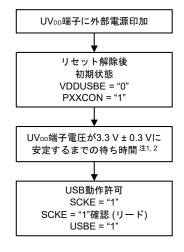

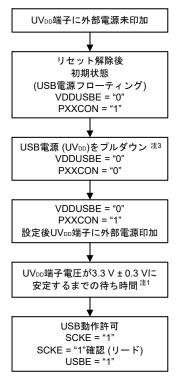

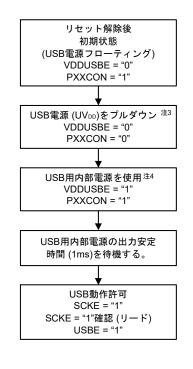

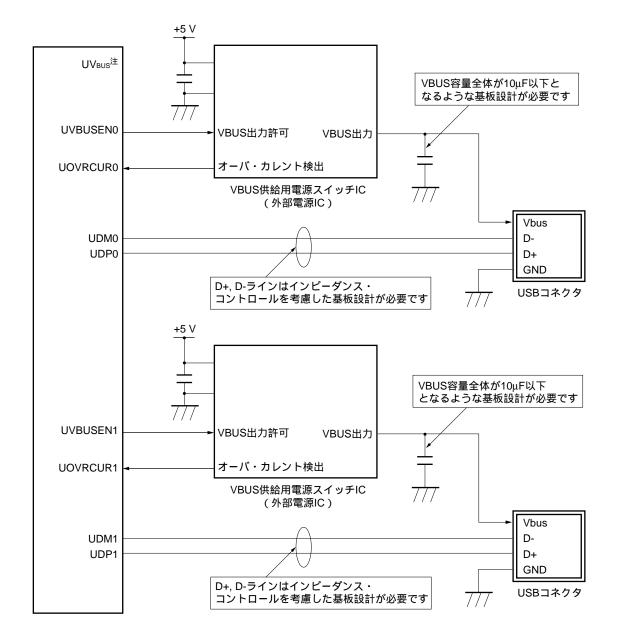

|          | 14. 4. 1. 1   動作開始                     |                          |

|          | 14. 4. 1. 2 コントローラ機能の選択設定              |                          |

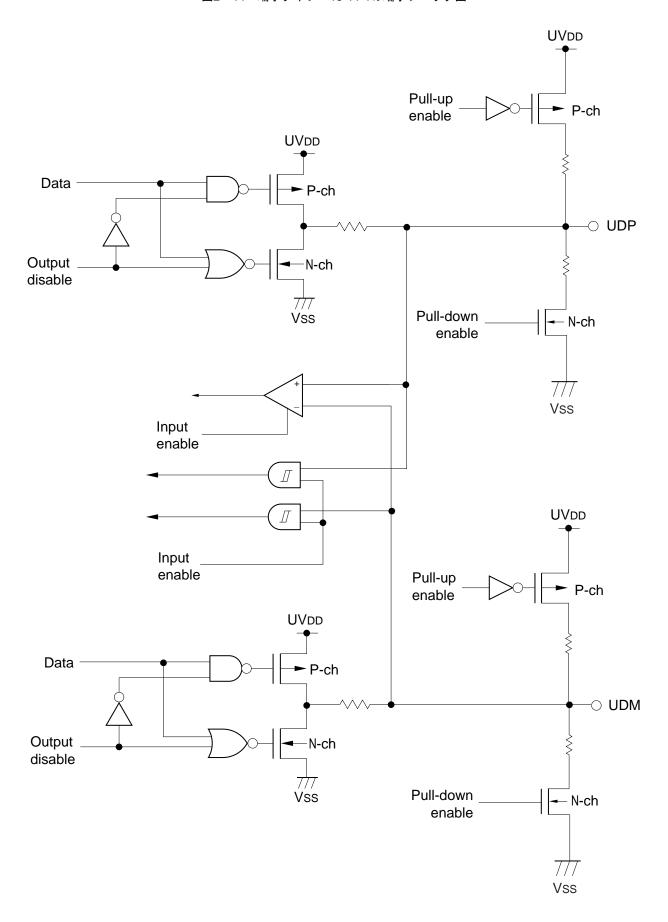

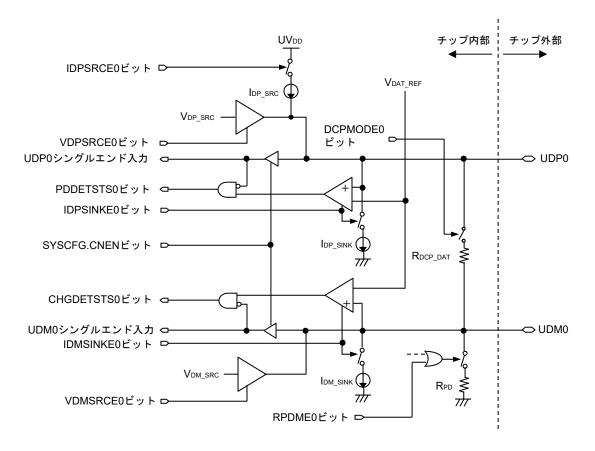

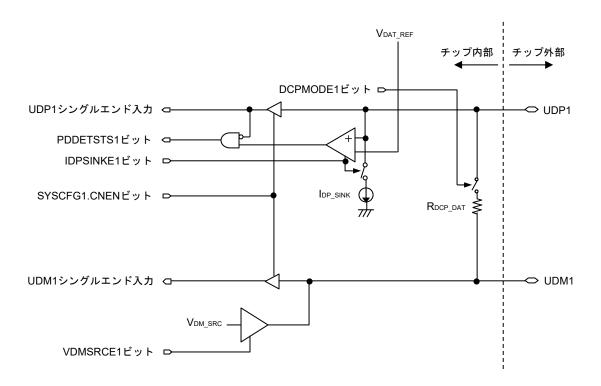

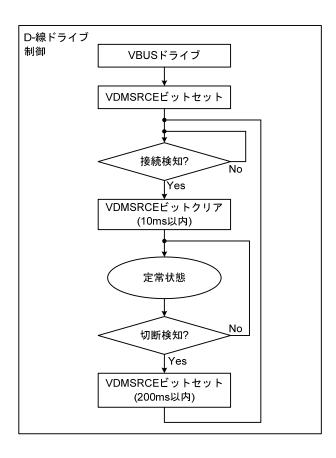

|          | - 14. 4. 1. 3 USBデータ・バス抵抗制御            |                          |

|          | 割り込み要因                                 |                          |

|          | 割り込みの説明                                |                          |

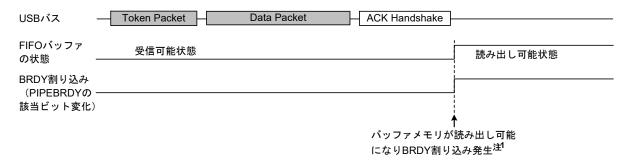

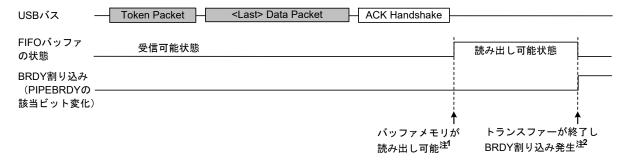

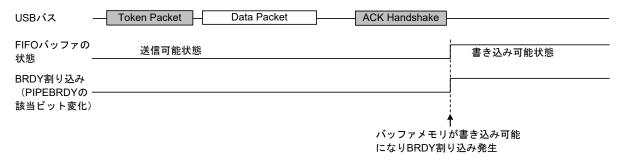

|          | 14. 4. 3. 1 BRDY割り込み                   |                          |

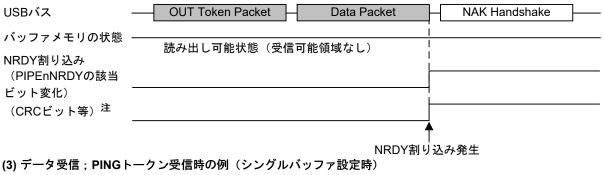

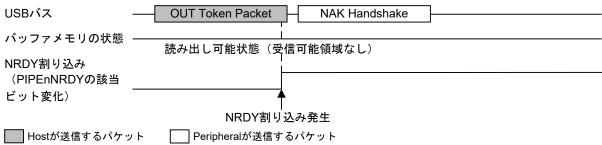

|          | 14.4.3.2 NRDY割り込み                      |                          |

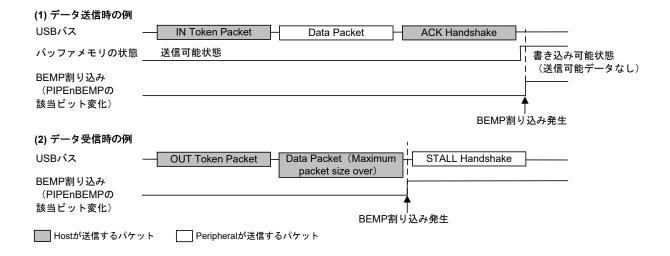

|          | 14. 4. 3. 3 BEMP割り込み                   |                          |

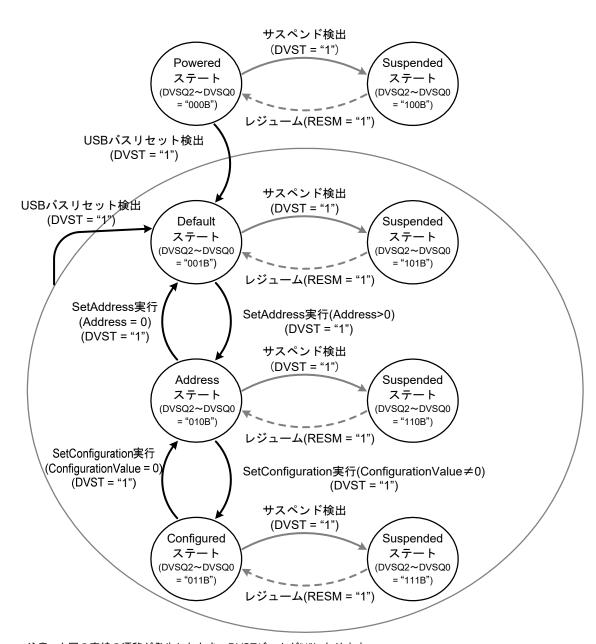

|          | 14.4.3.4 デバイス・ステート遷移割り込み               |                          |

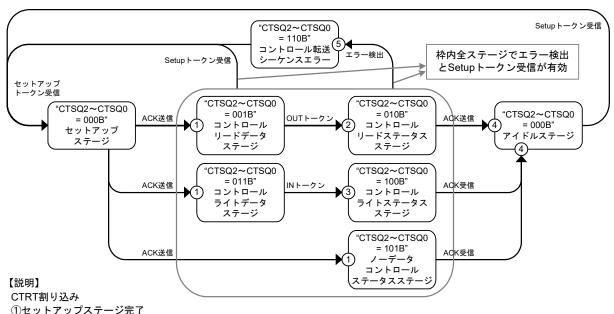

|          | 14. 4. 3. 5 コントロール転送ステージ遷移割り込み         |                          |

|          | 14.4.3.6 フレーム番号更新割り込み                  |                          |

|          | 14. 4. 3. 7 VBUS割り込み                   |                          |

|          | 14.4.3.8 レジューム割り込み                     |                          |

|          | 14.4.3.9 オーバカレント変化割り込み                 |                          |

|          | 14. 4. 3. 10 バス変化割り込み                  |                          |

|          | 14.4.3.10 ハス変化剖り込み                     |                          |

|          | i 寸、寸、ひ、 i ! - ししし ツI型IT大 山 ロリン メンタア   | 1 00                     |

|          |                                        |                          |

|          | 14.4.3.12 セットアップ・トランザクション正常応答割り込み      | 708                      |

|          | 14. 4. 3. 12 セットアップ・トランザクション正常応答割り込み   | 708<br>708               |

|          | 14.4.3.12 セットアップ・トランザクション正常応答割り込み      | 708<br>708<br>709        |

|          | 14. 4. 3. 12 セットアップ・トランザクション正常応答割り込み   | 708<br>708<br>709<br>709 |

|       | 14. 4. 4 パイプ・コントロール                      | 710 |

|-------|------------------------------------------|-----|

|       | 14.4.4.1 パイプ・コントロール・レジスタの切り替え手順          |     |

|       | 14. 4. 4. 2 転送タイプ                        |     |

|       | 14. 4. 4. 3 エンド・ポイント番号                   |     |

|       | 14. 4. 4. 4 マックス・パケット・サイズ設定              |     |

|       | 14. 4. 4. 5 トランザクション・カウンタ(パイプ4, 5読み出し方向) |     |

|       | 14. 4. 4. 6 応答PID                        |     |

|       | 14. 4. 4. 7 データPIDシーケンス・ビット              |     |

|       | 14. 4. 4. 8 応答PID = NAK機能                | 714 |

|       | 14. 4. 4. 9 自動応答モード                      |     |

|       | 14. 4. 4. 10 OUT-NAKモード                  |     |

|       | 14. 4. 4. 11 Null自動応答モード                 | 715 |

|       | 14. 4. 5 FIFOバッファ・メモリ                    | 716 |

|       | 14. 4. 5. 1 FIFOバッファ・メモリ                 | 716 |

|       | 14. 4. 5. 2 FIFOポートの機能                   | 718 |

|       | 14. 4. 5. 3 DMA転送(D0FIFO/D1FIFOポート)      | 719 |

|       | 14.4.6 コントロール転送(DCP)                     | 720 |

|       | 14. 4. 6. 1 ホスト・コントローラ機能選択時のコントロール転送     | 720 |

|       | 14. 4. 6. 2 ファンクション・コントローラ機能選択時のコントロール転送 | 721 |

|       | 14. 4. 7 バルク転送(パイプ4, 5)                  | 722 |

|       | 14.4.8 インタラプト転送(パイプ6,7)                  | 723 |

|       | 14. 4. 8. 1 ホスト・コントローラ機能選択時のインタラプト転送時の   |     |

|       | インターバル・カウンタ                              | 723 |

|       | 14. 4. 9 SOF補間機能                         | 724 |

|       | 14. 4. 10 パイプ・スケジュール                     | 725 |

|       | 14. 4. 10. 1 トランザクション発行条件                | 725 |

|       | 14. 4. 10. 2 転送スケジュール                    | 725 |

|       | 14. 4. 10. 3 USB通信許可                     | 725 |

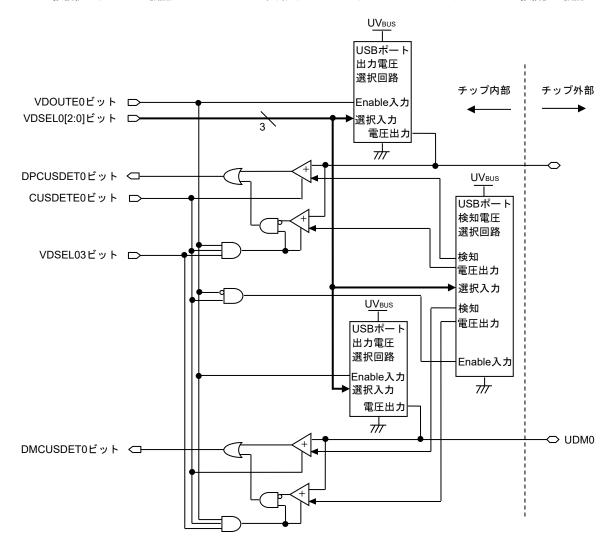

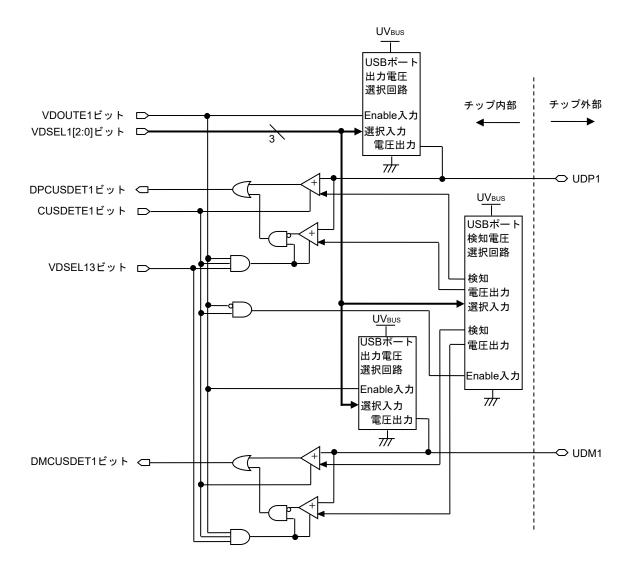

|       | 14. 4. 11 Battery Charging接続検知制御         | 726 |

|       | 14. 4. 12 Battery Charging接続検知オプション機能機能  | 728 |

|       | 14. 4. 13 Battery Charging検知処理           | 731 |

|       | 14. 4. 13. 1 ファンクション・コントローラ時の処理          | 731 |

|       | 14. 4. 13. 2 ホスト・コントローラ時の処理              | 733 |

|       |                                          |     |

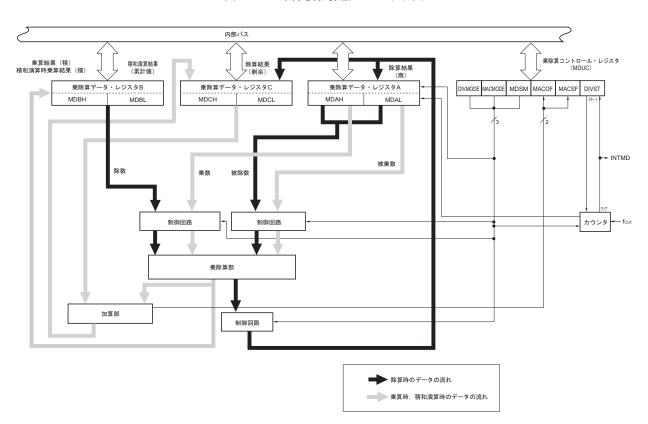

| 第15章  | 乗除積和算器                                   | 736 |

|       |                                          |     |

| 15. 1 | 乗除積和算器の機能                                | 736 |

| 15. 2 | 乗除積和算器の構成                                |     |

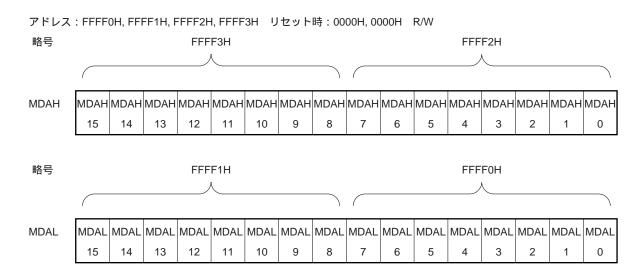

|       | 15. 2. 1 乗除算データ・レジスタA(MDAH, MDAL)        | 738 |

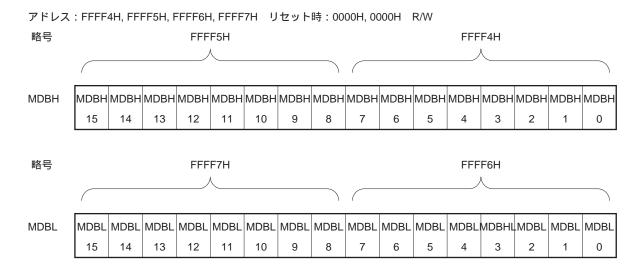

|       | 15. 2. 2 乗除算データ・レジスタB(MDBL, MDBH)        | 739 |

|       | 15. 2. 3 乗除算データ・レジスタC(MDCL, MDCH)        | 740 |

| 15. 3 | 乗除積和算器を制御するレジスタ                          | 742 |

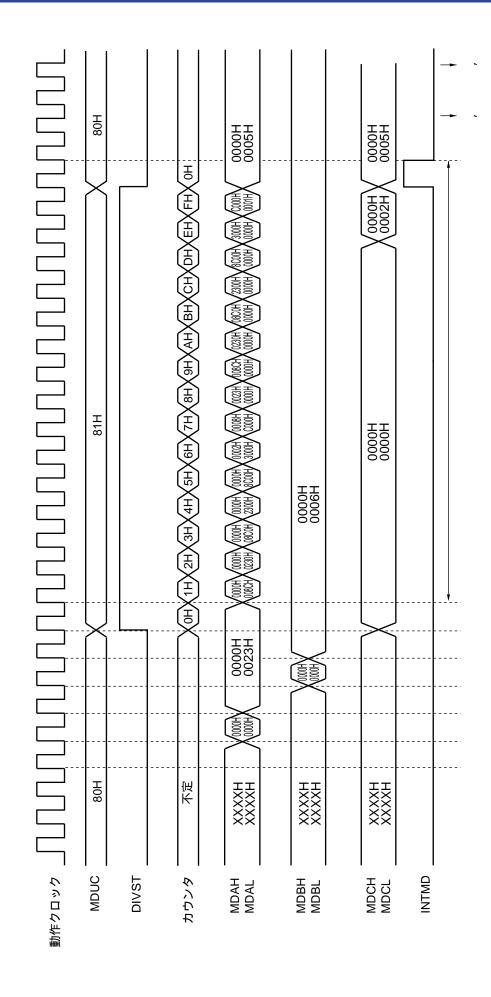

|       | 15. 3. 1 乗除算コントロール・レジスタ0(MDUC)           | 742 |

| 15. 4 | 乗除積和算器の動作                                |     |

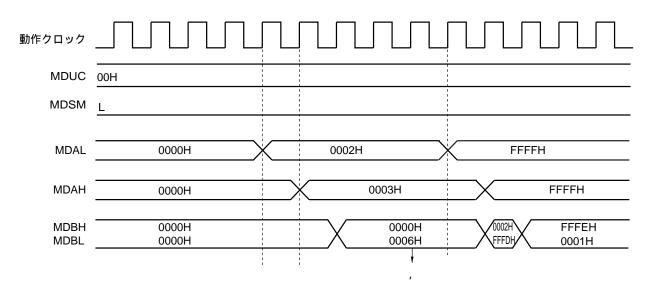

|       | 15. 4. 1 乗算(符号なし)動作                      | 744 |

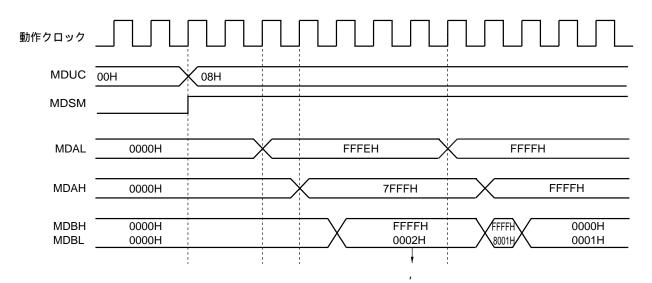

|       | 15. 4. 2 乗算(符号付)動作                       | 745 |

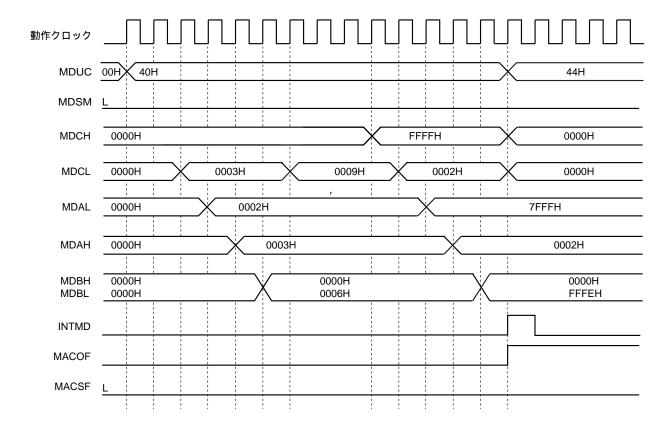

|       | 15. 4. 3 積和演算(符号なし)動作                    | 746 |

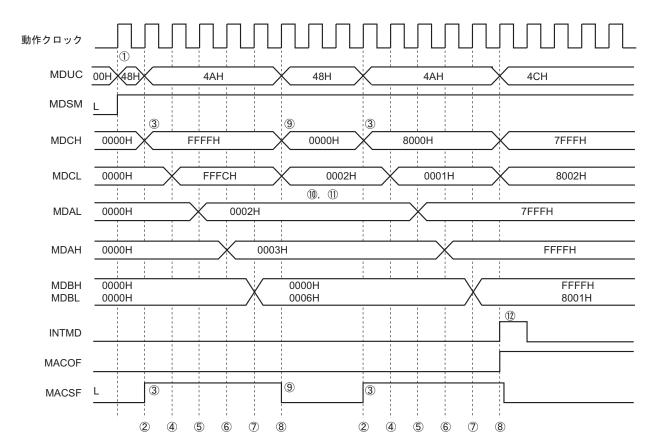

|       | 15. 4. 4 積和演算(符号付)動作                     | 748 |

|       | 15. 4. 5 除算動作                            | 750 |

|       |                                          |     |

| 第16章             | DMAコントローラ                                                 | 752 |

|------------------|-----------------------------------------------------------|-----|

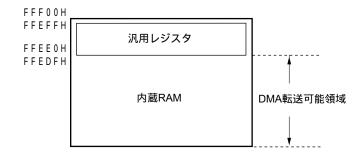

| 16. 1            | DMAコントローラの機能                                              | 752 |

|                  | DMAコントローラの構成                                              |     |

|                  | 16. 2. 1 DMA SFRアドレス・レジスタn(DSAn)                          |     |

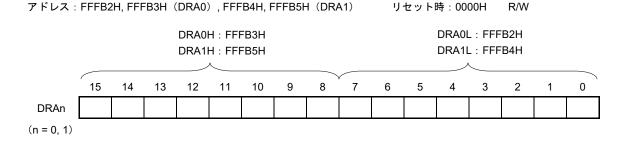

|                  | 16. 2. 2 DMA RAMアドレス・レジスタn(DRAn)                          |     |

|                  | 16. 2. 3 DMAバイト・カウント・レジスタn (DBCn)                         |     |

| 16. 3            | DMAコントローラを制御するレジスタ                                        | 756 |

|                  | 16.3.1 DMAモード・コントロール・レジスタn (DMCn)                         | 757 |

|                  | 16.3.2 DMA動作コントロール・レジスタn (DRCn)                           | 759 |

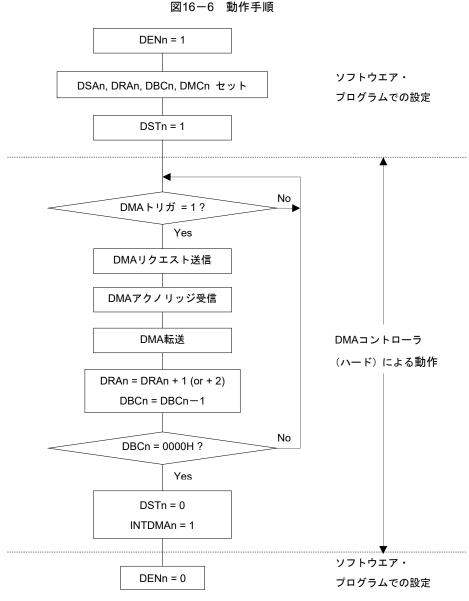

| 16. 4            | DMAコントローラの動作                                              | 760 |

|                  | 16. 4. 1 動作手順                                             | 760 |

|                  | 16.4.2 転送モード                                              | 761 |

|                  | 16.4.3 DMA転送の終了                                           | 761 |

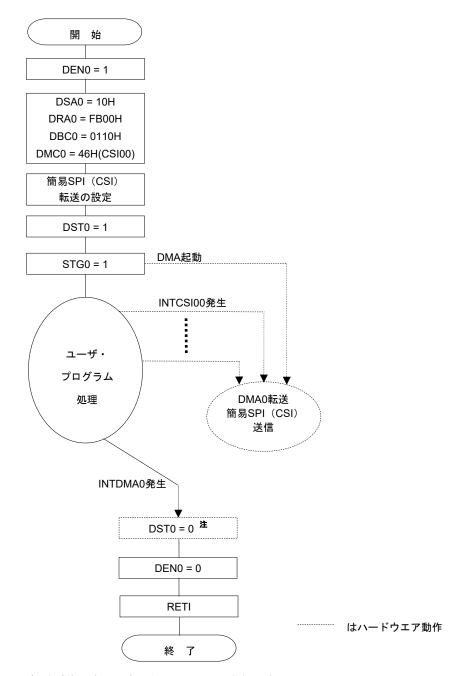

| 16. 5            | DMAコントローラの設定例                                             | 762 |

|                  | 16. 5. 1 簡易SPI (CSI) 連続送信                                 | 762 |

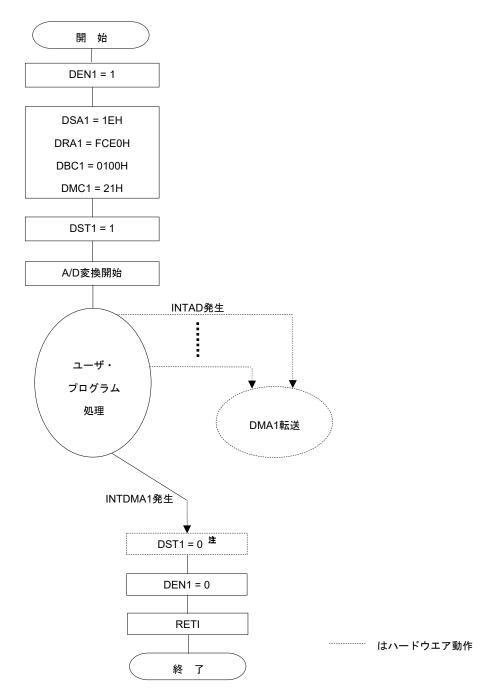

|                  | 16. 5. 2 A/D変換結果の連続取り込み                                   |     |

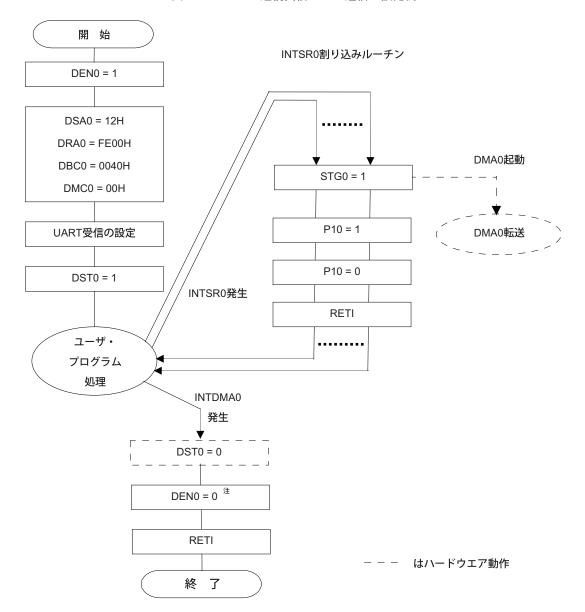

|                  | 16. 5. 3 UART連続受信+ACK送信                                   |     |

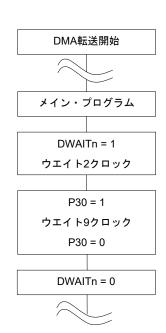

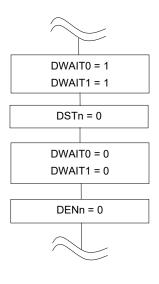

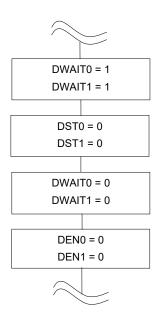

|                  | 16. 5. 4 DWAITnビットによるDMA転送保留                              |     |

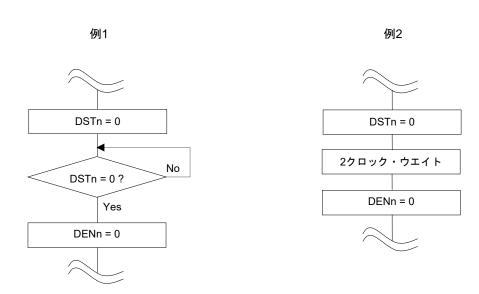

|                  | 16. 5. 5 ソフトウエアでの強制終了                                     |     |

| 16. 6            | DMAコントローラの注意事項                                            | 771 |

| 第17章             | 割り込み機能                                                    | 774 |

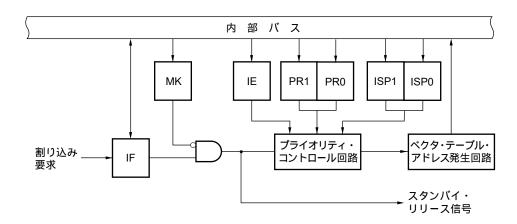

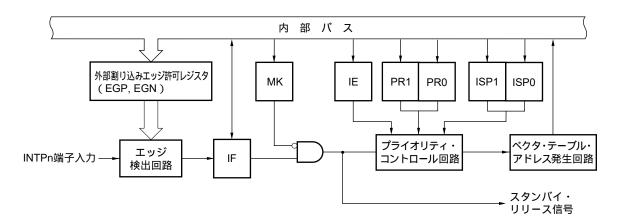

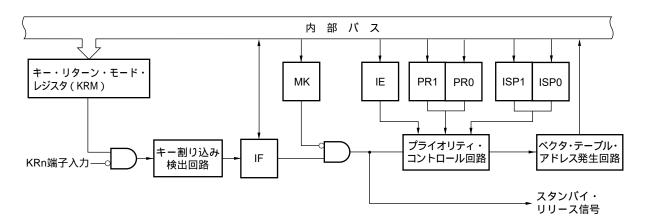

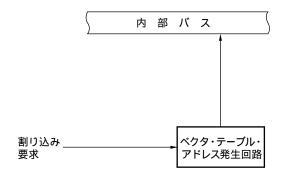

| 17 1             | 割り込み機能の種類                                                 | 774 |

|                  | 割り込み要因と構成                                                 |     |

|                  | 割り込み機能を制御するレジスタ                                           |     |

|                  | 17.3.1 割り込み要求フラグ・レジスタ(IFOL, IFOH, IF1L, IF1H, IF2L, IF2H) |     |

|                  | 17. 3. 2 割り込みマスク・フラグ・レジスタ                                 |     |

|                  | (MK0L, MK0H, MK1L, MK1H, MK2L, MK2H)                      | 785 |

|                  | 17.3.3 優先順位指定フラグ・レジスタ (PR00L, PR00H, PR01L, PR01H, PR02L, |     |

|                  | PR02H, PR10L, PR10H, PR11L, PR11H, PR12L, PR12H)          | 787 |

|                  | 17. 3. 4 外部割り込み立ち上がりエッジ許可レジスタ(EGP0, EGP1),                |     |

|                  | 外部割り込み立ち下がりエッジ許可レジスタ(EGN0, EGN1)                          | 789 |

|                  | 17.3.5 プログラム・ステータス・ワード (PSW)                              | 791 |

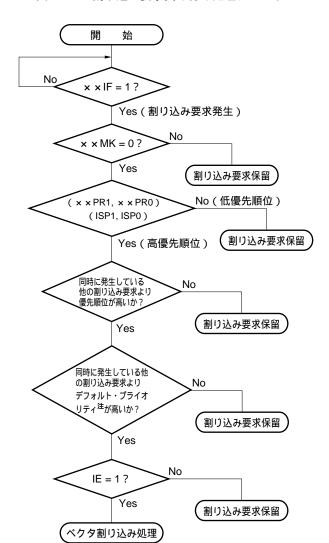

| 17. 4            | 割り込み処理動作                                                  |     |

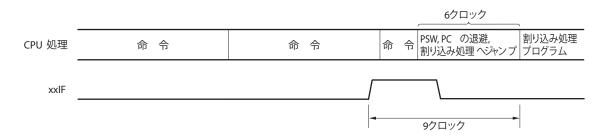

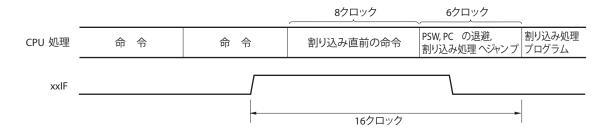

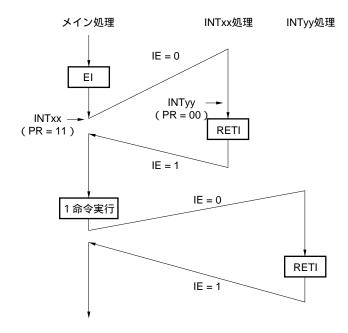

|                  | 17.4.1 マスカブル割り込み要求の受け付け動作                                 | 792 |

|                  | 17.4.2 ソフトウェア割り込み要求の受け付け動作                                | 795 |

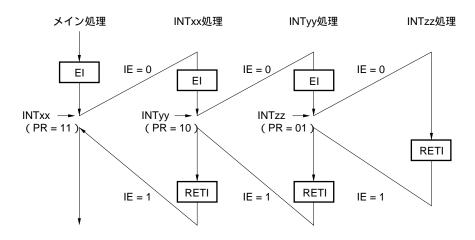

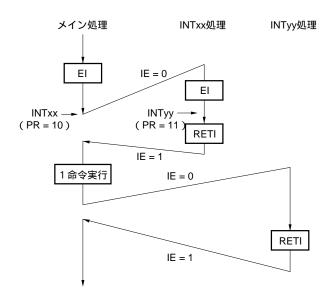

|                  | 17.4.3 多重割り込み処理                                           |     |

|                  | 17.4.4 割り込み要求の保留                                          | 799 |

| 第18章             | キー割り込み機能                                                  | 800 |

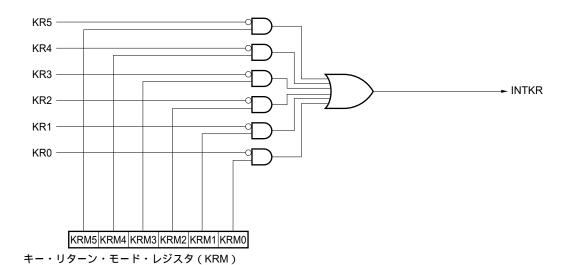

| 18. 1            | キー割り込みの機能                                                 | 800 |

|                  | キー割り込みの構成                                                 |     |

|                  | キー割り込みを制御するレジスタ                                           |     |

|                  | 18. 3. 1 キー・リターン・モード・レジスタ(KRM)                            |     |

|                  | 18. 3. 2 ポート・モード・レジスタ7 (PM7)                              |     |

| 笙10 <del>音</del> | スタンバイ機能                                                   | ደበ/ |

| カラー              | - インプ - イ *   10X 目E                                      |     |

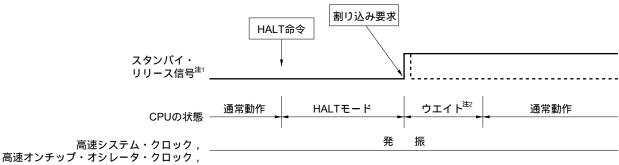

| 19. 1 | スタンバイ機能                                  | 804 |

|-------|------------------------------------------|-----|

| 19. 2 | スタンバイ機能を制御するレジスタ                         | 805 |

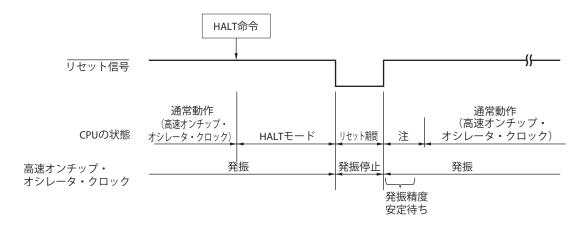

| 19. 3 | スタンバイ機能の動作                               | 806 |

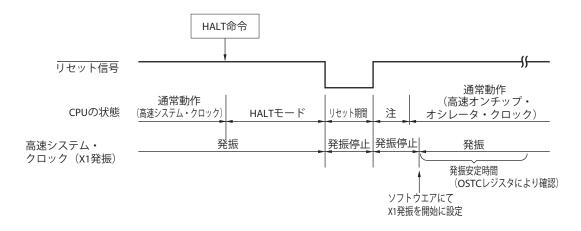

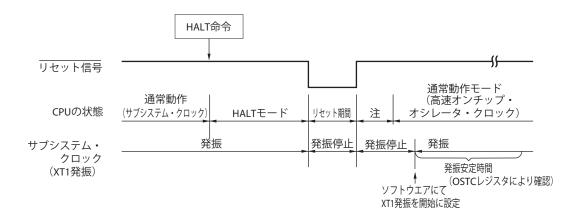

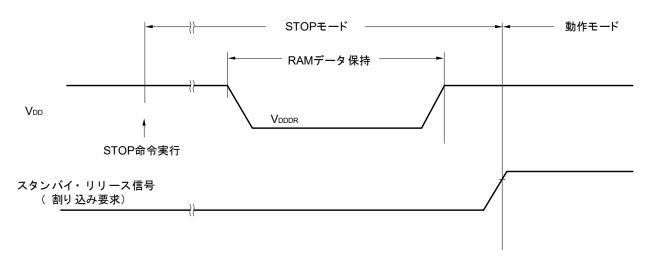

|       | 19. 3. 1 HALTモード                         | 806 |

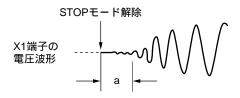

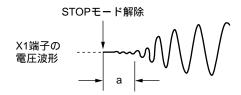

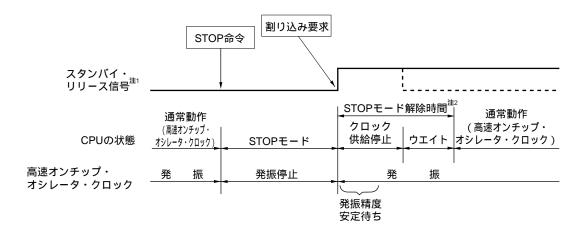

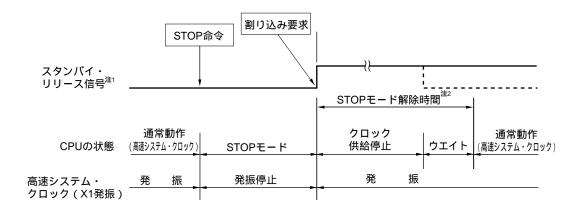

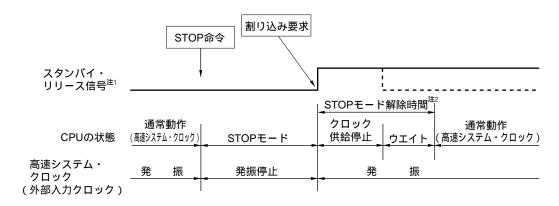

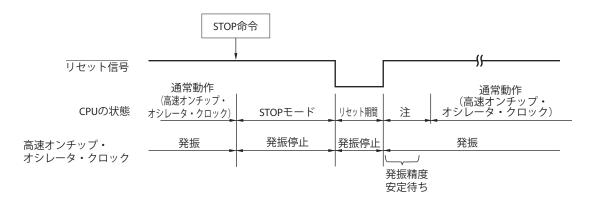

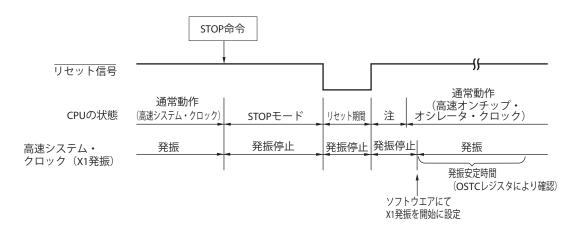

|       | 19.3.2 STOPモード                           | 811 |

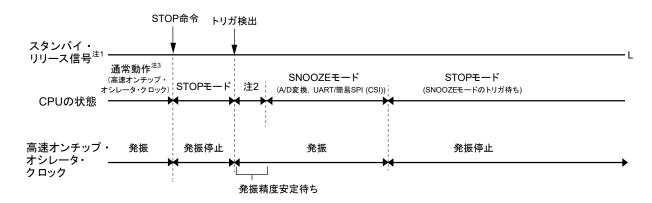

|       | 19. 3. 3 SNOOZEモード                       | 817 |

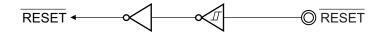

| 第20章  | リセット機能                                   | 820 |

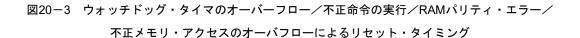

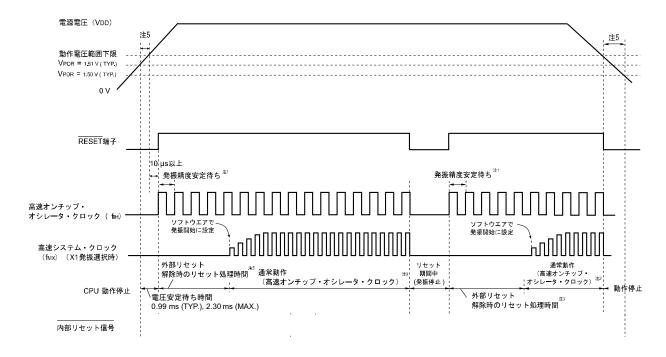

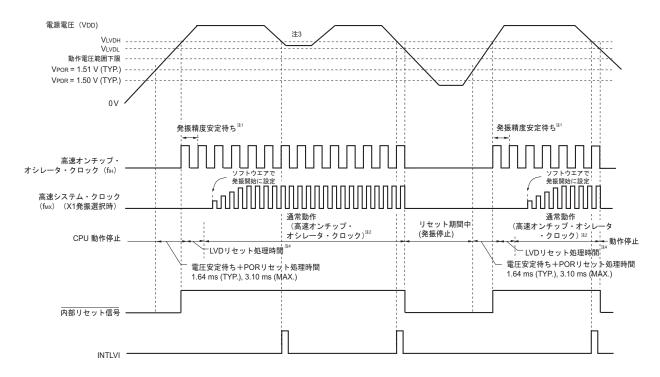

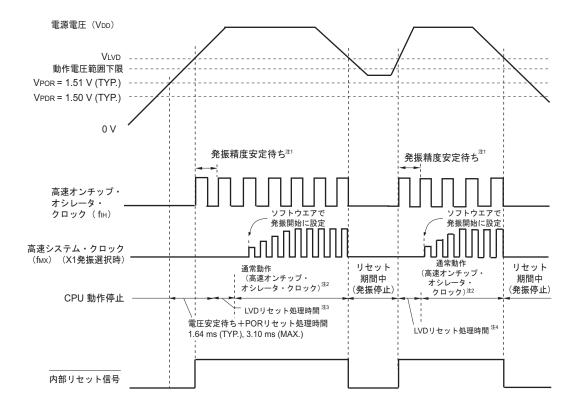

| 20. 1 | リセット動作のタイミング                             | 822 |

|       | リセット期間中の動作状態                             |     |

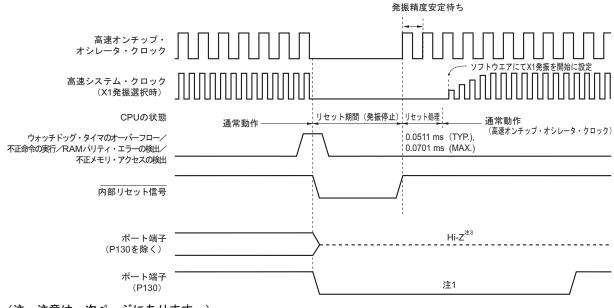

| 20. 2 | リセット要因を確認するレジスタ                          |     |

| 20. 0 | 20. 3. 1 リセット・コントロール・フラグ・レジスタ(RESF)      |     |

| 第21章  | パワーオン・リセット回路                             | 829 |

| 21 1  | パワーオン・リセット回路の機能                          | 820 |

|       | パワーオン・リセット回路の構成                          |     |

|       | パワーオン・リセット回路の動作                          |     |

| 21.0  | , パク カン サビノド回応の到下                        | 000 |

| 第22章  | 電圧検出回路                                   | 834 |

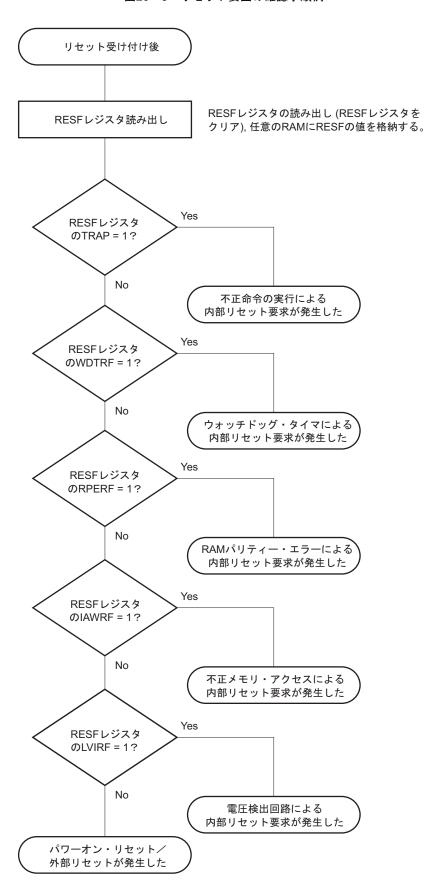

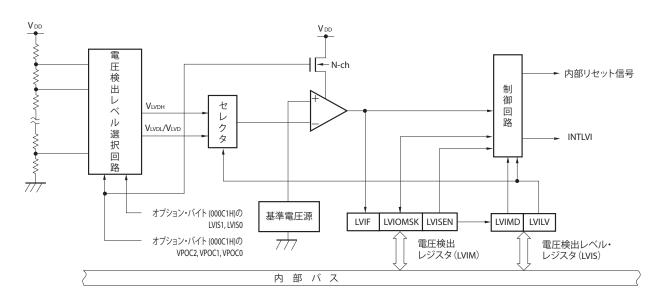

| 22. 1 | 電圧検出回路の機能                                | 834 |

| 22. 2 | 電圧検出回路の構成                                | 835 |

|       |                                          |     |

|       | 22. 3. 1 電圧検出レジスタ(LVIM)                  | 836 |

|       | 22. 3. 2 電圧検出レベル・レジスタ(LVIS)              | 837 |

| 22. 4 | 電圧検出回路の動作                                | 840 |

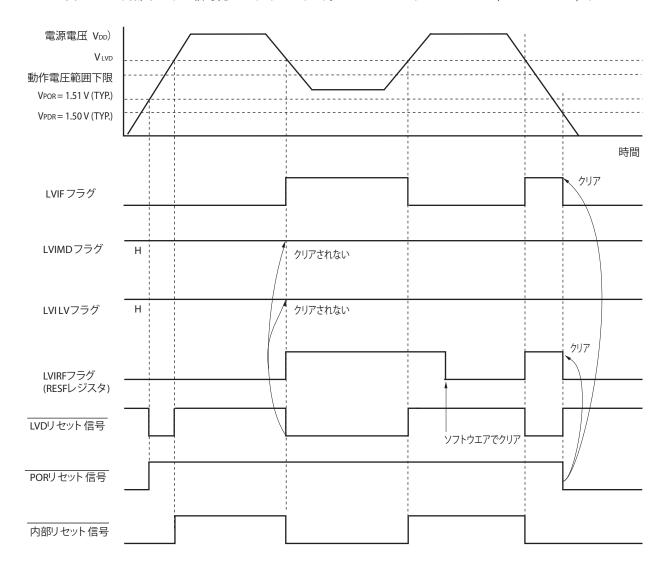

|       | 22. 4. 1 リセット・モードとして使用する場合の設定            |     |

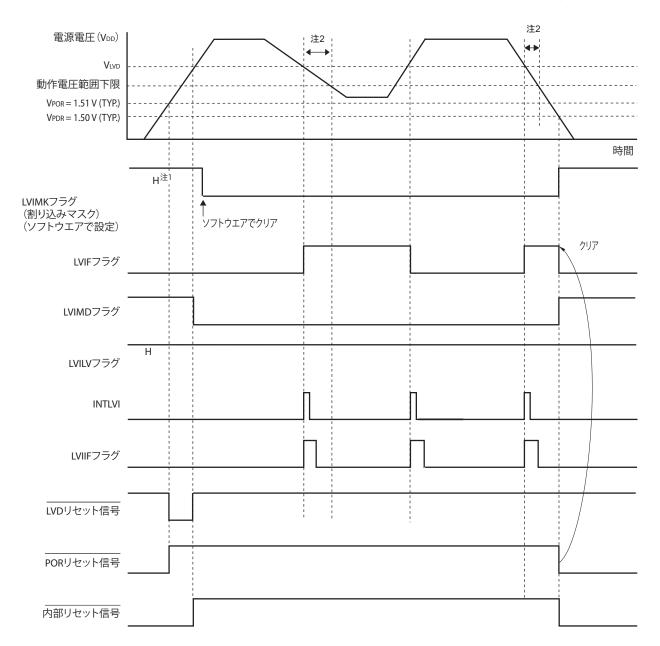

|       | 22.4.2 割り込みモードとして使用する場合の設定               | 842 |

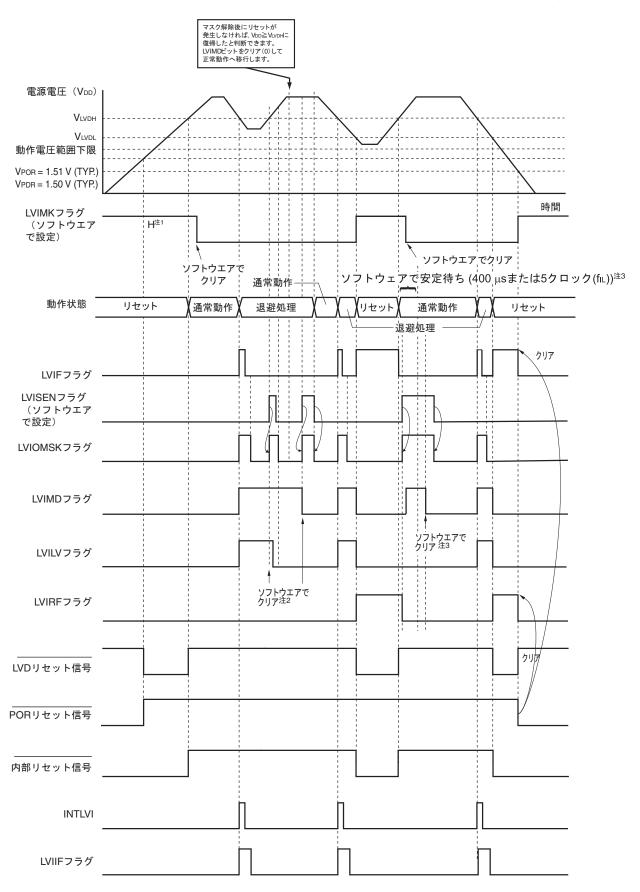

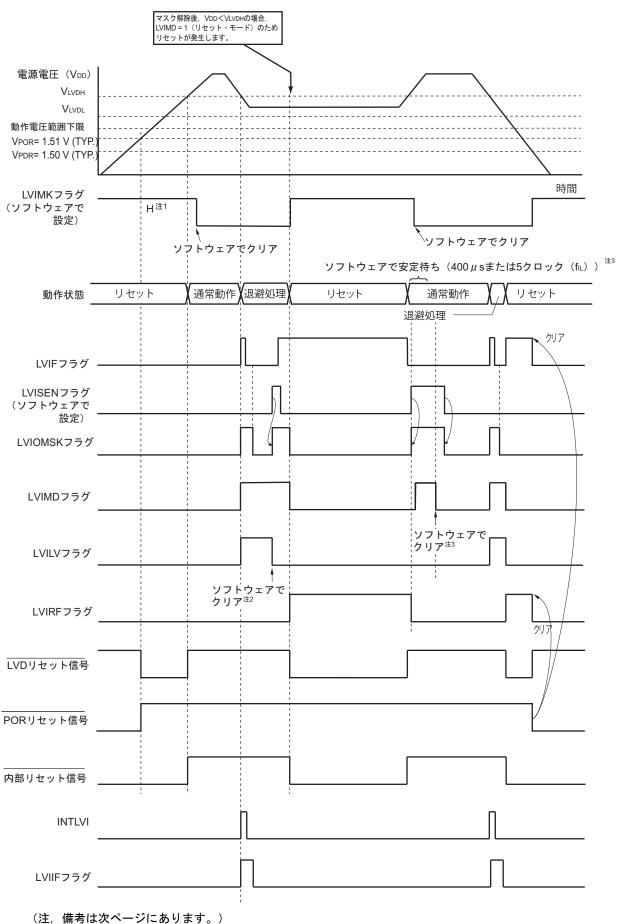

|       | 22.4.3 割り込み&リセット・モードとして使用する場合の設定         |     |

| 22. 5 | 電圧検出回路の注意事項                              | 849 |

| 第23章  | 安全機能                                     | 851 |

| 23. 1 | 安全機能の概要                                  | 851 |

| 23. 2 | 安全機能で使用するレジスタ                            | 852 |

| 23. 3 | 安全機能の動作                                  | 852 |

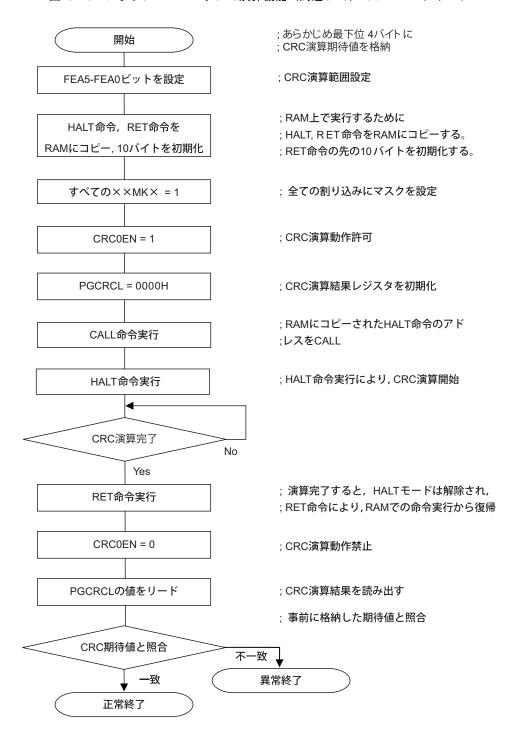

|       | 23. 3. 1 フラッシュ・メモリCRC演算機能(高速CRC)         | 852 |

|       | 23. 3. 1. 1 フラッシュ・メモリCRC制御レジスタ(CRC0CTL)  | 853 |

|       | 23. 3. 1. 2 フラッシュ・メモリCRC演算結果レジスタ(PGCRCL) | 854 |

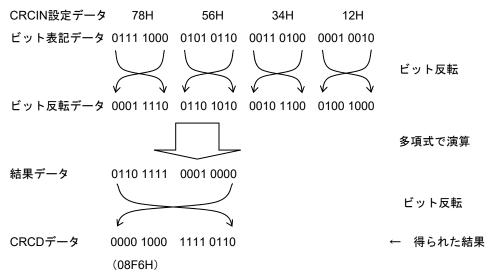

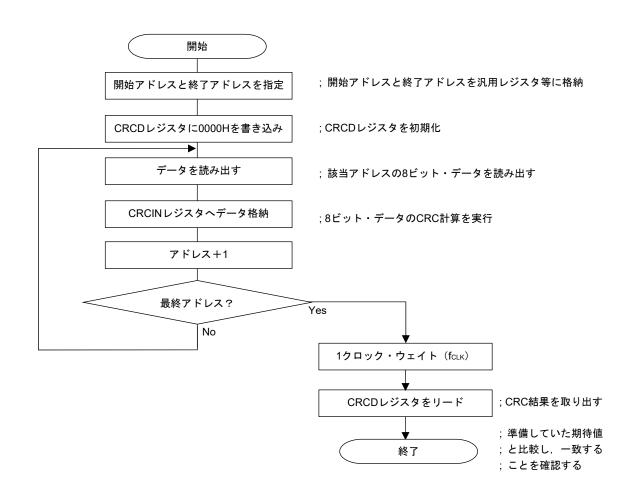

|       | 23. 3. 2 CRC演算機能(汎用CRC)                  |     |

|       | 23. 3. 2. 1 CRC入力レジスタ(CRCIN)             | 856 |

|       | 23. 3. 2. 2 CRCデータ・レジスタ (CRCD)           |     |

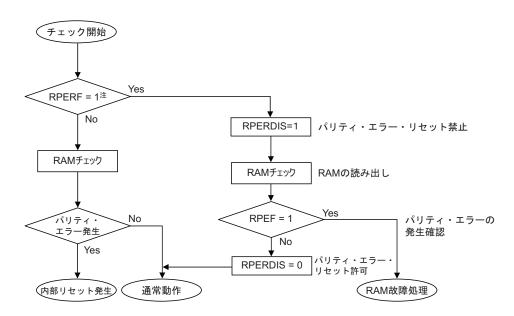

|       | 23. 3. 3 RAMパリティ・エラー検出機能                 |     |

|       | 23. 3. 3. 1 RAMパリティ・エラー制御レジスタ(RPECTL)    |     |

|       | 23. 3. 4 RAMガード機能                        |     |

|       | 23. 3. 4. 1 不正メモリ・アクセス検出制御レジスタ(IAWCTL)   |     |

|       | 23. 3. 5 SFRガード機能                        |     |

|       | 23. 3. 5. 1 不正メモリ・アクセス検出制御レジスタ(IAWCTL)   |     |

|       | 23.3.6 不正メモリ・アクセス検出機能                    |     |

|       | 23. 3. 6. 1不正メモリ・アクセス検出制御レジスタ(IAWCTL)23. 3. 7周波数検出機能 |     |

|-------|------------------------------------------------------|-----|

|       | 23. 3. 7. 1 タイマ入力選択レジスタ0(TISO)                       |     |

|       | 23. 3. 8 A/Dテスト機能                                    |     |

|       | 23. 3. 8. 1 A/Dテスト・レジスタ(ADTES)                       |     |

|       | 23. 3. 8. 2 アナログ入力チャネル指定レジスタ(ADS)                    |     |

|       | 23. 3. 9 入出力ポートのデジタル出力信号レベル検出機能                      |     |

|       | 23. 3. 9. 1 ポート・モード選択レジスタ(PMS)                       |     |

|       |                                                      |     |

| 第24章  | レギュレータ                                               | 871 |

| 24. 1 | レギュレータの概要                                            | 871 |

| 第25章  | オプション・バイト                                            | 872 |

| 05.4  |                                                      | 070 |

| 25. 1 | オプション・バイトの機能                                         |     |

|       | 25. 1. 1 ユーザ・オプション・バイト (000C0H-000C2H/010C0H-010C2H) |     |

|       | 25. 1. 2 オンチップ・デバッグ・オプション・バイト (000C3H/010C3H)        |     |

|       | ユーザ・オプション・バイトのフォーマット                                 |     |

|       | オンチップ・デバッグ・オプション・バイトのフォーマット                          |     |

| 25. 4 | オプション・バイトの設定                                         | 879 |

| 第26章  | フラッシュ・メモリ                                            | 880 |

| 00.4  | フラッシュ・メモリ・プログラマによるシリアル・プログラミング                       | 000 |

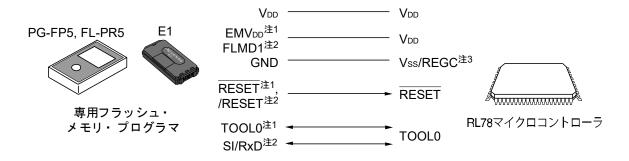

| 26. 1 |                                                      |     |

|       | 26. 1. 1 プログラミング環境                                   |     |

|       | 26. 1. 2 通信方式                                        |     |

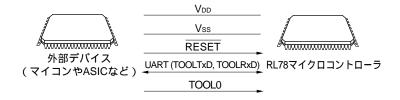

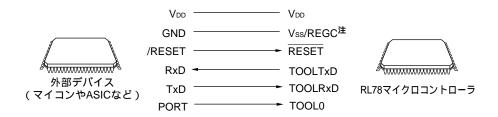

| 26. 2 | 外部デバイス(UART内蔵)によるシリアル・プログラミング                        |     |

|       | 26. 2. 1 プログラミング環境                                   |     |

|       | 26. 2. 2 通信方式                                        |     |

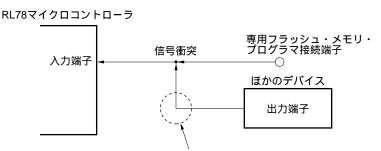

| 26. 3 | オンボード上の端子処理                                          |     |

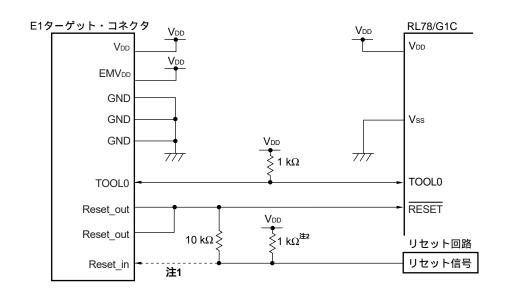

|       | 26. 3. 1 P40/TOOL0端子                                 |     |

|       | 26. 3. 2 RESET端子                                     |     |

|       | 26.3.3 ポート端子                                         | 888 |

|       | 26. 3. 4 REGC端子                                      | 888 |

|       | 26. 3. 5 X1, X2端子                                    | 888 |

|       | 26. 3. 6 電 源                                         | 888 |

| 26. 4 | シリアル・プログラミング方法                                       | 889 |

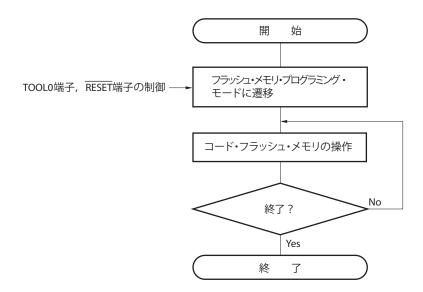

|       | 26. 4. 1 シリアル・プログラミング手順                              | 889 |

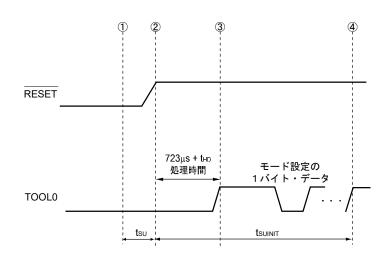

|       | 26. 4. 2 フラッシュ・メモリ・プログラミング・モード                       |     |

|       | 26. 4. 3 通信方式                                        |     |

|       | 26.4.4 通信コマンド                                        |     |

| 26.5  |                                                      |     |

|       | セルフ・プログラミング                                          |     |

| 20. 0 | 26. 6. 1 セルフ・プログラミング手順                               |     |

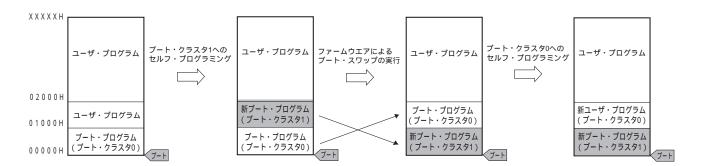

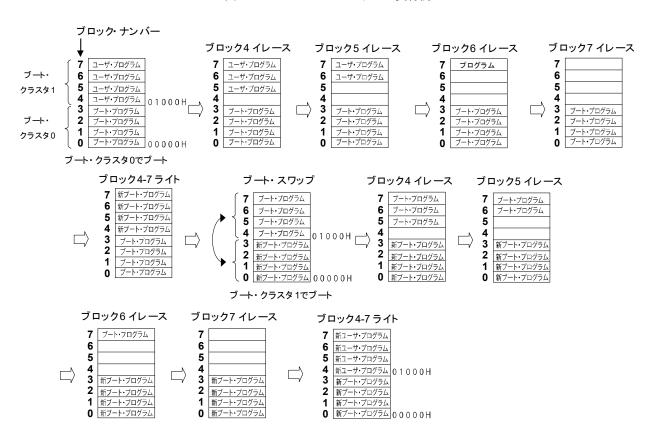

|       | 26. 6. 2 ブート・スワップ機能                                  |     |

|       | 26. 6. 3 フラッシュ・シールド・ウインドウ機能                          |     |

| 26.7  | 20.0.3 フラグフュ・フールド・ラインドラ機能                            |     |

|       | ゼヤュリティ設定                                             |     |

| ∠0. δ | テーダ・フラッシュ                                            |     |

|       | 26.8.1 データ・フラッシュの概要                                  |     |

|       | 26. 8. 2                                             |     |

|       | zv. o. z. ェーナーダ・フラッシュ・コフトロール・レン人ダ(UFLUTL)            | 904 |

|       | 26.8.3 データ・フラッシュへのアクセス手順             | 905  |

|-------|--------------------------------------|------|

| 第27章  | オンチップ・デバッグ機能                         | 907  |

| 07.4  |                                      | 0.0- |

|       | E1オンチップデバッギングエミュレータとRL78/G1Cの接続      |      |

|       | オンチップ・デバッグ・セキュリティID                  |      |

| 27. 3 | ユーザ資源の確保                             | 908  |

| 第28章  | 10進補正(BCD)回路                         | 910  |

| 28. 1 | 10進補正回路の機能                           | 910  |

| 28. 2 | 10進補正回路で使用するレジスタ                     | 910  |

|       | 28. 2. 1 BCD補正結果レジスタ(BCDADJ)         | 910  |

| 28. 3 | 10進補正回路の動作                           | 911  |

| 第29章  | 命令セットの概要                             | 913  |

| 29. 1 | 凡                                    | 914  |

|       | 29. 1. 1 オペランドの表現形式と記述方法             | 914  |

|       | 29. 1. 2 オペレーション欄の説明                 | 915  |

|       | 29. 1. 3 フラグ動作欄の説明                   | 916  |

|       | 29. 1. 4 PREFIX命令                    | 916  |

| 29. 2 | オペレーション一覧                            | 917  |

| 第30章  | 電気的特性(A:TA = -40~+85℃)               | 934  |

| 30. 1 | 絶対最大定格                               | 935  |

| 30. 2 | <b>発振回路特性</b>                        | 937  |

|       | 30. 2. 1 X1, XT1発振回路特性               | 937  |

|       | 30. 2. 2 オンチップ・オシレータ特性               | 937  |

|       | 30. 2. 3 PLL発振回路特性                   | 938  |

| 30. 3 | DC特性                                 | 939  |

|       | 30. 3. 1 端子特性                        | 939  |

|       | 30. 3. 2 電源電流特性                      | 944  |

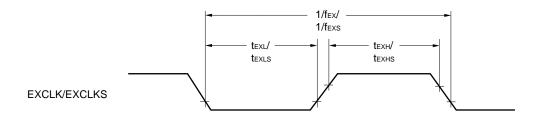

| 30. 4 | AC特性                                 | 951  |

|       | 30. 4. 1 基本動作                        | 951  |

| 30. 5 | 周辺機能特性                               | 954  |

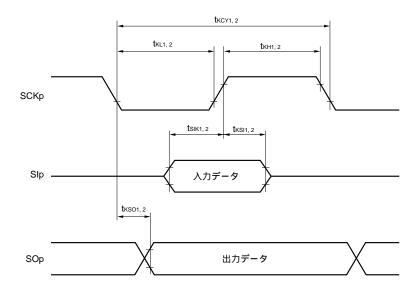

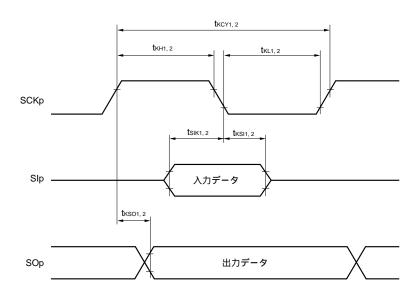

|       | 30. 5. 1 シリアル・アレイ・ユニット               | 954  |

|       | 30. 5. 2 シリアル・インタフェースIICA            | 977  |

|       | 30. 5. 3 USB                         | 980  |

| 30. 6 | アナログ特性                               | 984  |

|       | 30. 6. 1 A/Dコンバータ特性                  | 984  |

|       | 30.6.2 温度センサ/内部基準電圧特性                |      |

|       | 30. 6. 3 POR回路特性                     |      |

|       | 30. 6. 4 LVD回路特性                     |      |

|       | 30.6.5 電源電圧立ち上がり傾き特性                 |      |

| 30. 7 | RAMデータ保持特性                           |      |

|       | フラッシュ・メモリ・プログラミング特性                  |      |

|       | ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |      |

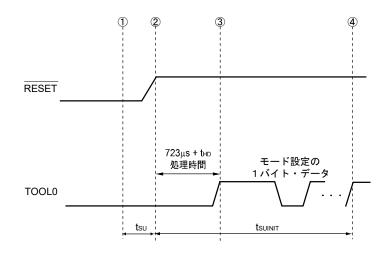

|       | 0 フラッシュ・メモリ・プログラミング・モードの引き込み時のタイミング  |      |

| 第31章 電気的特性(G:TA=―40~+105℃)           | 994   |

|--------------------------------------|-------|

| 31.1 絶対最大定格                          | 995   |

| 31. 2 発振回路特性                         |       |

| 31. 2. 1 X1, XT1発振回路特性               |       |

| 31. 2. 2 オンチップ・オシレータ特性               |       |

| 31. 2. 3 PLL発振回路特性                   |       |

| 31. 3 DC特性                           |       |

| 31. 3. 1 端子特性                        |       |

| 31. 3. 2 電源電流特性                      | 1004  |

| 31. 4 AC特性                           | 1011  |

| 31. 4. 1 基本動作                        | 1011  |

| 31. 5 周辺機能特性                         | 1014  |

| 31. 5. 1 シリアル・アレイ・ユニット               | 1014  |

| 31. 5. 2 シリアル・インタフェースIICA            | 1034  |

| 31. 5. 3 USB                         | 1035  |

| 31.6 アナログ特性                          | 1039  |

| 31. 6. 1 A/Dコンバータ特性                  | 1039  |

| 31. 6. 2 温度センサ/内部基準電圧特性              |       |

| 31. 6. 3 POR回路特性                     |       |

| 31. 6. 4 LVD回路特性                     |       |

| 31.6.5 電源電圧立ち上がり傾き特性                 |       |

| 31. 7 RAMデータ保持特性                     |       |

| 31. 8 フラッシュ・メモリ・プログラミング特性            |       |

| 31. 9 専用フラッシュ・メモリ・プログラマ通信(UART)      |       |

| 31. 10 フラッシュ・メモリ・プログラミング・モード引き込みタイミン | グ1048 |

| 第32章 外形 図                            | 1049  |

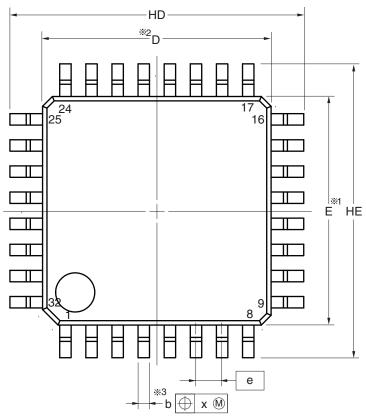

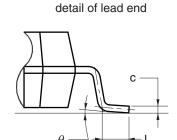

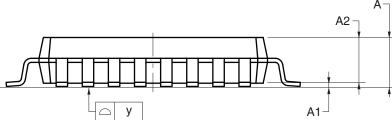

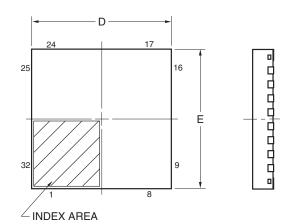

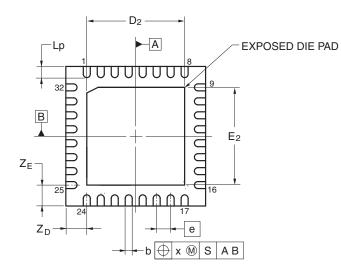

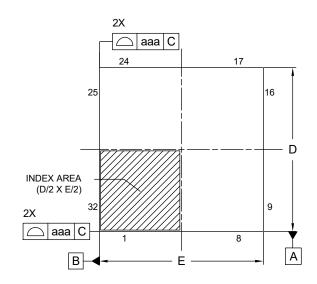

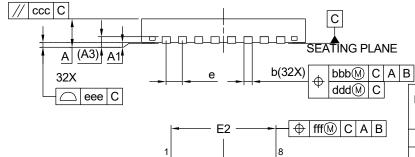

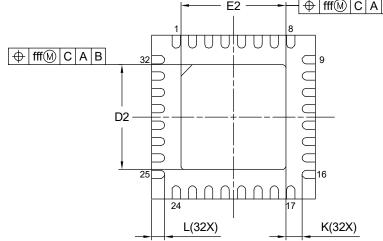

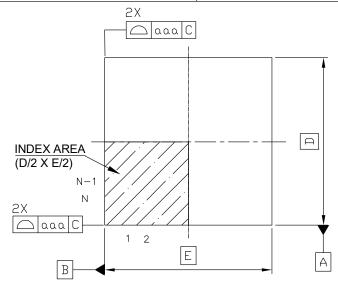

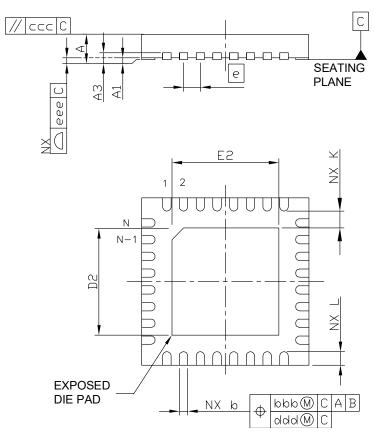

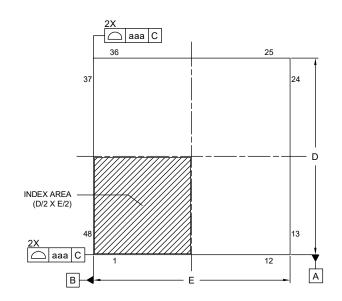

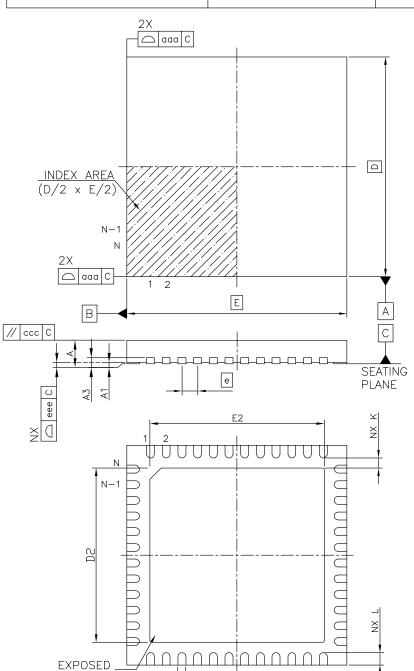

| 32. 1 32ピン製品                         | 1049  |

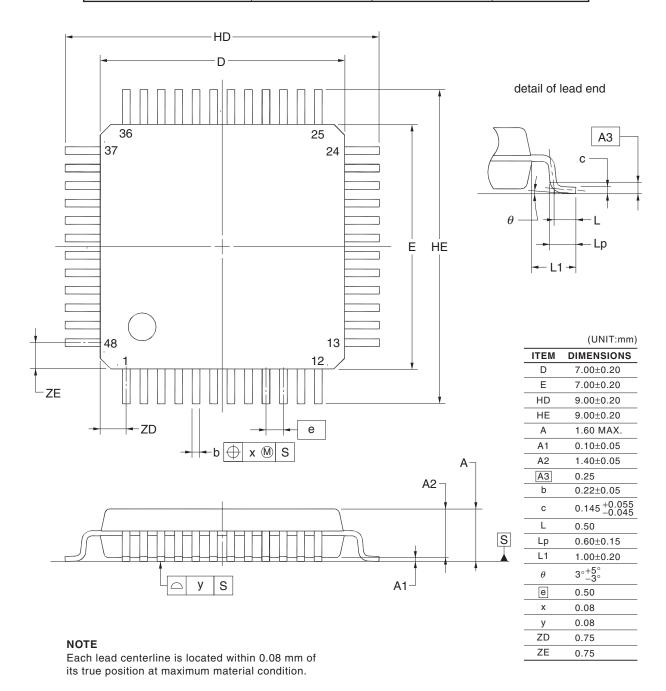

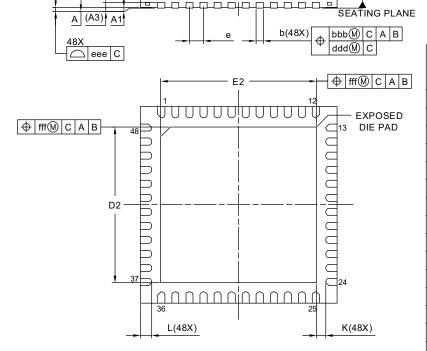

| 32. 2 48ピン製品                         | 1053  |

| 付録A 改版履歴                             | 1057  |

| A. 1 本版で改訂された主な箇所                    | 1057  |

| Δ 2 前版主での改版履歴                        | 1058  |

RL78/G1C ルネサスマイクロコンピュータ

R01UH0348JJ0140 Rev.1.40 2024.04.26

# 第1章 概 説

## 1.1 特 徵

## 超低消費電力テクノロジー

- VDD = 2.4~5.5 Vの単一電源

- HALTモード

- STOPモード

- SNOOZEモード

#### RL78 CPUコア

- 3段パイプラインのCISCアーキテクチャ

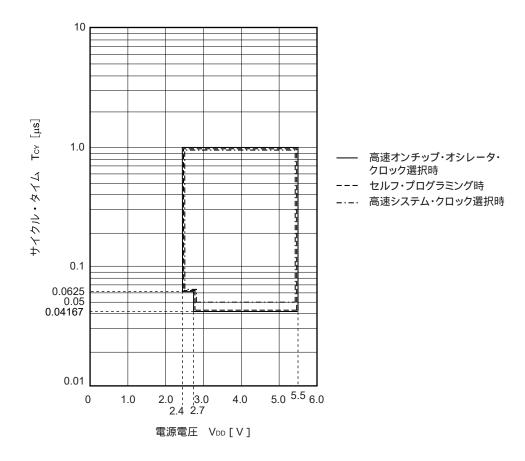

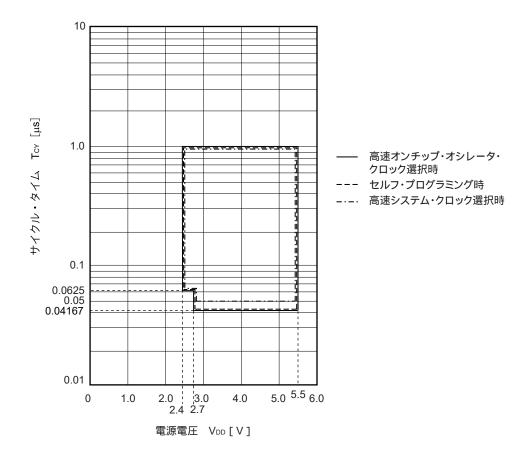

- 最小命令実行時間: 高速 (0.04167 μs: 高速オンチップ・オシレータ・クロックまたはPLLクロック24 MHz 動作時) から超低速 (30.5 μs: サブシステム・クロック32.768 kHz動作時) までを変更可能

- アドレス空間:1Mバイト

- 汎用レジスタ:8ビット・レジスタ×8×4バンク

- 内蔵RAM: 5.5 KB

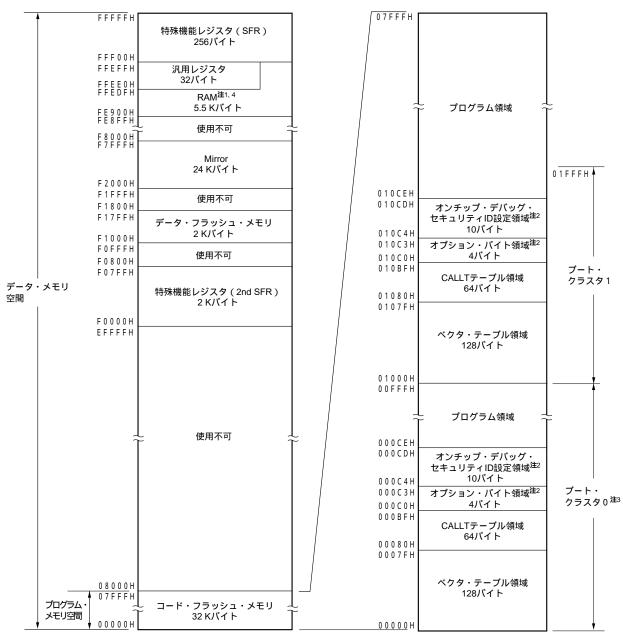

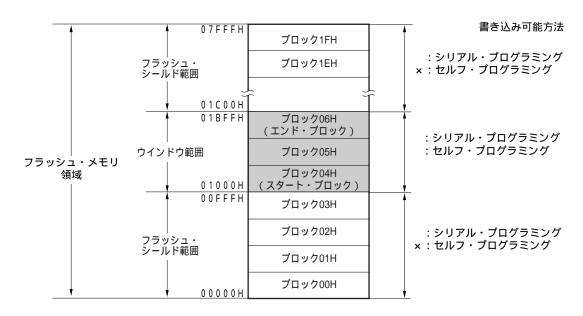

## コード・フラッシュ・メモリ

- コード・フラッシュ・メモリ:32 KB

- ブロック・サイズ:1KB

- ブロック消去禁止、書き換え禁止(セキュリティ機能)

- オンチップ・デバッグ機能内蔵

- セルフ・プログラミング:ブート・スワップ機能とフラッシュ・シールド・ウインドウ機能あり

## データ・フラッシュ・メモリ

- データ・フラッシュ・メモリ:2 KB

- バックグランド・オペレーション(BGO), データ・フラッシュの書き換え動作中に, プログラム・メモリ内の命令実行

- 書き換え回数:1,000,000回(TYP.)

- 書き換え電圧: VDD = 2.4~5.5 V

## 高速オンチップ・オシレータ

- 48 MHz/24 MHz/12 MHz/6 MHzから選択

- 高精度±1.0 % (V<sub>DD</sub> = 2.4~5.5 V, T<sub>A</sub> = -20~+85 °C)

## 動作周囲温度

- T<sub>A</sub> = -40~+85 °C (A:民生用途)

- T<sub>A</sub> = -40~+105 °C (G:産業用途)

#### 電源管理とリセット機能

- パワーオン・リセット (POR) 回路内蔵

- 電圧検出(LVD)回路内蔵(割り込み、リセットを9段階で選択)

#### DMA (Direct Memory Access) コントローラ

- 2チャネル搭載

- 8ビット/16ビットのSFR⇔内蔵RAM間の転送が2クロック

#### 乗除·積和演算器

- 16ビット×16ビット = 32ビット (符号付/符号なし)

- 32ビット÷32ビット = 32ビット(符号なし)

- 16ビット×16ビット+32ビット = 32ビット (符号付/符号なし)

#### USB

- USBバージョン2.0準拠,ホスト・ファンクション機能搭載

- フル・スピード転送(12 Mbps), ロウ・スピード(1.5 Mbps)に対応

- USB Battery Charging Specification Revision 1.2準拠

- Apple社MFi仕様, USB power supply component specification 2.1A/1.0A充電モードに対応<sup>注1</sup>

#### シリアル・インタフェース

簡易SPI (CSI<sup>注2</sup>) : 2チャネルUART : 1チャネル

● I<sup>2</sup>C/簡易I<sup>2</sup>C : 1チャネル/2チャネル

#### タイマ

■ 16ビット・タイマ : 4チャネル■ 12ビット・インターバル・タイマ : 1チャネル

● リアルタイム・クロック : 1チャネル (99年カレンダ, アラーム機能, 時計補正機能)

● ウォッチドッグ・タイマ : 1チャネル (専用の低速オンチップ・オシレータ・クロックで動作可能)

### A/Dコンバータ

- 8/10ビット分解能A/Dコンバータ (V<sub>DD</sub> = 2.4~5.5 V)

- アナログ入力:8~9チャネル

- 内部基準電圧(1.45 V) と温度センサ搭載

#### 入出力ポート

- I/Oポート: 22~38本(N-chオープン・ドレイン入出力 [6 V耐圧]: 3, 4本, N-chオープン・ドレイン入出力 [Vpp耐圧]: 5, 6本)

- N-chオープン・ドレイン、TTL入力バッファ、内蔵プルアップの切り替え可能

- キー割り込み機能内蔵

- クロック出力/ブザー出力制御回路内蔵

- 注1 Apple社充電モードの導入に当たって、Apple社のMade for iPod/iPhone/iPad (MFi) ライセンスプログラムに登録する必要があります。

本仕様を請求する場合、先にApple社のMFIに加入した上でお問い合わせください。

注2 一般的にはSPIと呼ばれる機能ですが、本製品ではCSIとも呼称しているため、本マニュアルでは併記します。

備考 製品によって、搭載している機能が異なります。1.6 機能概要を参照してください。

#### その他

● 10進補正 (BCD) 回路内蔵

#### ROM, RAM容量

| フラッシュROM | データ・フラッシュ | RAM                 | RL78/G1C           |                    |

|----------|-----------|---------------------|--------------------|--------------------|

|          |           |                     | 32ピン               | 48ピン               |

| 32 KB    | 2 KB      | 5.5 KB <sup>注</sup> | R5F10JBC, R5F10KBC | R5F10JGC, R5F10KGC |

注 5.5 Kバイトの場合, セルフ・プログラミング機能使用時は約4.5 Kバイト (詳細は, **第3章 CPUアーキテクチャ**参照)。

備考 製品により、搭載している機能が異なります。1.6 機能概要を参照してください。

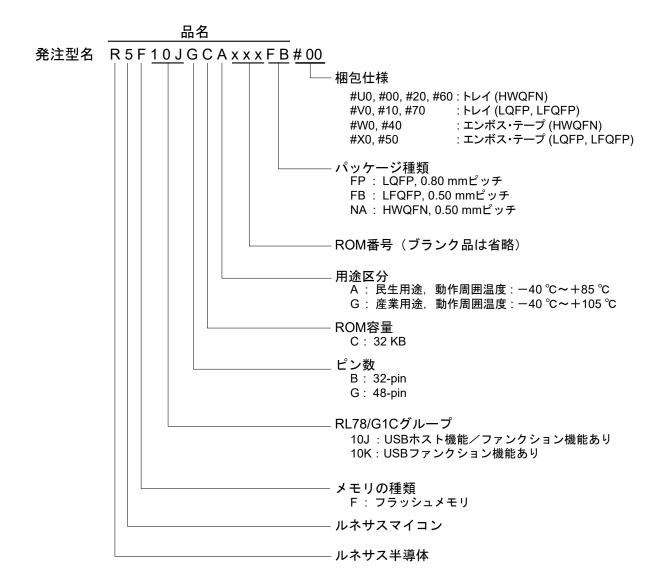

## 1.2 型名一覧

$\star$

図1-1 RL78/G1Cの型名とメモリサイズ・パッケージ

表1-1 発注型名一覧

|          | ピン数  | パッケージ             | USB機能   | 用途              | 発注型名        |                     | ルネサス・コード     |

|----------|------|-------------------|---------|-----------------|-------------|---------------------|--------------|

|          |      |                   |         | 区分 <sup>注</sup> | 品名          | 梱包仕様                |              |

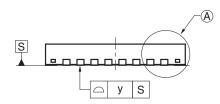

|          | 32ピン | 32ピン・プラスチッ        | ホスト/ファン | Α               | R5F10JBCANA | #U0, #W0            | PWQN0032KB-A |

| *        |      | クHWQFN            | クション機能  |                 |             | #00, #20, #40, #60  | PWQN0032KE-A |

|          |      | (5 x 5 mm, 0.5 mm |         |                 |             |                     | PWQN0032KG-A |

|          |      | ピッチ)              |         | G               | R5F10JBCGNA | #U0, #W0            | PWQN0032KB-A |

| *        |      |                   |         |                 |             | #00, #20, #40, #60  | PWQN0032KE-A |

|          |      |                   |         |                 |             |                     | PWQN0032KG-A |

|          |      |                   | ファンクション | Α               | R5F10KBCANA | #U0, #W0            | PWQN0032KB-A |

| *        |      |                   | 機能のみ    |                 |             | #00, #20, #40, #60  | PWQN0032KE-A |

|          |      |                   |         |                 |             |                     | PWQN0032KG-A |

|          |      |                   |         | G               | R5F10KBCGNA | #U0, #W0            | PWQN0032KB-A |

| *        |      |                   |         |                 |             | #00, #20, #40, #60  | PWQN0032KE-A |

|          |      |                   |         |                 |             |                     | PWQN0032KG-A |

| *        |      | 32ピン・プラスチッ        | ホスト/ファン | А               | R5F10JBCAFP | #V0, #X0, #10, #50, | PLQP0032GB-A |

|          |      | クLQFP             | クション機能  | G               | R5F10JBCGFP | #70                 |              |

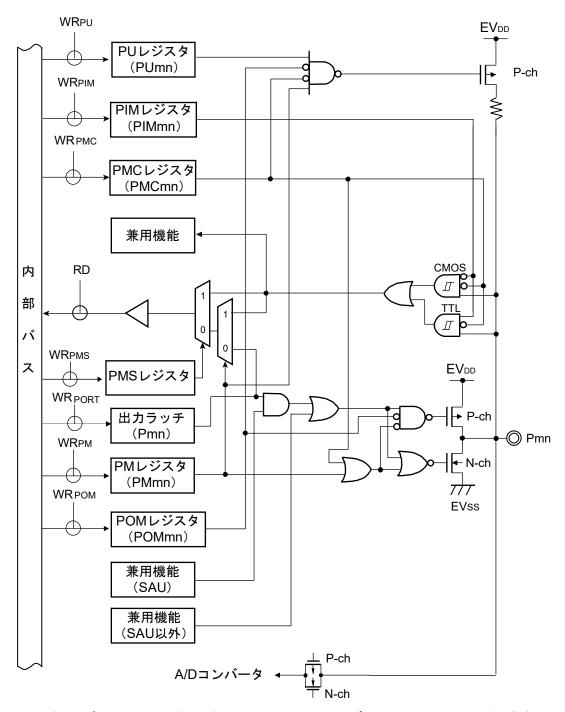

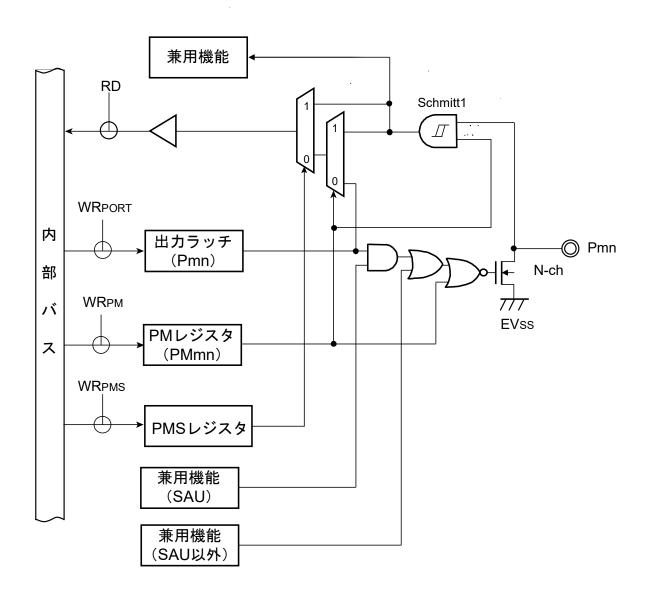

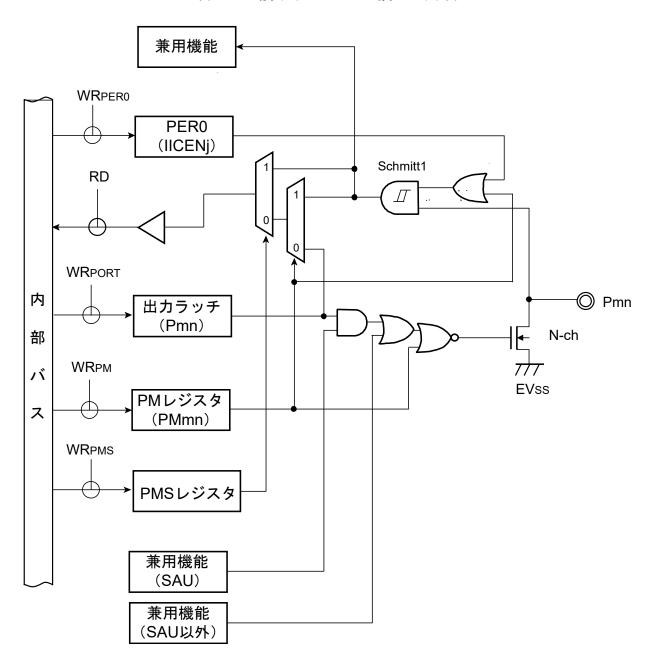

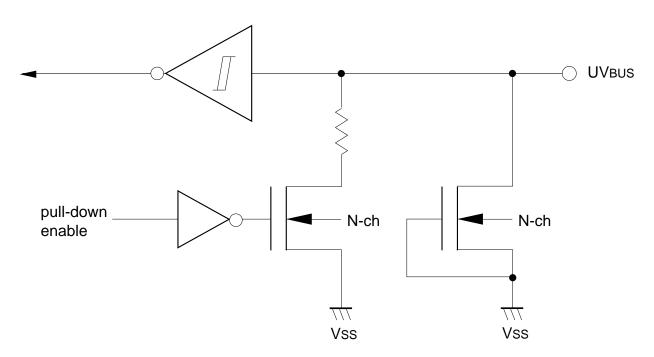

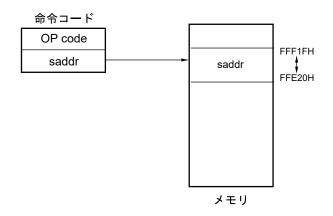

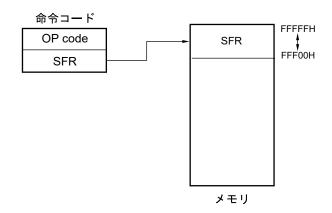

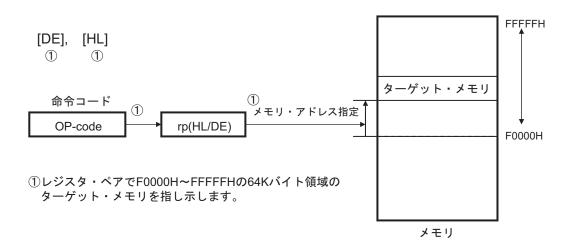

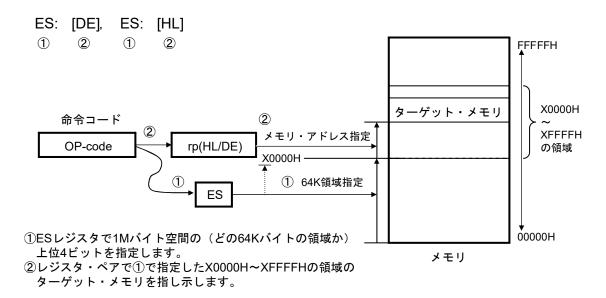

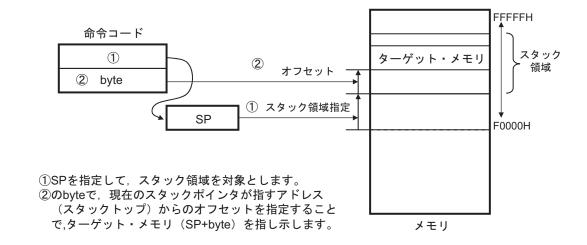

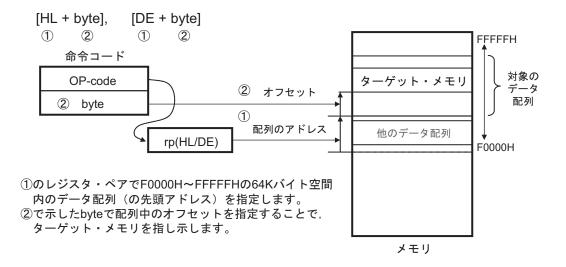

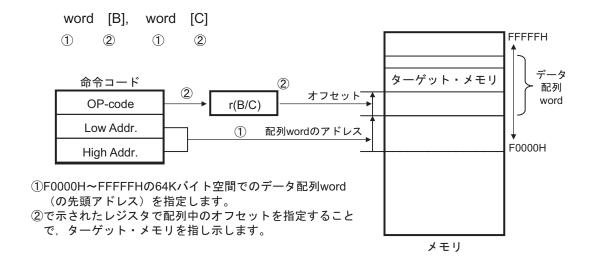

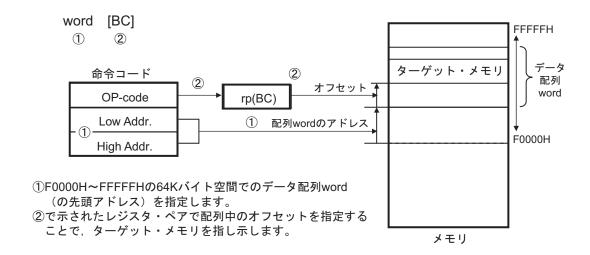

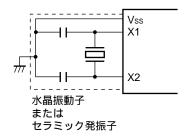

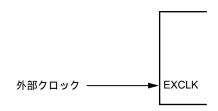

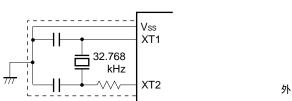

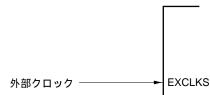

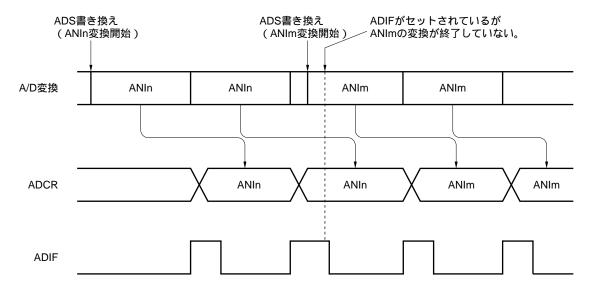

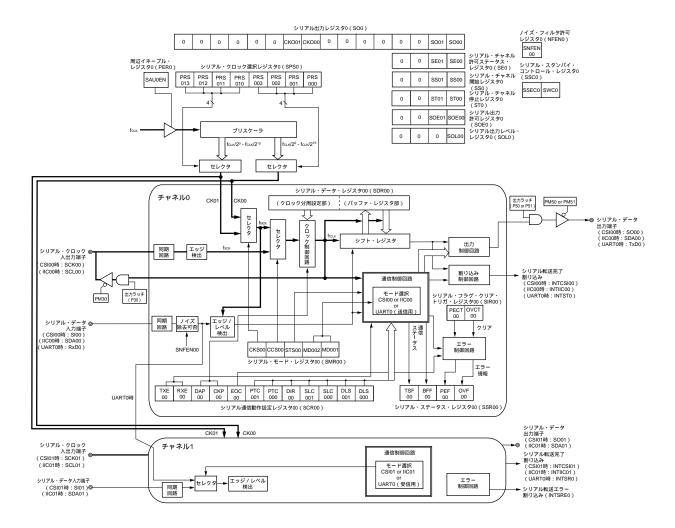

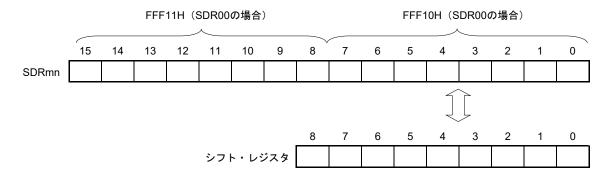

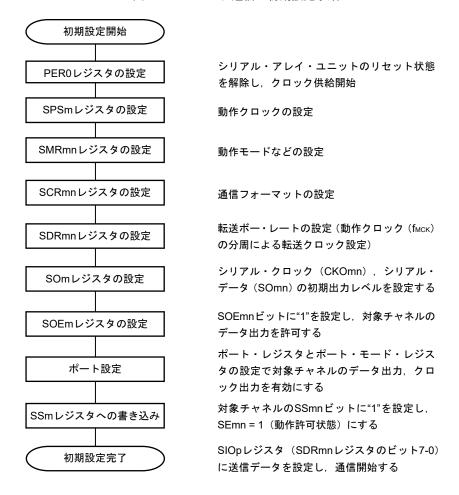

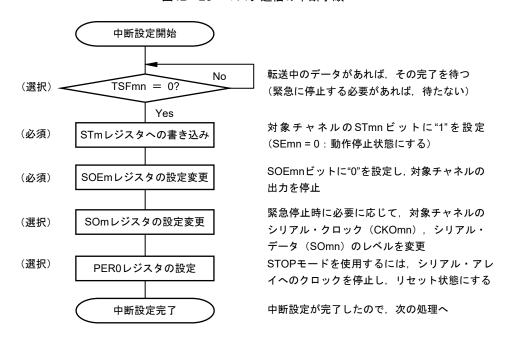

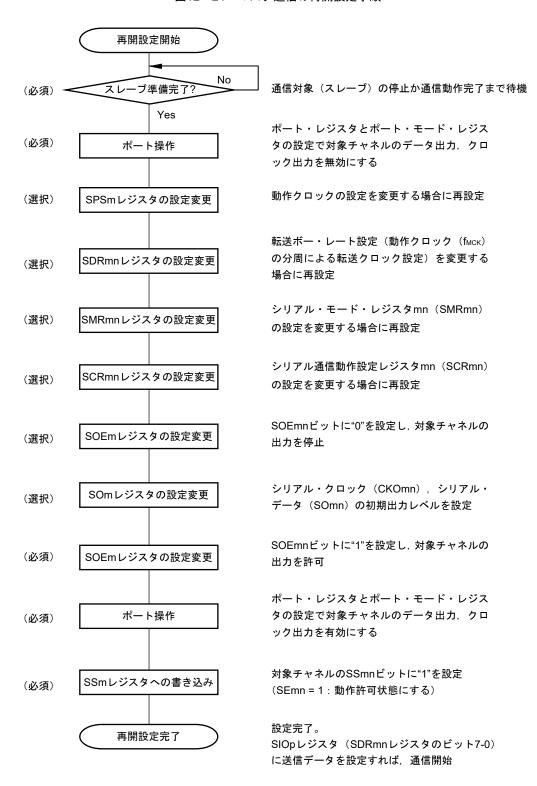

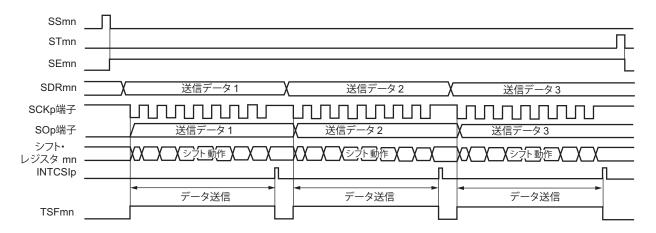

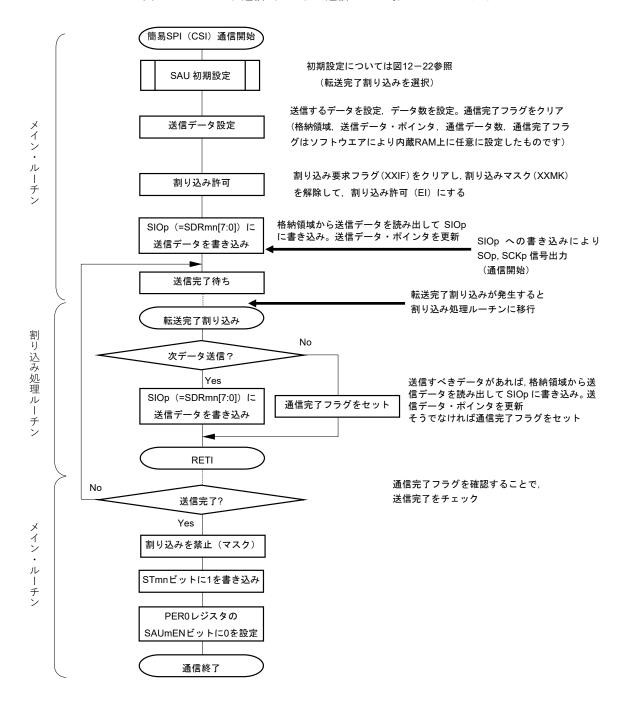

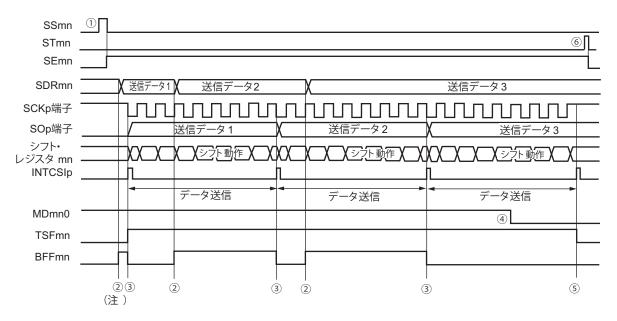

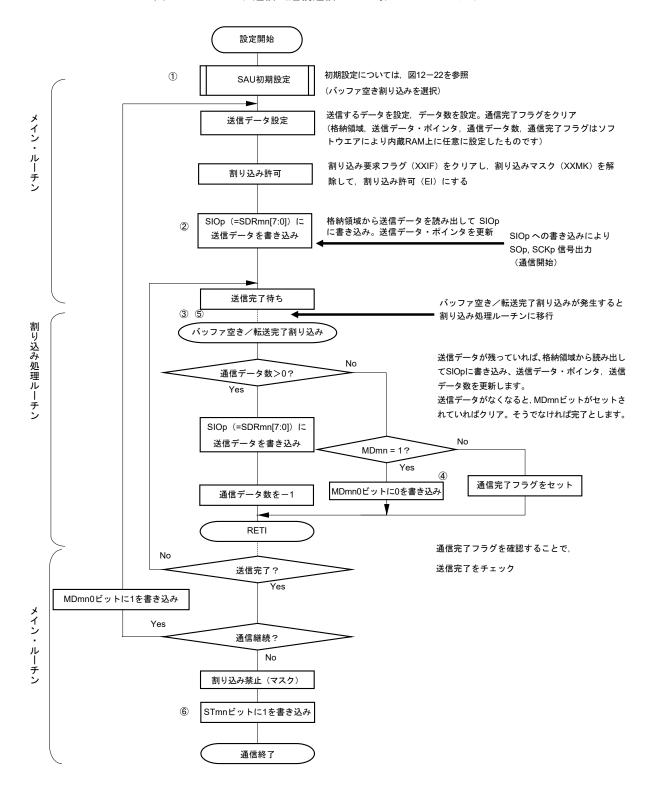

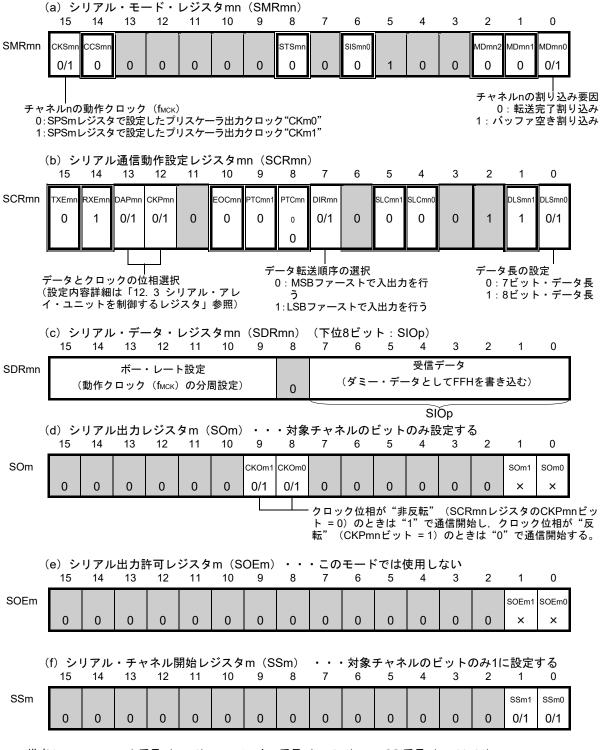

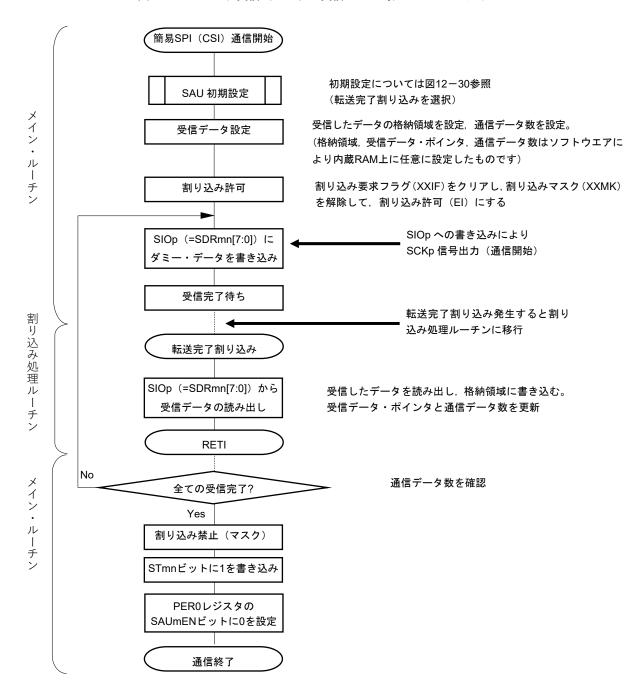

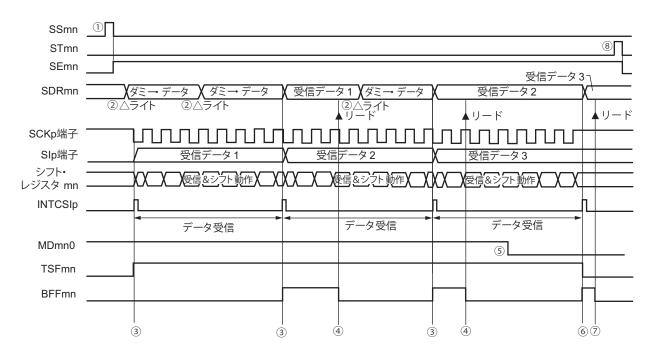

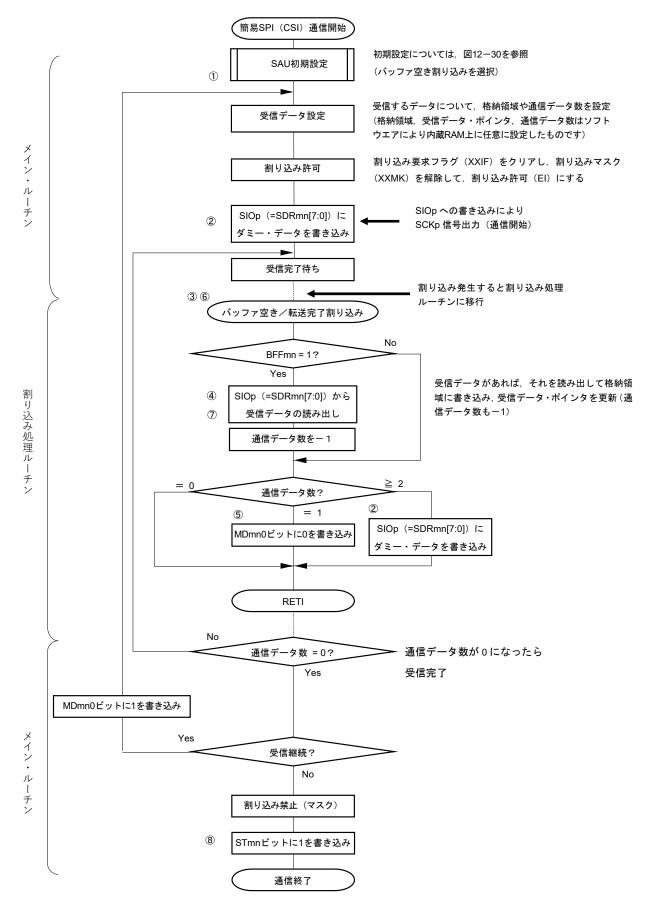

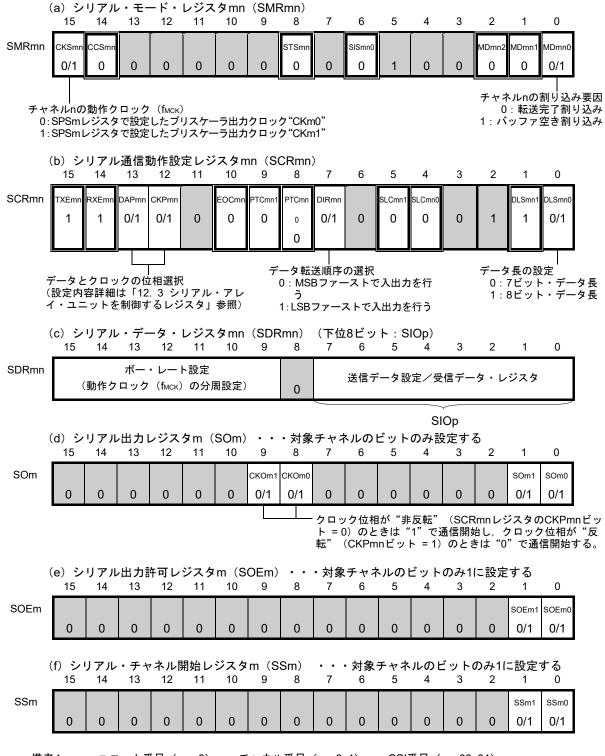

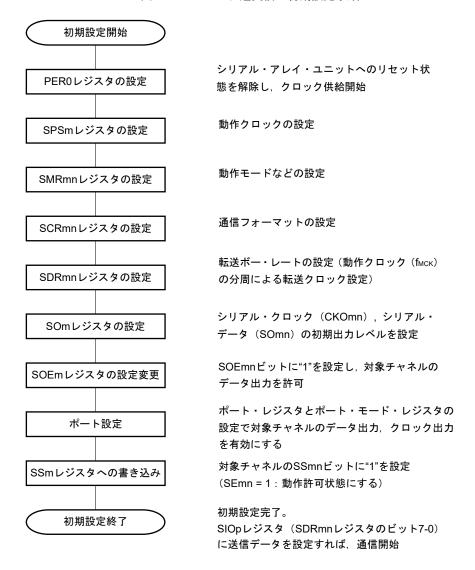

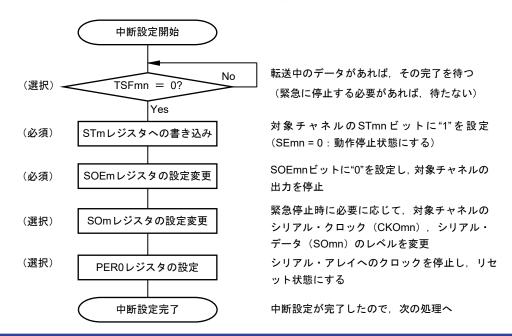

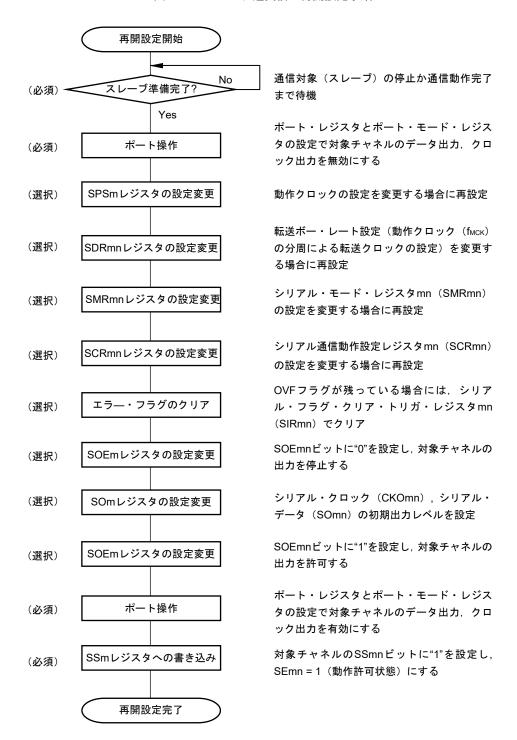

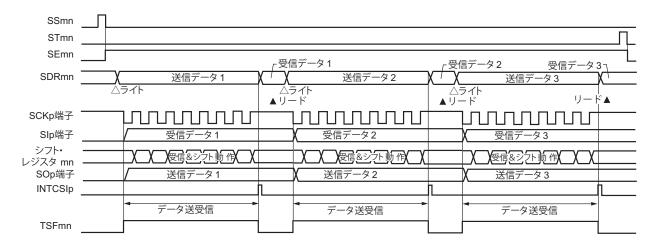

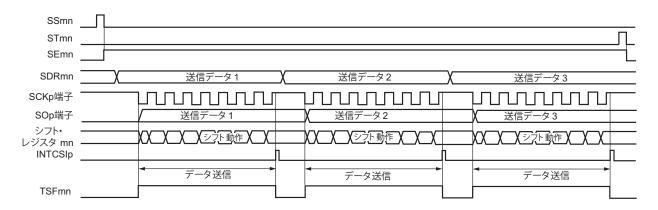

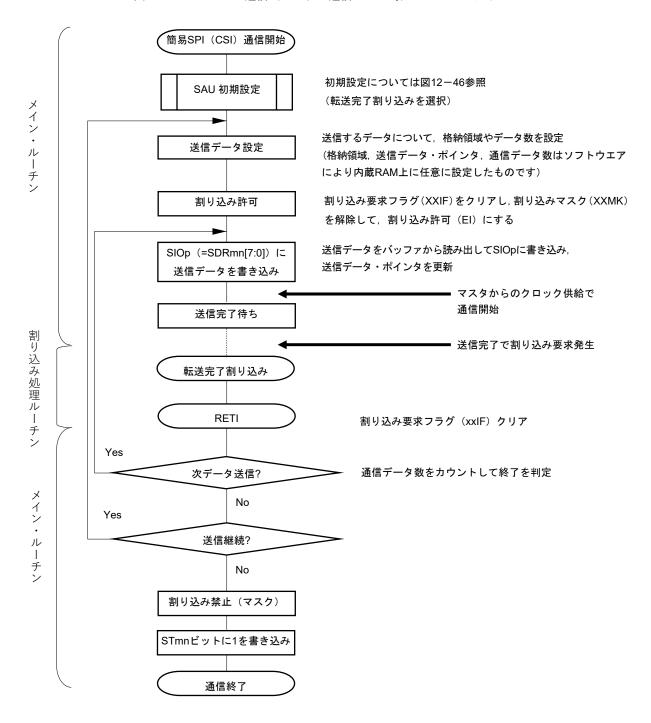

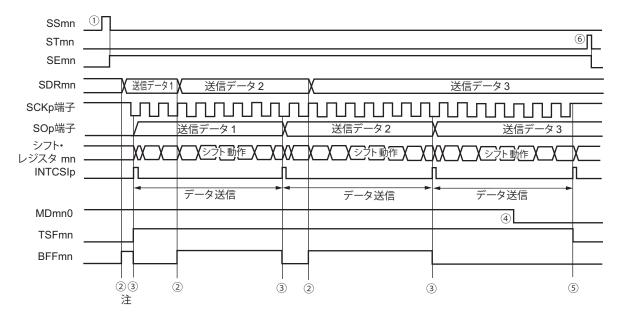

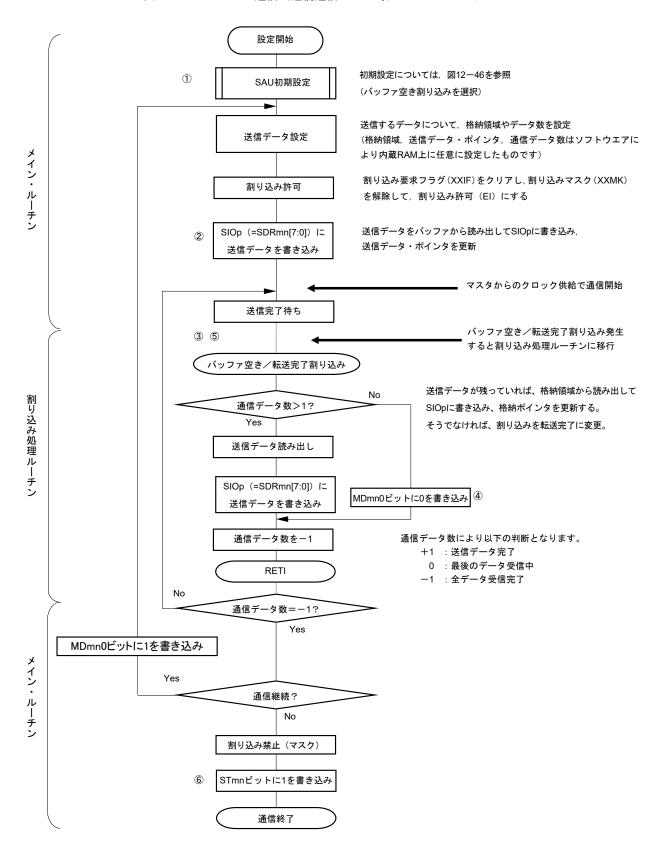

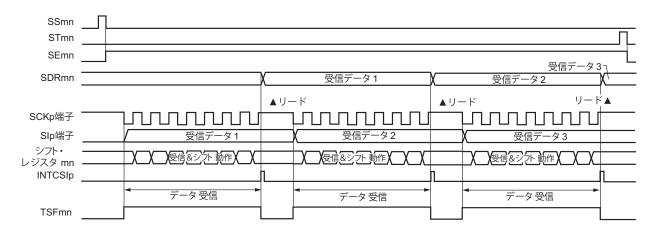

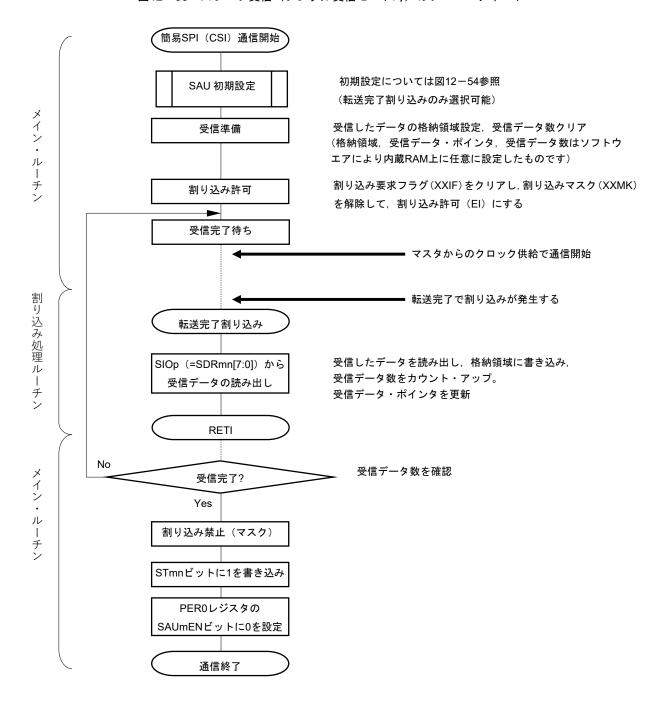

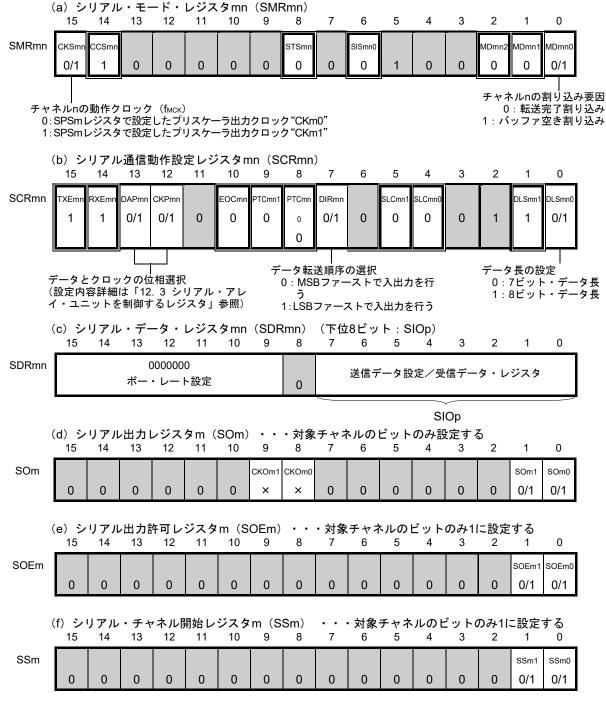

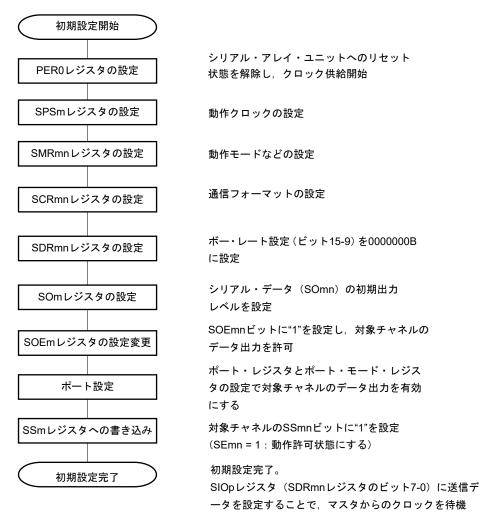

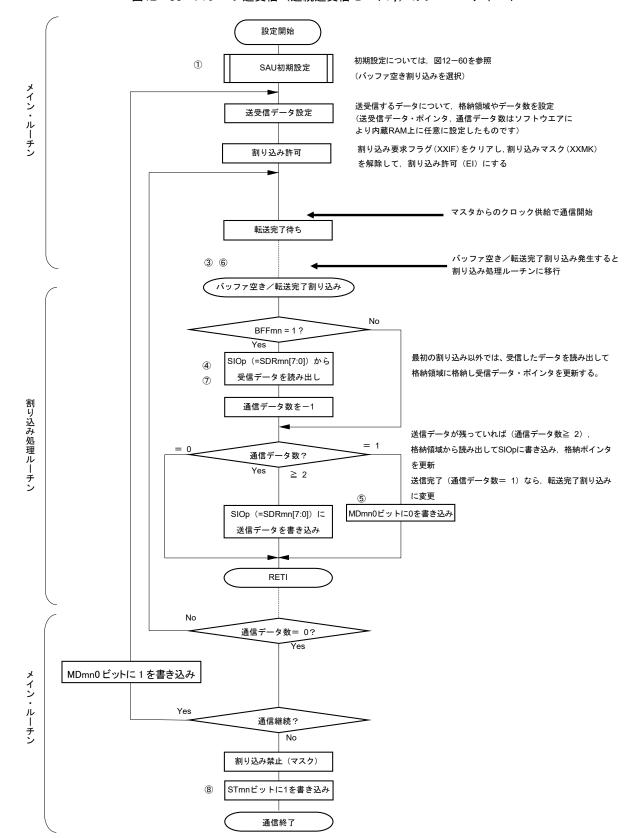

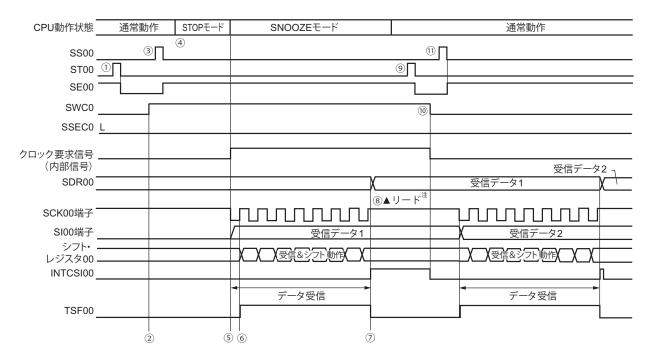

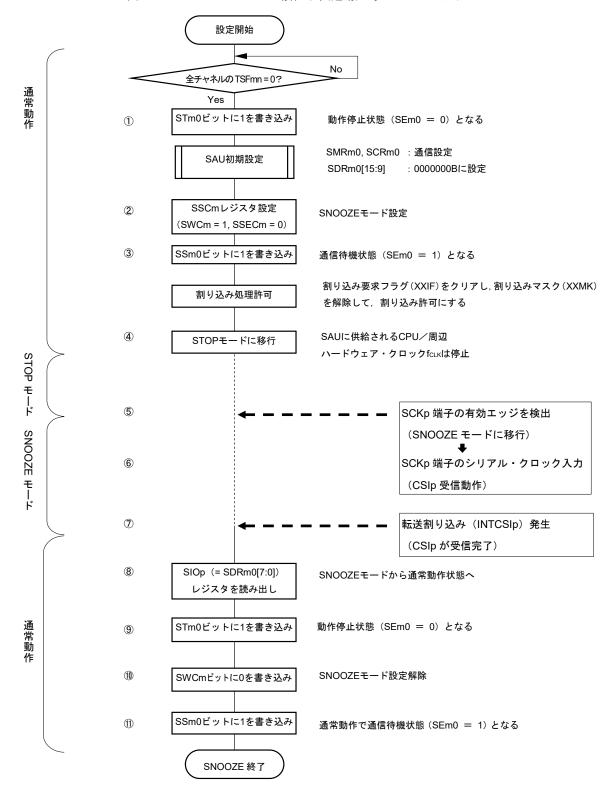

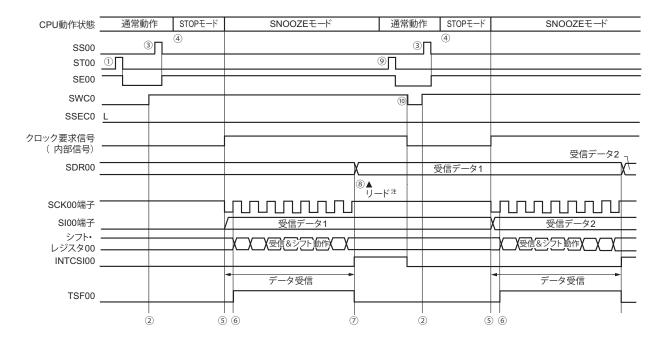

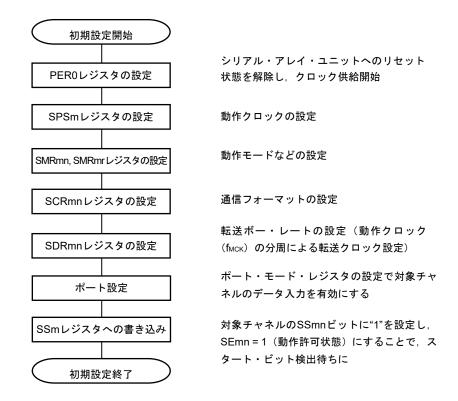

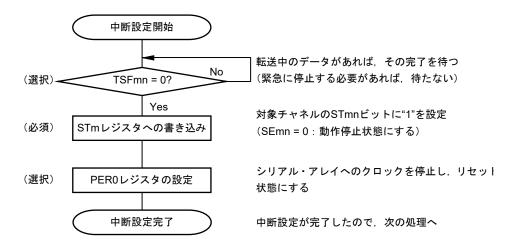

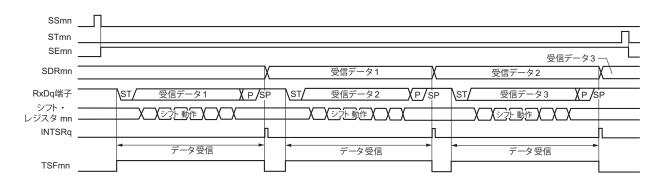

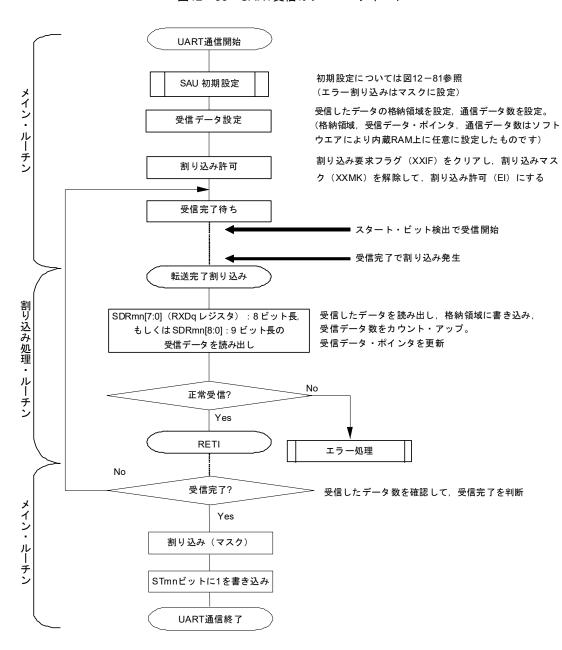

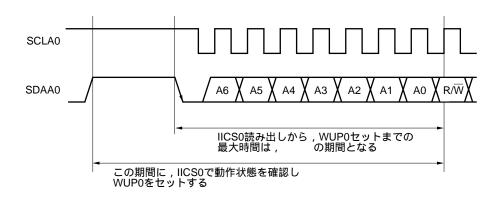

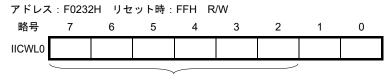

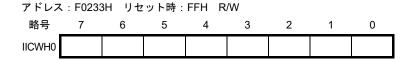

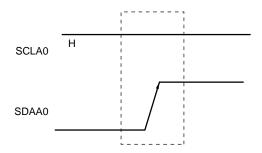

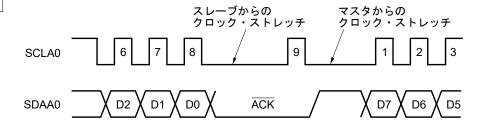

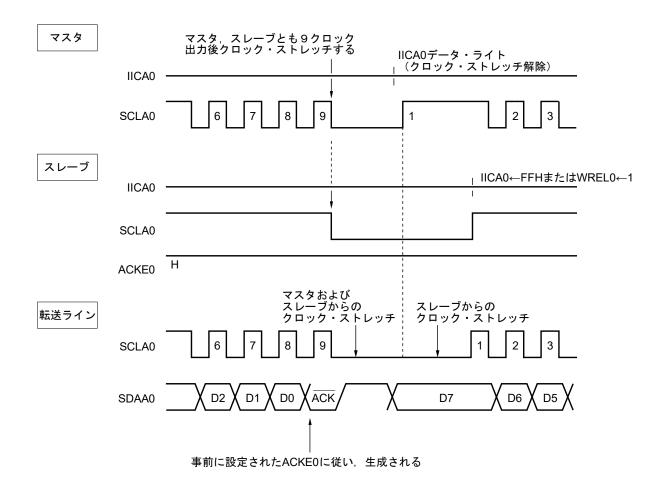

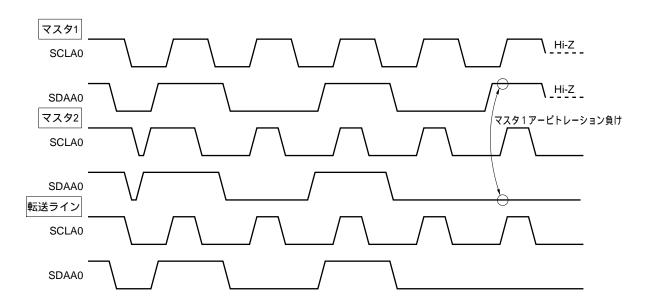

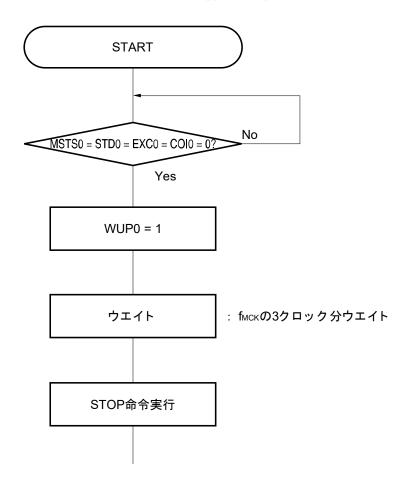

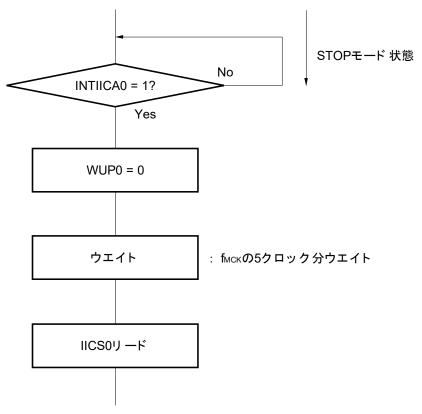

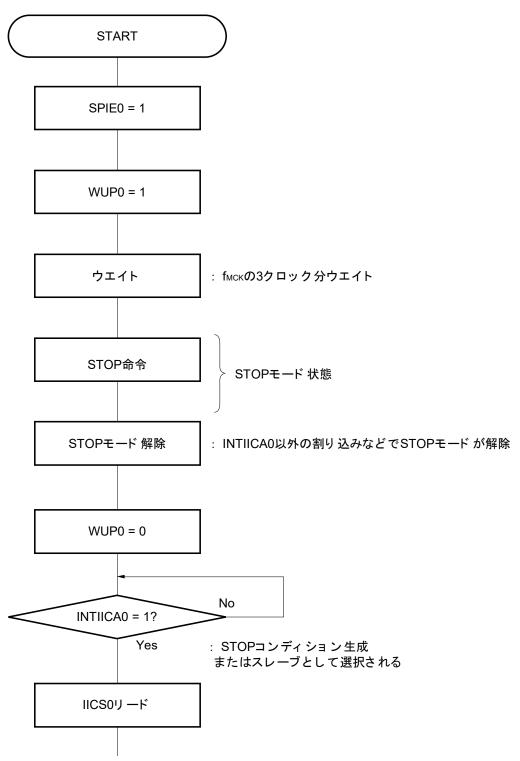

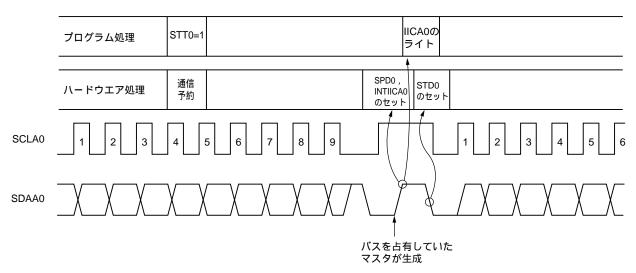

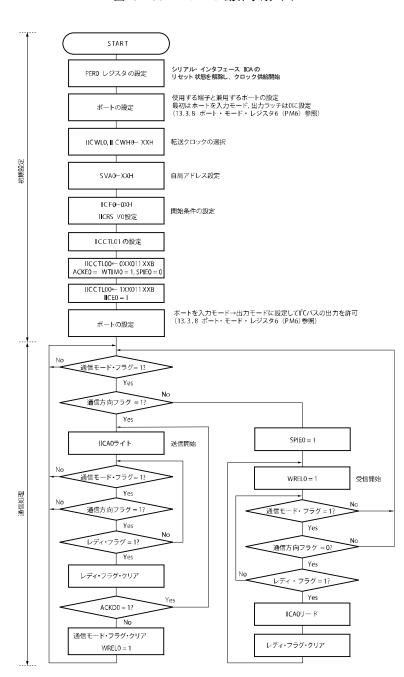

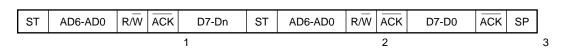

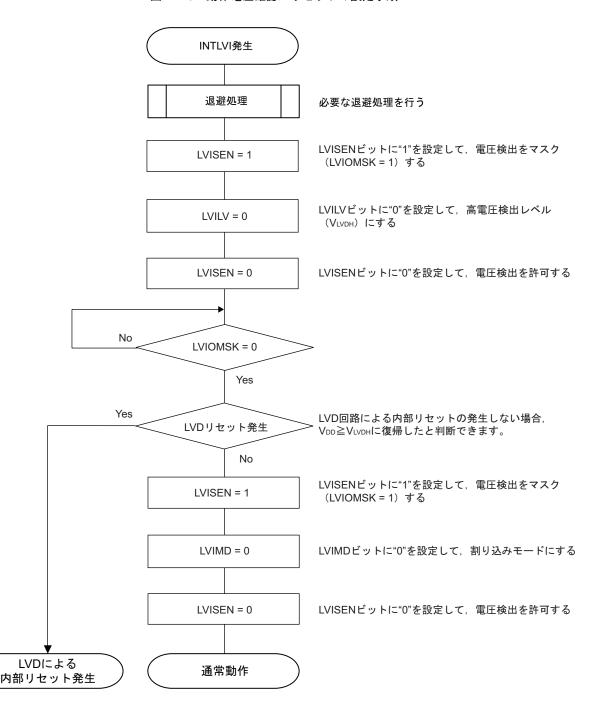

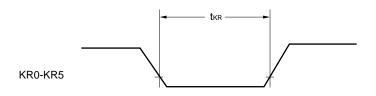

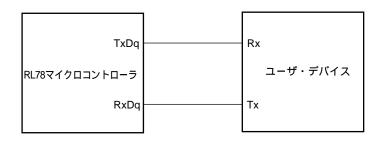

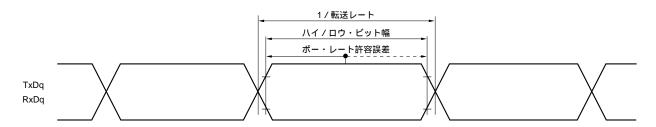

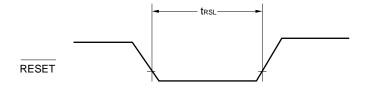

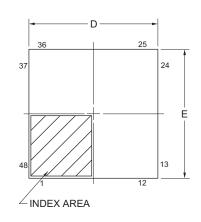

|          |      | (7 x 7 mm, 0.5 mm | ファンクション | Α               | R5F10KBCAFP |                     |              |