#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

### RA78K/ I ASSEMBLER PACKAGE USER'S MANUAL for LANGUAGE

**NEC Corporation**

#### Errata

The followings are corrections in the RA78K/I Assembler Package User's Manual for Language:

| Page                   | For                         | Read                      |

|------------------------|-----------------------------|---------------------------|

| i,[Target Device]      | uPD78122,uPD78124,uPD78P124 | Expurgation               |

| iv,"Assembler related" | EEM-                        | EEU-1205                  |

| iv,"Debugger related"  | IE-78120-R ~ (PC-DOS) based | Expurgation               |

|                        | EEM-1047                    | Expurgation               |

| 1-14,Table 1-1         | PC-9800 series              | IBM PC                    |

|                        | MS-DOS                      | PC-DOS                    |

| A-15~17                | Table C-2                   | Expurgation               |

| A-18,line 3~4          | For the uPD78122 ~          | Expurgation               |

|                        | to read as "addr16"         |                           |

| A-28,Last              | 0 <u>110</u> 0 <u>001</u>   | 0 <u>001</u> 0 <u>110</u> |

|                        | A register                  | L register                |

|                        | L register                  | A register                |

## RA78K/ I ASSEMBLER PACKAGE USER'S MANUAL for LANGUAGE

**NEC Corporation**

#### INTRODUCTION

Phase-out/Discontinued

This manual is designed to facilitate correct understanding of the basic functions of each program in the RA78K/I Assembler Package (hereinafter referred to as "this package or the package") and the methods of describing source programs for the RA78K/I. This manual does not cover how to operate the respective programs of the RA78K/I assembler package. Therefore, after you have comprehended the contents of this manual, read the RA78K/I Assembler Package User's Manual for Operation (hereinafter referred to as "the Operation Manual") to operate each program in the assembler package.

This manual is applicable to the package product versions V2.0 and upwards of the RA78K/I assembler package.

[Target Devices]

The software of the following microcomputers can be developed with this package:

- o uPD78112, uPD78P112

- o uPD78122, uPD78124, uPD78P124

[Readers of Manual]

Although this manual is intended for those who are familiar with the functions and instructions of the microcomputer subject to software development, the manual can also be used by those who use an assembler program for the first time.

[Organization of Manual] This manual consists of the following six chapters and appendixes:

Chapter 1 - General Outlines the functions of this package including the role of the package in microcomputer development.

Chapter 2 - How to Describe Source Programs Describes the general rules applicable to the description of a source program such as the basic configuration and description format of source programs, and expressions and operators of the assembler.

Chapters 3 & 4 Directives and Control Instructions Details the description format, function, and use of each of the assembler directives and control instructions, including application examples.

Chapter 5 - Macros Outlines macro functions such as macrodefintion, macro reference (macrocall), and macroexpansion. Macro directives are explained in Chapter 3.

Chapter 6 - Product Utilization Introduces some measures recommended for effective utilization of this package.

#### Appendixes

Contain a list of instructions (uCOM-78K/I), a list of directives and control instructions, a list of reserved words, a list of hints on use and restrictions, etc.

NOTE: The uCOM-78K/I instruction set is not detailed in this manual. For these instructions, refer to the user's manual of each microcomputer subject to software development.

Phase-out/Discontinued [Recommended Usage of Manual] For those who use an assembler for the first time: Read from Chapter 1, General of this manual. For those who have a general understanding of assembler programs: You may skip Chapter 1, General of this manual. (However, it is advisable to read Section 1.3, "Reminders Before Program Development".) Source programs for the uCOM-78K/I can be described in several different ways. Be sure to read Chapter 2, "How to Describe Source Programs". For those which wish to know the directives and control instructions of the assembler: Read Chapters 3 and 4, respectively, because the format, function, use, and application examples of each directive or control instruction are detailed in these chapters. The uCOM-78K/I instructions are listed in the respective appendixes. Use the lists for quick reference.

[Symbols and Abbreviations] The following symbols and abbreviations are used in this manual:

| Symbol           | Meaning                                              |

|------------------|------------------------------------------------------|

| • • •            | Continuation (repetition) of data in the same format |

| []               | Parameter(s) in brackets can be omitted.             |

| ** **            | Characters enclosed in " " (double quotes) must be   |

|                  | input as is.                                         |

| ( )              | Characters enclosed in parentheses must be input     |

|                  | as is.                                               |

| <                | Characters enclosed in < > must be input as is       |

|                  | (or indicates a title).                              |

| <u></u>          | Important point                                      |

| ц.               | One or more blanks (spaces) must be input:           |

| $\bigtriangleup$ | Indicates one blank (space).                         |

| •<br>•           | This part of the program description is omitted.     |

[References]

The documents related to this manual are shown below.

| Document name                                                        | Document No. |

|----------------------------------------------------------------------|--------------|

| o Assembler related                                                  | Doodone Not  |

| RA78K/I Assembler Package User's Manual                              | EEM-         |

| for Operation - PC-9800 series (MS-DOS)                              |              |

| and IBM PC (PC-DOS) based                                            |              |

| o Debugger related                                                   | 2            |

| IE-78112-R User's Manual Volume I - Hardware                         | EEP-1026     |

| IE-78112-R User's Manual Volume II - Software                        | EEM-1023     |

| IE-78112-R System Software Operation Manual<br>IBM PC (PC-DOS) based | EEM-1028     |

| IE-78120-R System Software User's Manual<br>IBM PC (PC-DOS) based    | EEM-1047     |

|                                                                      | 1            |

| o Device related                                                     | ``           |

| uPD78112 User's Manual                                               | IEM-1136     |

| Product Catalog for D78112CW/GF                                      | IP-1091      |

|                                                                      |              |

NOTE: Contact your nearest NEC dealer for the latest information on the reference documentation.

\*MS-DOS<sup>TM</sup> is a trademark of Microsoft Corp. \*\*IBM  $PC^{TM}$  and PC-DOS<sup>TM</sup> are trademarks of IBM Corp.

#### TABLE OF CONTENTS

|      |                                                   | Page  |

|------|---------------------------------------------------|-------|

| CHAI | PTER 1 GENERAL                                    | 1 – 1 |

| 1.1  | Assembler Overview                                | 1-1   |

|      | 1.1.1 What is an assembler?                       | 1 – 1 |

|      | 1.1.2 What is a relocatable assembler?            | 1-6   |

| 1.2  | Functional Outline of Assembler Package           | 1-9   |

|      | 1.2.1 Creation of source module file with editor  | 1-10  |

|      | 1.2.2 Assembler                                   | 1-11  |

|      | 1.2.3 Linker                                      | 1-12  |

|      | 1.2.4 Locater                                     | 1-13  |

| 1.3  | Reminders Before Program Development              | 1-14  |

|      | 1.3.1 Size of source module file                  | 1-14  |

|      | 1.3.2 Number of files that can be input to Linker | 1-14  |

|      | 1.3.3 Restriction on number of symbols            | 1-14  |

|      | 1.3.4 Maximum performance characteristics of      |       |

|      | assembler package                                 | 1-15  |

| 1.4  | Features of Assembler Package                     | 1-16  |

|      |                                                   |       |

| CHAI | PTER 2 HOW TO DESCRIBE SOURCE PROGRAMS            | 2-1   |

| 2.1  | Basic Configuration of Source Program             | 2-1   |

|      | 2.1.1 Module header                               |       |

|      | 2.1.2 Module body                                 | 2-3   |

|      | 2.1.3 Module tail                                 | 2-3   |

|      | 2.1.4 Overall configuration of source program     | 2-4   |

|      | 2.1.5 Description example of source program       | 2-5   |

| 2.2  | Description Format of Source Program              |       |

|      | 2.2.1 Configuration of statement                  |       |

|      | 2.2.2 Character set                               |       |

|      | 2.2.3 Fields of statement                         |       |

| 2.3  | Expressions and Operators                         |       |

|      | 2.3.1 Functions of operators                      |       |

|      | 2.3.2 Restrictions on Operations                  |       |

| 2.4  | Characteristics of Operands                       |       |

|      | 2.4.1 Size and address range of operand value     | 2-49  |

|      | 2.4.2 Symbol attributes and relocation            | 0 - 1 |

|      | attributes of operands                            | 2-51  |

.

| CHAPTER 3 DIRECTIVES                                    |          |

|---------------------------------------------------------|----------|

| 3.1 Overview of Directives                              |          |

| 3.2 Directives for Segment Definition                   |          |

| (1) CSEG                                                |          |

| (2) DSEG                                                |          |

| (3) BSEG                                                | 3-16     |

| (4) ORG                                                 | 3-20     |

| (5) ENDS                                                | 3-24     |

| 3.3 Directives for Symbol Definition                    | 3-26     |

| (1) EQU                                                 | 3-27     |

| (2) SET                                                 | 3-34     |

| 3.4 Directives for Memory Initialization and            |          |

| Area Reservation                                        | 3-36     |

| (1) DB                                                  | 3-37     |

| (2) DW                                                  | 3-39     |

| (3) DS                                                  | 3-42     |

| (4) DBIT                                                | 3-44     |

| 3.5 Directives for Linkage                              | 3-46     |

| (1) EXTRN                                               | 3-48     |

| (2) EXTBIT                                              | 3-50     |

| (3) PUBLIC                                              | 3-52     |

| (4) NAME                                                | ••• 3-54 |

| 3.6 Directive for Automatic Selection of BR Instruction | 3-56     |

| (1) BR                                                  | 3-57     |

| 3.7 Macro Directives                                    | 3-61     |

| (1) MACRO                                               | 3-62     |

| (2) LOCAL                                               | 3-64     |

| (3) REPT                                                | 3-67     |

| (4) IRP                                                 | 3-70     |

| (5) EXITM                                               | 3-73     |

| (6) ENDM                                                | 3-77     |

| 3.8 Directive for Assembly Termination                  | 3-79     |

| (1)                                                     |          |

|                                                         |          |

| CHAPTER 4 CONTROL INSTRUCTIONS                    |                 | 4 – 1 |

|---------------------------------------------------|-----------------|-------|

| 4.1 Overview of Control Instructions              | • • • • • • • • | 4-1   |

| 4.2 INCLUDE Control Instruction                   |                 | 4-2   |

| (1) INCLUDE                                       |                 | 4-3   |

| 4.3 Assembly List Control Instructions            |                 | 4-5   |

| (1) EJECT                                         |                 | 4-6   |

| (2) NOLIST                                        |                 | 4-8   |

| (3) LIST                                          |                 | 4-10  |

| (4) SUBTITLE                                      |                 | 4-12  |

|                                                   |                 |       |

| 4.4 Control Instructions for Conditional Assembly | • • • • • • • • | 4-16  |

| (1) IF, ELSEIF, ELSE, ENDIF                       |                 | 4-17  |

| (2) SET, RESET                                    |                 | 4-24  |

|                                                   |                 |       |

| CHAPTER 5 MACROS                                  |                 | 5-1   |

| 5.1 Overview of Macro                             |                 | 5-1   |

| 5.2 Utilization of Macros                         |                 | 5-3   |

| 5.2.1 Macrodefinition                             |                 | 5-3   |

| 5.2.2 Macro reference                             |                 | 5-4   |

| 5.2.3 Macroexpansion                              |                 | 5-5   |

| 5.3 Symbols within Macro                          |                 | 5-7   |

|                                                   |                 |       |

| CHAPTER 6. PRODUCT UTILIZATION                    |                 | 6-1   |

#### APPENDIXES

| APPENDIX A | LIST OF RESERVED WORDS              | A-1  |

|------------|-------------------------------------|------|

| APPENDIX B | LIST OF DIRECTIVES                  | A-4  |

| APPENDIX C | INSTRUCTION SET OF uCOM-78K/I       | A-7  |

| APP C-1.   | Instruction Set and Its Operation   | A-7  |

| APP C-2.   | Instruction Codes                   | A-27 |

| APPENDIX D | MAXIMUM PERFORMANCE CHARACTERISTICS | A-36 |

INDEX

.

#### ILLUSTRATIONS AND TABLES

.

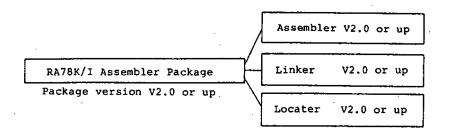

| Fig. 1-1. | Assembler Package 1-1                                 |

|-----------|-------------------------------------------------------|

| Fig. 1-2. | Flow of Assembler 1-2                                 |

| Fig. 1-3. | Development Process of Microcomputer-applied          |

|           | Product 1-3                                           |

| Fig. 1-4. | Software Development Process                          |

| Fig. 1-5. | Assembly Phase by This Package                        |

| Fig. 1-6. | Re-assembly for Debugging 1-7                         |

| Fig. 1-7. | Program Development Utilizing Existing Modules 1-8    |

| Fig. 1-8. | Program Development Procedure with This Package 1-9   |

| Fig. 1-9. | Creation of Source Module File                        |

| Fig. 1-10 | . Functions of Assembler 1-11                         |

| Fig. 1-11 | . Functions of Linker 1-12                            |

| Fig. 1-12 | Functions of Locater 1-13                             |

| Fig. 2-1. | Configuration of Source Module                        |

| Fig. 2-2. | Overall Configuration of Source Program               |

| Fig. 2-3. | Examples of Source Module Configurations 2-5          |

| Fig. 2-4. | Configuration of Sample Program                       |

| Fig. 2-5. | Fields That Make Up A Statement                       |

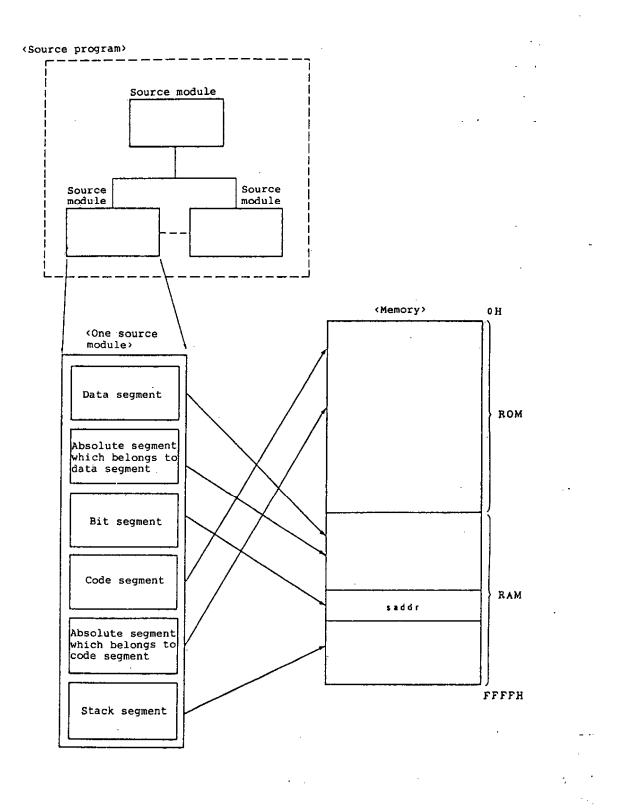

| Fig. 3-1. | Memory Allocation to Segments                         |

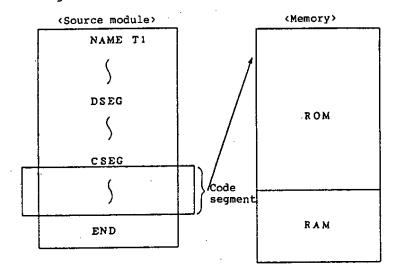

| Fig. 3-2. | Relocation of Code Segment                            |

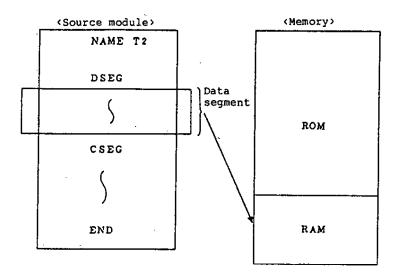

| Fig. 3-3. | Relocation of Data Segment                            |

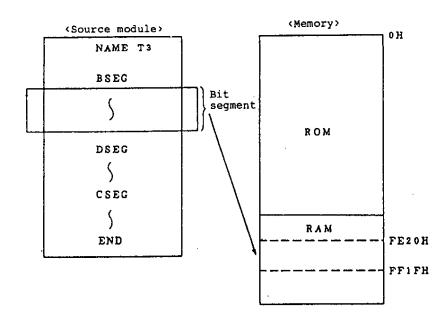

| Fig. 3-4. | Relocation of Bit Segment 3-15                        |

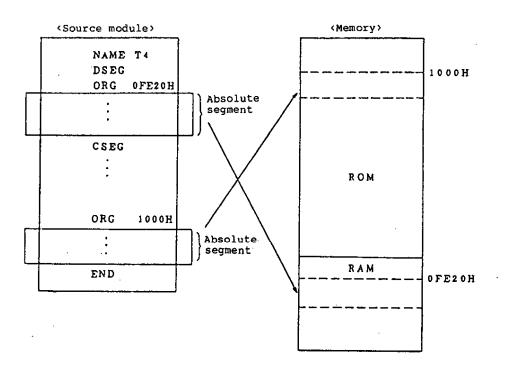

| Fig. 3-5. | Relocation of Absolute Segment                        |

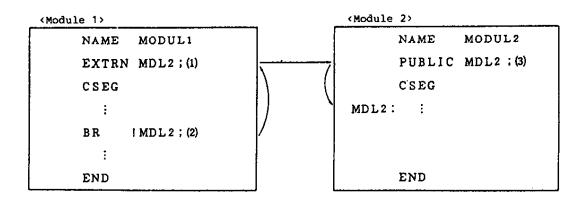

| Fig. 3-6. | Relationship of Symbols between Two Modules 3-46      |

|           |                                                       |

| Table 1-1 | . Size of Source Module File 1-14                     |

| Table 2-1 | . Items That Can Be Described in Module Header 2-2    |

| Table 2-2 | . Symbol Types 2-13                                   |

| Table 2-3 | . Types of Symbol Attributes 2-15                     |

| Table 2-4 | • Methods of Representing Numeric Constant Types 2-18 |

| Table 2-5 | . Special Characters That Can Be Described in         |

|           | Operand Field 2-20                                    |

| Table 2-6 | . Types of Operators 2-24                             |

| Table 2-7 | . Order of Precedence of Operators 2-24               |

| Table 2-8 | . Types of Relocation Attributes 2-43                 |

| Table 2-9 | . Combinations of Operators and Terms by Relocation   |

|           | Attribute 2-44                                        |

| able  | 2-10. | Combinations of Operators and Terms by         |      |

|-------|-------|------------------------------------------------|------|

|       |       | Relocation Attribute (External Reference Term) | 2-45 |

| able  | 2-11. | Types of Symbol Attributes                     | 2-46 |

| 'able | 2-12. | Combinations of Operators and Terms by Symbol  | 2-47 |

| 'able | 2-13. | Conditions for Size of Operand Value           | 2-50 |

| 'able | 2-14. | Conditions for Address Range of Operand Value  | 2-51 |

| 'able | 2-15. | Operand Attributes of Instructions             | 2-53 |

| Table | 3-1.  | List of Directives                             | 3-1  |

| Table | 3-2.  | Segment Definition Methods and Memory Address  |      |

|       |       | Allocation                                     | 3-3  |

| Table | 3-3.  | Functions of Relocation Attributes             | 3-6  |

| Table | 3-4.  | Uses of Relocation Attributes                  | 3-6  |

| Table | 3-5.  | Default Segment Names of Code Segments         | 3-7  |

| Table | 3-6.  | Representation Formats of Operands             |      |

|       |       | Indicating Bit Values                          | 3-28 |

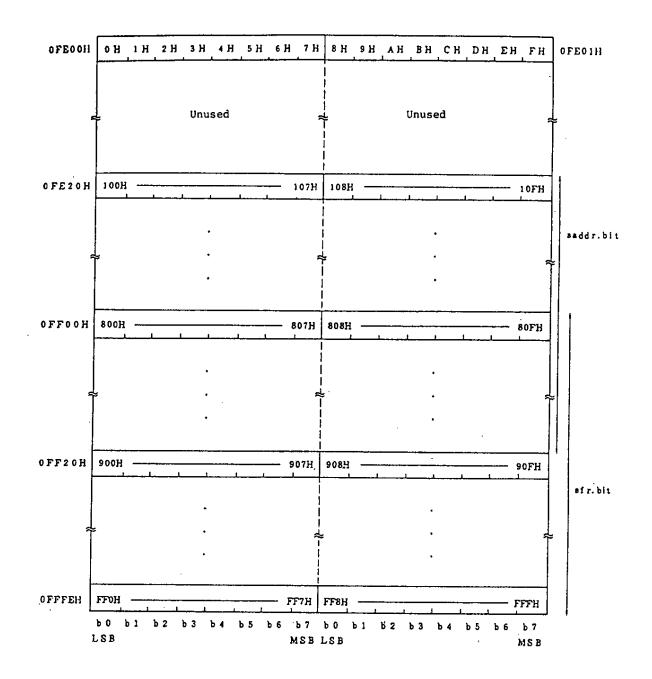

| Table | 3-7.  | Bit Address Map                                | 3-33 |

| Table | 3-8.  | Bit Value That Can Be Described as Operand     |      |

|       |       | of EXTBIT                                      | 3-59 |

| Table | 3-9.  | Optimization Conditions of BR Directive        | 3-59 |

| Table | 4-1.  | List of Control Instructions                   | 4–1  |

1.1 Assembler Overview

The RA78K/I Assembler Package is a series of programs designed to translate a source program coded in the assembly language of the uCOM-78K/I series microprocessors, into machine language coding.

The assembler package contains three programs: Assembler, Linker, and Locater.

#### 1.1.1 What is an assembler?

(1) Assembly language and machine language An assembly language is the most fundamental programming

language for microprocessors.

To have a microprocessor do its job, programs and data are required. These programs and data must be written by a human being (i.e., a programmer) and stored in the memory section of a microcomputer. Programs and data that can be handled by the microcomputer is nothing but a set or combinations of binary numbers which is called machine language (i.e., the language that can be understood or interpreted by the computer). To create a program in machine language coding, namely, by a set of binary numbers is not an easy job for a human being, because it's difficult for him or her to remember the coding and he or she is likely to make errors in coding. For this reason, there is a method of creating a program using an abbreviated symbol (or mnemonic symbol) which represents the meaning of a machine language instruction to assist the human memory. A programming language system by this symbolic coding is called an assembly language.

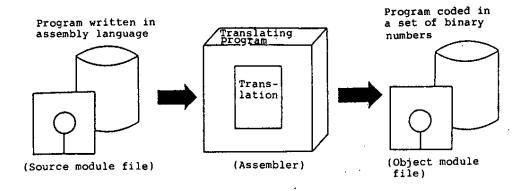

To translate a program created in the assembly language into a set of binary numbers that can be understood by the microprocessor, another program is required. This program is called an assembler.

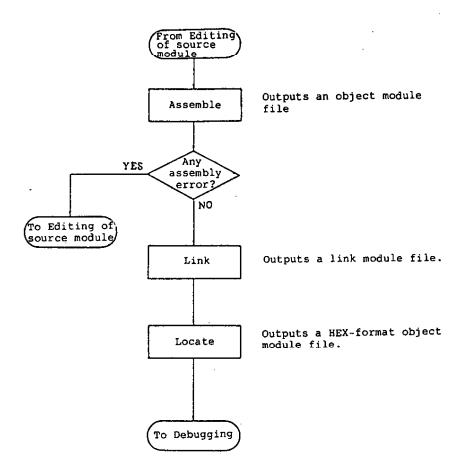

Fig. 1-2. Flow of Assembler

(2) Development of microcomputer-applied products and role of this package

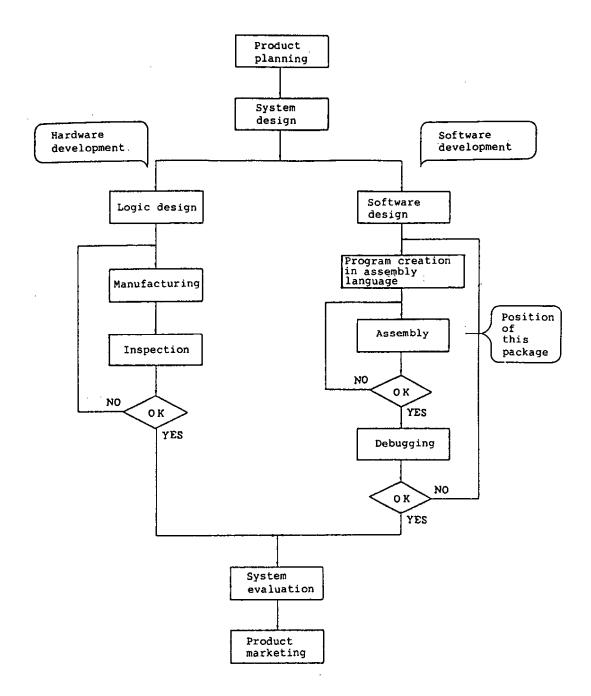

Fig. 1-3 illustrates the standing of the programming in assembly language in the development process of microcomputer-applied product.

Fig. 1-3 Development Process of Microcomputer-applied Product

The software development process will be further detailed in Fig. 1-4 on the next page.

Phase-out/Discontinued

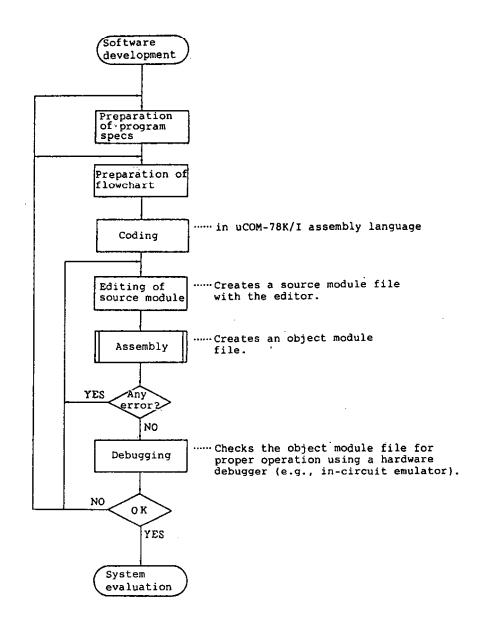

#### Fig. 1-4. Software Development Process

The assembly phase in the software development process will be reviewed in further detail by giving an example of this package.

#### 1.1.2 What is a relocatable assembler?

The machine language translated from a source language by the assembler will be stored in the memory of the microcomputer before use. In this case, in which memory location each machine language instruction will be stored must have been determined. Therefore, information on "the allocation of each machine language instruction to a specific address in memory" will be added to the machine language converted by the assembler.

Phase-out/Discontinued

Depending on the method of allocating addresses to machine language instructions, an assembler can be broadly divided into an absolute assembler and a relocatable assembler.

o Absolute assembler

Allocates the machine language instructions converted in one-time assembly operation to absolute addresses.

o Relocatable assembler

Addresses determined for the machine language instructions converted in one-time assembly operation are tentative. Absolute addresses will be determined by a program called the locater.

In the past, when a program was created with the absolute assembler, programmers had to, as a rule, complete programming at a time. However, if you create a large program at a time, the program becomes complicated, making analysis and maintenance of the program troublesome. To avoid this, such a large program is developed by dividing it into several subprograms (i.e., modules) for each functional unit. This programming technique is called the modular programming.

The relocatable assembler is an assembler suitable for modular programming. The following advantages can be derived from modular programming with the relocatable assembler:

(1) Increase in development efficiency

It's difficult to write a large program at a time. In such a case, divide the program into modules for each function and the program can be developed with two or more programmers engaged in writing subprograms at the same time. This will certainly increase development efficiency of the program.

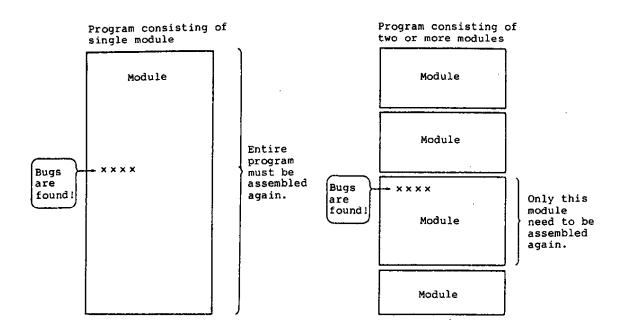

If any bugs are found in the program, you do not need to re-assemble the entire program just to correct part of the program. Only the subprogram (module) requiring correction(s) can be re-assembled. This will help shorten the debugging time.

#### Fig. 1-6. Re-assembly for Debugging

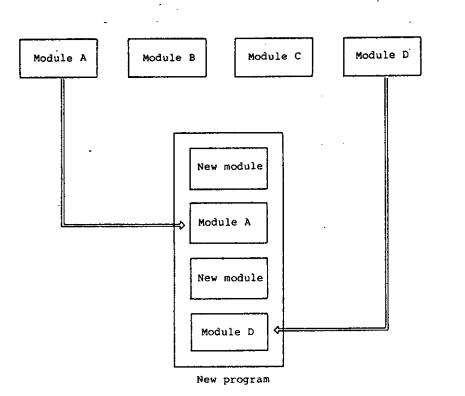

(2) Utilization of resources

Highly reliable, highly versatile modules which have been previously created can be utilized for creation of another program. If you accumulate such high-versatility modules as software resources, you can save time and labor in developing a new program.

Fig. 1-7. Program Development Utilizing Existing Modules

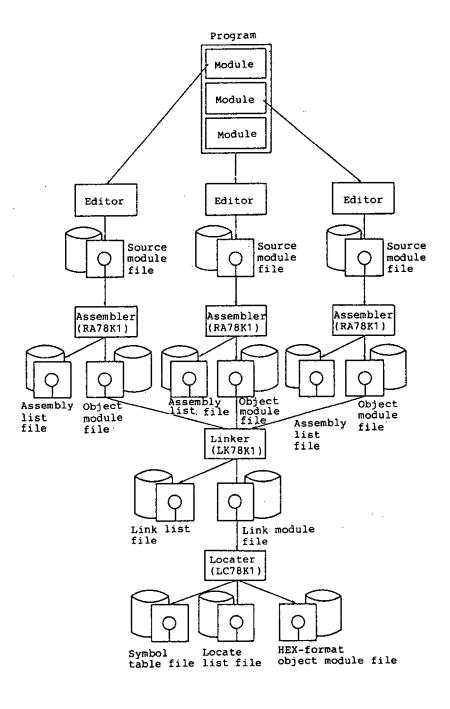

1.2 Functional Outline of Assembler Package An ordinary program development procedure with this assembler package is illustrated in Fig. 1-8. The development of a program is basically performed by using the assembler, linker, and locater.

Phase-out/Discontinued

In the following discussions, the assembler, linker, and locater programs are collectively referred to as "the assembler package or this package" and the assembler program, as "the assembler".

Fig. 1-8. Program Development Procedure with This Package

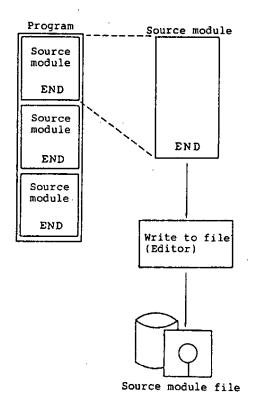

1.2.1 Creation of source module file with editor Devide one program functionally into several modules. Each module becomes the unit of coding as well as the unit of input to the assembler. A module serving as the unit of input to the assembler is called a source module. After coding each source module, the source module is written into a file with the editor. The file thus created is called a source module file.

The source module file becomes an input file to the assembler (RA78K1).

Fig. 1-9. Creation of Source Module File

#### 1.2.2 Assembler

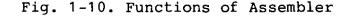

The assembler accepts source module files as input files and translates assembly language into machine language. If any coding error is found in the input source module, the assembler outputs an assembly error. If no assembly error is found, the assembler outputs an object module file which contains machine language information and relocation information relating to the allocation address of each machine language instruction. The assembler also outputs information at assembly time as an assembly list file.

Assembly list file

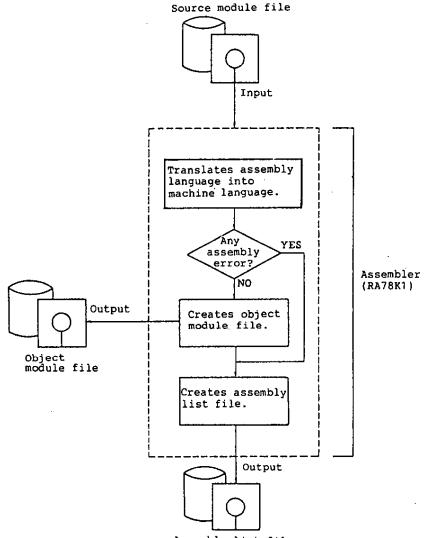

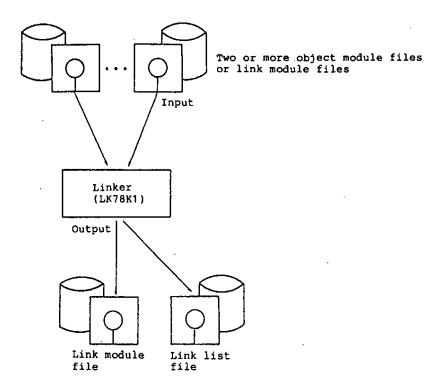

1.2.3 Linker

The linker accepts two or more object module files output by the assembler or link module file output by the linker itself as input files and gathers them for output as a single link module file. The linker also outputs information at link time as a link list file.

Phase-out/Discontinued

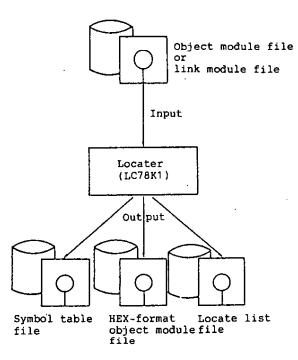

#### 1.2.4 Locater

The locater accepts the object module file output by the assembler or the link module file output by the linker as an input file and determines the addresses to be allocated to machine language instructions and outputs the result of the locate operation as a HEX-format object module file.

Phase-out/Discontinued

The locater also outputs the symbol information required in symbolic debugging with an in-circuit emulator as a symbol table file and the allocation address information at locate time as a locate list file.

Fig. 1-12. Functions of Locater

The processing of this package terminates when the processes up to the locater have been completed normally.

1.3 Reminders Before Program Development

Before you set your hand to the development of a program, keep in mind the following points:

1.3.1 Size of source module file

The size of a source module file that can be input to the assembler is limited to one of the following values depending on the operating (or execution) environment of the assembler.

Table 1-1. Size of Source Module File

| Host machine      | OS              | Size of source module   |

|-------------------|-----------------|-------------------------|

|                   |                 | file that can be input  |

| MD-086/116 series | Concurrent CP/M | 64K bytes max.          |

| PC-9800 series    | MS-DOS          | 64K bytes max.          |

|                   | CP/M-86         |                         |

| VAX-11 series     | VMS             | Approx. 850K bytes max. |

With a source module file having a size of 64K bytes, assuming that each line of the source module consists of an average of 30 characters, a program of up to about 2K steps can be assembled as a single source module file.

1.3.2 Number of files than can be input to Linker The number of object module files and/or link module files that can be input to the linker is 100.

1.3.3 Restriction on number of symbols The number of local symbols and that of PUBLIC symbols, which can be defined in the assembler, linker, and locater, respectively, are restricted as shown in the table below.

|           | Number of symbols      |                       |

|-----------|------------------------|-----------------------|

|           | No. of local symbols   | No. of PUBLIC symbols |

| Assembler | Approx. 1,800          | 256                   |

| Linker    | 1,800 x No. of modules | Approx. 2,000         |

| Locater   | 1,800 x No. of modules | Approx. 2,000         |

- NOTE: If any PUBLIC symbols have been defined, the number of local symbols that can be defined in the assembler must be reduced to the following value:

- No. of local symbols that can be used in Assembler = Approx. 1,800 - No. of PUBLIC symbols defined

1.3.4 Maximum performance characteristics of assembler package The maximum performance characteristics of the assembler package that should be kept in your mind before program development are listed in the following tables.

(1) Maximum performance characteristics of Assembler

| Item                          | Restriction    |

|-------------------------------|----------------|

| Symbol length                 | 6 characters   |

| No. of characters per line    | 99 characters  |

| No. of code segments per type | 1 segment      |

| No. of absolute segments      | 10 segments    |

| No. of macrodefinitions       | 10 definitions |

(2) Maximum performance characteristics of Linker

| Item                           | Restriction  |

|--------------------------------|--------------|

| No. of input module files      | 100 files    |

| No. of different segment names | 255 names    |

| No. of absolute segments       | 100 segments |

(3) Maximum performance characteristics of Locater

| Item                        | Restriction  |  |  |

|-----------------------------|--------------|--|--|

| No. of relocatable segments | 256 segments |  |  |

| in the input module         | 1            |  |  |

1.4 Features of Assembler Package

This package has the following features:

(1) Macro function

When the same group of instructions must be described in a source program over and over again, a macro can be defined by giving a single macro name to the group of instructions. By using this macro function, coding efficiency and readability of the program can be increased.

- (2) Optimize function of branch instructions The assembler package has an assembler directive to automatically select a branch instruction (i.e., BR directive). To create a program with high memory efficiency, a 2-byte branch instruction must be described according to the branch destination range of the branch instruction. However, it is troublesome for the programmer to describe a branch instruction by paying attention to the branch destination range for each branching. If the BR directive is described, the assembler generates the appropriate branch instruction according to the branch destination range. This is called the optimize function of branch instructions.

- (3) Conditional assembly function With this function, part of a source program can be specified for assembly or non-assembly according to a predetermined condition. If a debug statement is described in a source program, whether or not the debug statement should be translated into machine language can be selected by setting a switch for conditional assembly. When the debug statement is no longer required, the source program can be assembled without major modifications to the program.

CHAPTER 2. HOW TO DESCRIBE SOURCE PROGRAMS

2.1 Basic Configuration of Source Program

When a source program is described by dividing it into several modules, each module which becomes the unit of input to the assembler is called a source module. (If a source program consists of only one module, the source program means the same as the source module.)

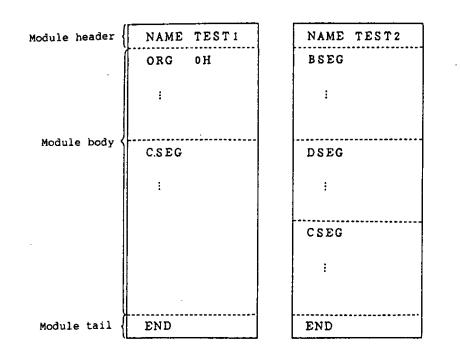

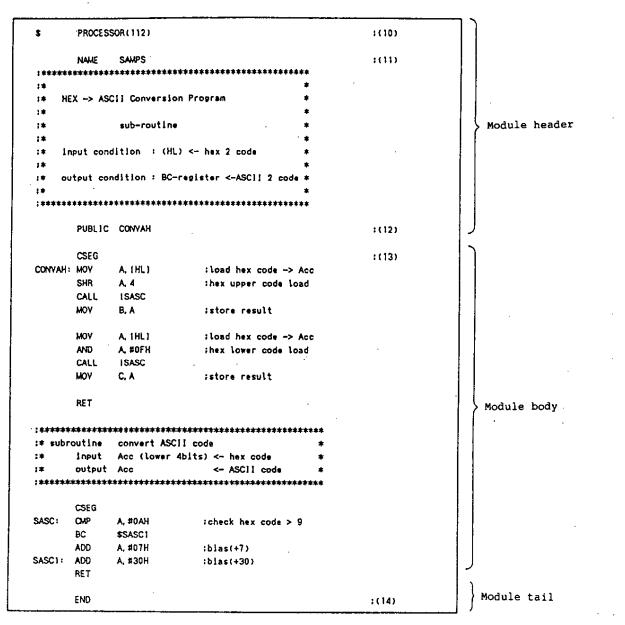

Each source module which becomes the unit of input to the assembler consists mainly of the following three parts:

(1) Module header

(2) Module body

(3) Module tail

Fig. 2-1. Configuration of Source Module

| Module header |  |  |  |  |  |

|---------------|--|--|--|--|--|

| Mođule body   |  |  |  |  |  |

| Module tail   |  |  |  |  |  |

.

#### 2.1.1 Module header

In the module header, five different items can be described as shown in Table 2-1 below.

| Table A | z=1, items inat | Call be Described in Mouure | neudor                                 |  |

|---------|-----------------|-----------------------------|----------------------------------------|--|

| Item    | Item that can   | Explanation                 | Chapter/section                        |  |

| No.     | be described    |                             | in this manual                         |  |

| 1       | Assembler       | Assembler option(s) which   | See 4, "Control                        |  |

|         | options         | are normally specified in   | Instructions".                         |  |

|         |                 | the start-up command line   |                                        |  |

|         |                 | of the assembler can be     | ,                                      |  |

|         |                 | described before NAME       |                                        |  |

|         |                 | directive in the module     |                                        |  |

|         |                 | header.                     |                                        |  |

| 2       | NAME directive  | This directive can be       | See 3.5, "Linkage                      |  |

|         |                 | described only in the       | directives".                           |  |

|         |                 | module header and must      |                                        |  |

|         |                 | always be described.        | ······································ |  |

| 3       | PUBLIC, EXTRN,  | These directives can be     | See 3.5, "Linkage                      |  |

| 1       | or EXBIT        | described only in the       | directives."                           |  |

|         | directive       | module header.              |                                        |  |

| 4       | EQU or SET      | These directives can be     | See 3.3, "Symbol                       |  |

| į       | directive       | described after PUBLIC,     | definition                             |  |

|         |                 | EXTRN, or EXBIT direc-      | directives."                           |  |

|         |                 | tive in the module          |                                        |  |

|         |                 | header.                     |                                        |  |

| 5       | Control         | Control instructions        | See 4, "Control                        |  |

|         | instructions    | can be described after      | Instructions."                         |  |

|         |                 | NAME directive in the       |                                        |  |

|         |                 | module header.              |                                        |  |

| Table 2-1. | Items | That | Can | Be | Described | in | Module | Header_ |

|------------|-------|------|-----|----|-----------|----|--------|---------|

|            |       |      |     |    |           |    |        |         |

NOTE: These items must be described in the module header in the order of item numbers. (Namely, assembler option(s) (Item No. 1) must be described before the NAME directive (Item No. 2). Comment(s) can be described anywhere after the assembler option(s) in the module header and control instruction(s) can be described after the NAME directive in the module header.

2.1.2 Module body

In the module body, the following items cannot be described:

o Assembler options

o NAME directive

o PUBLIC, EXTRN, and EXTBIT directives

All other directives, control instructions, and uCOM-78K/I

instructions can be described in the module body.

The module body must be described by dividing it into units each

called a segment.

The user may define the following four segments with a directive

corresponding to each segment:

(1) Code segment ...... Must be defined with the CSEG directive.

(2) Data segment ...... Must be defined with the BSEG directive.

(4) Absolute segment ... Must be defined with the ORG directive.

The module body may be configured with any segment combinations, provided a data segment and a bit segment must be defined before a code segment.

#### 2.1.3 Module tail

The module tail indicates the end of the source module. The END directive must be described in this part.

2.1.4 Overall configuration of source program The overall configuration of a source module becomes as shown below.

Fig. 2-2. Overall Configuration of Source Program

|     | Assembler option(s)<br>NAME directive<br>EQU and SET directives<br>PUBLIC, EXTRN, and EXTBIT<br>directives<br>Control instruction(s) | Module header |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|---------------|

|     | Directives (other than<br>NAME, PUBLIC, EXTRN, EXTBIT)<br>Control instruction(s)<br>Instruction(s)                                   | Module body   |

|     | END directive                                                                                                                        | Module tail   |

| 000 |                                                                                                                                      |               |

NOTE: \_\_\_\_\_\_ indicates that the directive must always be described.

Examples of simple source module configurations are shown in Fig. 2-3 on the next page.

Fig. 2-3. Examples of Source Module Configurations

2.1.5 Description example of source program

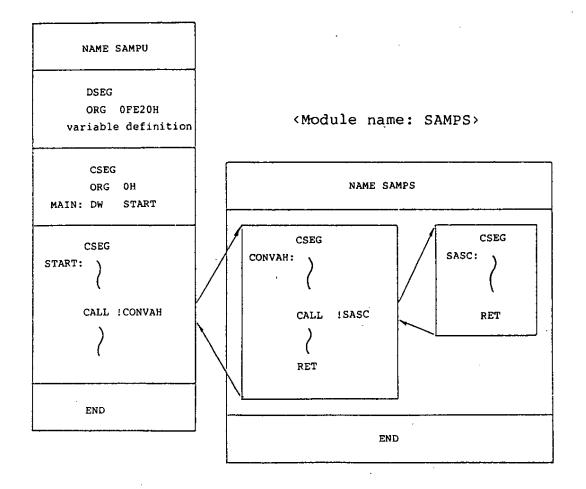

In this subsection, a description example of a uCOM-78K/I source program is shown, in the hope that you can have a general idea of how to describe a source module. (This example is attached to the package product as a sample program file.)

The configuration of the sample program can be illustrated simply as follows:

Fig. 2-4. Configuration of Sample Program

<Module name: SAMPM>

.

This sample program was created by dividing a single source program into two modules. The module "SAMPM" is a main routine of this program and the module "SAMPS", a subroutine which is to be called within the main routine.

<Main routine>

| \$     | PROCESS     | OR(112)                  | :(1)                                    |               |

|--------|-------------|--------------------------|-----------------------------------------|---------------|

|        | NAME        | SAMPM                    | :(2)                                    |               |

| ;***** | *******     | ******                   |                                         |               |

| :*     |             |                          | *                                       |               |

| ;*     | HEX ->      | ASCII Conversion Program | *                                       |               |

| :*     |             |                          | * · · · · · · · · · · · · · · · · · · · | Module header |

| :*     |             | main-routine             | *                                       |               |

| 1#     |             |                          | · •                                     |               |

| ;***** | ******      | ********                 | ********                                |               |

|        |             | MAIN, START              | :(3)                                    | <u>}</u>      |

|        | EXTRN       | CONVAH                   | :(4)                                    |               |

|        | EVINA       | CONTROL 1                |                                         |               |

|        | DSEG        |                          | ;(5)                                    |               |

|        | ORG         | OFE40H                   |                                         |               |

| HDTSA: |             | 1                        |                                         |               |

| STASC: |             | 2                        |                                         |               |

|        |             |                          |                                         |               |

|        | CSEG        |                          | ;(6)                                    |               |

|        | ORG         | он                       | :(7)                                    |               |

| MAIN:  | DW          | START                    |                                         |               |

|        |             |                          |                                         |               |

|        | CSEG        |                          | :(8)                                    |               |

| START  | MOY         | SP, #0E0H                |                                         |               |

|        | - MOA       | MM, #00                  |                                         |               |

|        | MOA         | STBC, #00                |                                         |               |

|        |             |                          |                                         | Module body   |

|        | MOA         | HDTSA, #1AH              | test bey Drends data in Mi real-tar     |               |

|        | MOAM        | HL, #HDTSA               | ;set hex 2-code data in HL registor     |               |

|        | <b>a</b> 11 | 1000001010               | :convert ASCII <- HEX                   |               |

|        | CALL        | ICONVAH                  | :output BC-register <- ASCII code       |               |

|        | MOVW        | HL, #STASC               | set HL <- store ASC11 code table        |               |

|        | MOYH        | A, B                     |                                         |               |

|        | MOY         | (HL), A                  |                                         |               |

|        | INC         | L                        |                                         |               |

|        | MOV         | Ă,C                      |                                         |               |

|        | MOV         | (HL), A                  | · · · ·                                 |               |

|        | BR          | \$\$                     |                                         |               |

|        |             |                          |                                         |               |

- (1) Assembler option

- (2) Declaration of a module name

- (3) Declaration of a symbol referenced from another module as an external definition symbol

- (4) Declaration of a symbol defined in another module as an external reference symbol

- (5) Declaration of the start of a data segment(6) Declaration of the start of a code segment

- (7) Declaration of the start of an absolute segment from address OH

- (8) Declaration of the start of the code segment (meaning the end of the absolute segment)

- (9) Declaration of the end of the module

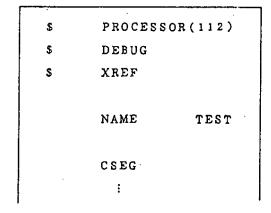

<Subroutine>

(10) Assembler option

- (11) Declaration of a module name

- (12) Declaration of a symbol referenced from another module as an external definition symbol

- (13) Declaration of the start of a code segment

- (14) Declaration of the end of the module

2.2 Description Format of Source Program

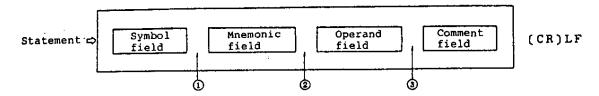

2.2.1 Configuration of statement

A source program consists of statements.

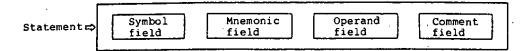

Each statement consists of the four fields shown in Fig. 2-5.

Fig. 2-5. Fields That Make Up A Statement

The Symbol field and the Mnemonic field must be separated from each other with a colon (:) or one or more blank (or TAB) characters.

(2) The Mnemonic field and the Operand field must be separated from each other with one or more blank (or TAB) characters. Depending on the instruction described in the Mnemonic field, the Operand field may not be required.

③ The Comment field if used must be preceded with a semicolon (;).

A statement must be described within a line. (A line must be terminated with a LF (OAH) code.) Up to 99 characters can be described per line.

The following lines may also be described:

- o Dummy line ( a line without statement description)

- o Line consisting of the Symbol field alone

- o Line consisting of the Comment field alone

# 2.2.2 Character Set

Use the following alphabetic, numeric, and special characters to describe statements.

(1) Alphabetic characters

A B C D E F G H I J K L M N O P Q R S T U V W X Y Z a b c d e f g h i j k l m n o p q r s t u v w x y z

\_\_\_ NOTE 2-1

When any lowercase letter is used in a symbol or reserved word description, the lowercase letter is interpreted as its uppercase equivalent.

(2) Numeric characters

| Character                             | Name             | Main use                           |  |  |

|---------------------------------------|------------------|------------------------------------|--|--|

| ?                                     | Question mark    | Symbol equivalent to alphabetic    |  |  |

|                                       |                  | characters                         |  |  |

| @ Unit price                          |                  | Symbol equivalent to alphabetic    |  |  |

|                                       | symbol           | characters                         |  |  |

| _                                     | Underscore       | Symbol equivalent to alphabetic    |  |  |

| _                                     |                  | characters                         |  |  |

| Blank                                 |                  | Delimiter of each field            |  |  |

| НТ (09Н)                              | TAB code         | Character equivalent to Blank      |  |  |

| ,                                     | Comma            | Delimiter between the 1st and 2nd  |  |  |

|                                       | · .              | operands                           |  |  |

| #<br>*                                | Colon            | Delimiter between the Symbol and   |  |  |

|                                       | 1                | Mnemonic fields                    |  |  |

| ; Semicolon                           |                  | Symbol indicating the start of     |  |  |

|                                       |                  | the Comment field                  |  |  |

| CR (0DH)                              | Carriage return  | Symbol indicating the end of a     |  |  |

|                                       | code             | line                               |  |  |

| LF (OAH)                              | Line feed code   | Same as above                      |  |  |

| +                                     | Plus sign        | ADD operator or positive sign      |  |  |

| -                                     | Minus sign       | SUBTRACT operator or negative sign |  |  |

| *                                     | Asterisk         | MULTIPLY operator                  |  |  |

| 1                                     | Slash            | DIVIDE operator                    |  |  |

| •                                     | Period           | BIT operator                       |  |  |

| ( ) Left and right Symbols            |                  | Symbols specifying the order of    |  |  |

|                                       | parentheses      | arithmetic operations to be        |  |  |

| · · · · · · · · · · · · · · · · · · · |                  | performed                          |  |  |

| 1                                     | Single quotation | Symbol indicating the start or     |  |  |

| Ĺ                                     | mark             | end of a character constant        |  |  |

.

| Character | Name                 | Main use                                                        |  |  |

|-----------|----------------------|-----------------------------------------------------------------|--|--|

| \$        | Dollar sign          | o Symbol indicating the location counter                        |  |  |

|           |                      | o Symbol indicating the start of<br>an assembler option         |  |  |

|           |                      | o Symbol specifying a relative<br>addressing mode               |  |  |

| #         | Sharp sign           | Symbol specifying an immediate addressing mode                  |  |  |

| 1         | Exclamation<br>point | o Symbol specifying an absolute<br>addressing mode              |  |  |

|           |                      | o Symbol specifying the operand<br>representation format addr16 |  |  |

|           |                      | of a MOV instruction                                            |  |  |

|           | Braces               | o Symbol specifying an indirect<br>addressing mode              |  |  |

# 2.2.3 Fields of Statement

The respective fields that make up a statement are detailed in this subsection.

(1) Symbol field

A symbol is described in the Symbol field. The term "symbol" refers to a name given to a numerical data or address. By using symbols, the contents of a source program can be understood more easily.

The types and attributes of symbols and the conventions of symbol description are explained below.

,

[Symbol types]

Symbols are available in the types shown in Table 2-2, depending on their use and method of definition.

Table 2-2. Symbol Types

| 1            |                                       |                             |

|--------------|---------------------------------------|-----------------------------|

| Symbol type  | Use                                   | Method of definition        |

| Name         | Used as a numerical data              | This type is described      |

|              | in a source program.                  | in the Symbol field of      |

|              |                                       | the EQU, SET, or DBIT       |

|              |                                       | directive, or in the        |

|              |                                       | Operand field of the        |

|              |                                       | EXTBIT directive.           |

| Label        | Used as an address data               | This type is described      |

|              | in a source program.                  | in the Symbol field of      |

|              |                                       | an instruction or the       |

|              |                                       | DB, DW, or DS directive.    |

|              |                                       | <u>A colon (:) must be</u>  |

|              |                                       | <u>used as a delimiter.</u> |

|              |                                       | This type is also           |

|              |                                       | described in the Operand    |

|              |                                       | field of the EXTRN          |

|              |                                       | directive.                  |

| Segment name | Used as a segment name                | This type is described      |

|              | subject to operation                  | in the Symbol field of      |

|              | in a locater option                   | the CSEG, DSEG, BSEG,       |

|              | · · · · · · · · · · · · · · · · · · · | or ORG directive.           |

| Module name  | Used as a module name                 | This type is described      |

|              | in symbolic debugging                 | in the Operand field        |

| <u></u>      |                                       | of the NAME directive.      |

| Macro name   | Used as a macro name                  | This type is described      |

|              | for macro reference in                | in the Symbol field of      |

|              | a source program.                     | the MACRO directive.        |

[Conventions of symbol description]

All symbols must be described according to the following rules:

Phase-out/Discontinued

- A symbol must be made up of alphanumeric characters and special characters (?, @, and \_) that can be used as a symbol in a manner equivalent to alphabetic characters. The first character of the symbol must always be one of the alphabetic characters or special characters (?, @, and ).

- ② A symbol must be made up of not more than six characters. If a symbol consisting of seven or more characters is described, an error will result.

- ③ No reserved word can be used as a symbol. Reserved words are indicated in Appendix A, List of Reserved Words.

- (4) The same symbol cannot be described two or more times (provided that the name defined with the SET directive can be re-defined with the SET directive).

- (5) Lowercase letters described as a symbol will be interpreted as their uppercase equivalents.

- 6 When describing a label in the Symbol field, separate the Symbol field from the Mnemonic field with a delimiter ":".

(Example of correct symbol descriptions)

| TEN   | EQU   | 10н           | ; | "TEN" is a name.           |

|-------|-------|---------------|---|----------------------------|

| NEXT: | BR    | <b>!</b> 100H | ; | "NEXT" is a label.         |

| C1    | CSEG  |               | ; | "C1" is a segment name.    |

|       | NAME  | SAMPLE        | ; | "SAMPLE" is a module name. |

| MAC1  | MACRO |               | ; | "MAC1" is a macro name.    |

(Example of incorrect symbol descriptions)

| SEVENTY | EQU | 70H   | ; "SEVENTY" is a name.               |

|---------|-----|-------|--------------------------------------|

| 1ST:    | MOV | A,#0H | ; No numeric character can be used   |

|         |     |       | as the 1st character of a symbol.    |

| NEXT    | BR  | 1100н | ; "NEXT" is a label and must be      |

|         |     |       | separated from Mnemonic field        |

|         |     |       | with a colon (:)                     |

| TEN     | EQU | 10н   | ; "TEN" and "ten" are the same named |

| ten     | EQU | 20H   | symbols. Description of "ten" will   |

|         |     |       | thus result in an error.             |

[Symbol attributes] Names and labels each have a value and an attribute. Segment names, module names, and macro names have no value. A value refers to the value of a defined numerical data or address data itself. The attribute of a symbol is called a symbol attribute and must be one of the types indicated in Table 2-3.

Phase-out/Discontinued

| Table 2 | 2-3. | Types | of | Symbol | Attributes |

|---------|------|-------|----|--------|------------|

|---------|------|-------|----|--------|------------|

| Attribute type | Classification                              |  |  |  |

|----------------|---------------------------------------------|--|--|--|

| NUMBER         | o Names defined with EQU and SET directives |  |  |  |

|                | (provided that labels, bit values, and      |  |  |  |

|                | symbols having a bit value defined with     |  |  |  |

|                | the directives are excluded.)               |  |  |  |

| ADDRESS        | o Symbols defined as labels                 |  |  |  |

|                | o Names defined as labels with EQU and SET  |  |  |  |

|                | directives                                  |  |  |  |

| BIT            | o Names defined as bit values with EQU and  |  |  |  |

|                | SET directives                              |  |  |  |

| <u></u>        | o Names defined with DBIT directive         |  |  |  |

(Examples)

| TEN    | EQU        | 10н           | ; | Name "TEN" has attribute NUMBER<br>and value 10H.  |

|--------|------------|---------------|---|----------------------------------------------------|

| START: | ORG<br>MOV | 80H<br>A,#10H | ; | Label "START" has attribute                        |

| BIT1   | EQU        | OFE20H. 0     | ; | Name "BIT1" has attribute BIT and value OFE20H. 0. |

(2) Mnemonic field

```

Phase-out/Discontinued

In the Mnemonic field, a mnemonic instruction or directive is

described.

With an instruction or directive requiring an operand or

operands, the Mnemonic field must be separated from the

Operand field with one or more Blank or TAB characters.

(Example of correct descriptions)

MOV

A, #0H

CALL

!CONVAH

RET

(Example of incorrect descriptions)

MOVA, #0H

; No blank exists between Mnemonic and

Operand fields.

CAL L !CONVAH

; A blank exists in Mnemonic field.

HLT

; uCOM78/I has no such instruction as

"HLT".

```

(3) Operand field

In the Operand field, the data (operands) required for the instruction or directive described in the Mnemonic field must be described. Depending on the instruction or directive, no operand can be described in the Operand field or two or more operands must be described in the Operand field. When describing two or more operands, delimit each operand with a comma (,). The following five types of data can be described in the Operand field: o Constants (numeric constant and character constant) o Register names o Special characters (\$, #, !, and [ ]) o Names and labels o Expressions The size and attribute of the required operand may be different depending on the instruction or directive. Refer to Section 2.4, "Characteristics of Operands" for the sizes and attributes of operands.

See APPENDIX C, "uCOM-78K/I Instruction Set" for the operand representation formats and description methods in the uCOM-78K/I instruction set.

Each of these five types of data that can be described in the Operand field is detailed below.

#### [Constants]

A constant is a fixed value or data item and is also referred to as an immediate data.

Constants are divided into numeric constants and character constants.

o Numeric constants

A binary, octal, decimal, or hexadecimal number can be described as a numeric constant. The method of representing each numeric constant type is shown in Table 2-4 below.

Table 2-4. Methods of Representing Numeric Constant Types

| Constant type    | Method of representation         | Example |

|------------------|----------------------------------|---------|

| Binary constant  | Character "B" is suffixed to a   | 1101B   |

| (Binary number)  | string of binary characters      |         |

|                  | (value).                         |         |

| Octal constant   | Character "O" is suffixed to a   | 740     |

| (Octal number)   | string of octal characters       |         |

|                  | (value).                         |         |

| Decimal constant | A string of decimal characters   | 128     |

| (Decimal number) | (value) is described with or     | 128D    |

|                  | without suffixing character "D"  |         |

|                  | to the string.                   |         |

| Hexadecimal      | Character "H" is suffixed to a   | 8 CH    |

| constant         | string of hexadecimal characters | 0A6H    |

| (Hexadecial      | (value). If the first character  |         |

| number)          | of the constant begins with one  |         |

|                  | of the characters "A through F", |         |

|                  | "0" must be prefixed to the      |         |

|                  | constant.                        |         |

o Character constants

```

A character constant is expressed by enclosing a character

or a string of characters shown in 2.2.2, "Character set"

with a pair of single quotation marks.

As a result of an assembly process, the character or

characters are converted into 7-bit ASCII code with the

parity bit (MSB) set as "0".

To use a single quotation mark as it is originally intended,

the single quotation mark must be input twice in succession.

Examples:

'A'

1 1

; Represents a single blank.

1111

; Represents a pair of single quotation

marks.

'main'

```

[Register names]

The following registers can be described in the Operand

field.

o General-purpose registers

o General-purpose register pairs

o Special function registers

General-purpose registers and general-purpose register pairs include those which can be described with their absolute names (R0 to R7 and RP1 to RP3), as well as with their function names (X, A, B, C, D, E, H, L,, AX, BC, DE, and HL). A register name that can be described in the Operand field may be different depending on the type of instruction. See APPENDIX C.1, "Instruction Set and Its Operation" for details of the method of describing each register.

[Special characters]

Special characters that can be described in the Operand field are shown in Table 2-5.

• • •

Table 2-5. Special Characters That Can Be Described in

| Operand           | T TETU                                                                          |

|-------------------|---------------------------------------------------------------------------------|

| Special character | Function                                                                        |

| \$                | o Indicates the location address of the instruction having this operand (or the |

|                   | 1st byte of the address with a multiple-                                        |

|                   | byte instruction).                                                              |

|                   | o Indicates a relative addressing mode for                                      |

|                   | a Branch instruction.                                                           |

| 1                 | o Indicates an absolute addressing mode                                         |

|                   | for a Branch or Call instruction.                                               |

|                   | o Indicates the specification of addr16                                         |

|                   | which allows all memory space to be                                             |

|                   | specified for a MOV instruction.                                                |

| #                 | Indicates an immediate data.                                                    |

|                   | Indicates an indirect addressing mode.                                          |

(Application examples of special characters)

| Address | Source | program    |   |

|---------|--------|------------|---|

| 100     | LOOP:  | INC A      |   |

| 101     |        | BNZ \$\$-1 | 1 |

In (1) above, the first "\$" in the Operand field indicates the relative addressing of the conditional branch instruction BNZ. The second "\$" indicates the location address 101 to which the first byte of the object code for the instruction "BNZ \$\$-1" is to be assigned. The description in (1) can be substituted with "BNZ \$LOOP".

Source program

| BR !100H      | ; "!" indicates the absolute address- |

|---------------|---------------------------------------|

|               | ing of BR (unconditional branch)      |

|               | instruction.                          |

| MOV A, !2000H | ; "!" indicates addr16 specification  |

|               | of MOV instruction                    |

| SUB A, #10H   | ; "#" indicates an immediate data.    |

2-20

TEN EQU 10H SUB A, #TEN ; "#" indicates an immediate data. ; "[ ]" indicate an indirect AND A, [HL] addressing mode. [Names and labels] If a name or label is described in the Operand field, the value of the name or label becomes a numerical data subject to operation by the instruction or directive described in the Mnemonic field. (Application example of name) TEN EOU 10H MOV A, #TEN ; This description can be substituted with "MOV A, #10H". (Application example of label) ORG 100H LOOP: INC A BNZ \$LOOP ; This description can be substituted with "BNZ \$100H". [Expressions] In the Operand field, expressions can be described. An expression is a valid series of constants, \$ indicating a location address, names, or labels, that are connected with operators and can be used as an operand of an instruction. For the expressions and operators, see Section 2.3, "Expressions and Operators". (Example of expression description) TEN EQU 10H

MOV A, #TEN-5H

In this example, "#TEN-5H" is an expression. In this expression, name "TEN" and numeric constant "5H" are connected with the "-" (minus) operator. The value of the expression is OBH. Therefore, this description can be substituted with "MOV A, #OBH".

(4) Comment field

In the Comment field, any remarks to identify or explain a particular step or operation in a program may be described following the input of a semicolon (;). By describing comments in the Comment field, an easy-tounderstand source program can be created. The comments described in the Comment field are not subject to assembler operation (i.e., conversion into machine language) but are output as is on an assembly list.

# (Examples of comment descriptions)

\$ PROCESSOR(112) NAME SAMPS :\* \* :\* HEX -> ASC11 Conversion Program ٠ :\* ± Lines consisting of :\* sub-routine ۰ Comment field only :\* \* :\* input condition = (HL) <- hex 2 code</pre> \* 1\* :\* output condition : BC-register <-ASCI1 2 code \*</pre> ;\* \* PUBLIC CONVAH

|         | CSEG |         |                       |                                       |

|---------|------|---------|-----------------------|---------------------------------------|

| CONVAH: | MOY  | A (HL)  | :load hex code -> Acc |                                       |

|         | SHR  | A, 4    | thex upper code load  |                                       |

|         | CALL | ISASC   |                       |                                       |

|         | MOA  | 8, A    | store result          | Lines in which comments are described |

|         | MON  | A, THUT | :load hex code -> Acc | ale described                         |

|         | AND  | A, #OFH | thex lower code load  |                                       |

|         | CALL | ISASC   |                       |                                       |

|         | MOV  | C, A    | istore result         |                                       |

|         |      |         |                       |                                       |

RET

#### 2.3 Expressions and Operators

An expression is a valid series of constants, \$ indicating a location address, names, or labels connected with operators. Elements of an expression other than the operators are called terms and are referred to as the 1st term, 2nd term, and so forth from left to right, in their order of description. Operators are available in the types shown in Table 2-6, and their order of precedence in calculation has been predetermined as shown in Table 2-7.

A pair of parentheses (i.e., left and right parentheses) are used to change the order in which calculations are to be performed.

Example: MOV A, #5\*(SYM+1)

; ①

Phase-out/Discontinued

In (1) above, "5\*(SYM+1)" is an expression. "5" is the 1st term of the expression and "SYM" and "1" are the 2nd and 3rd terms, respectively. "\*, +, and ()" are operators.

| Table | 2-6. | Types | of | Operators |

|-------|------|-------|----|-----------|

|-------|------|-------|----|-----------|

| Type of operator          | Operators                       |

|---------------------------|---------------------------------|

| Arithmetic operators      | +, -, *, /, MOD, + sign, - sign |

| Logical operators         | OR, AND, NOT, XOR               |

| Relational operators      | EQ, NE, GT, GE, LT, LE          |

| Shift operators           | SHR, SHL                        |

| Byte-separating operators | HIGH, LOW                       |

| Bit operator              | . (Period)                      |

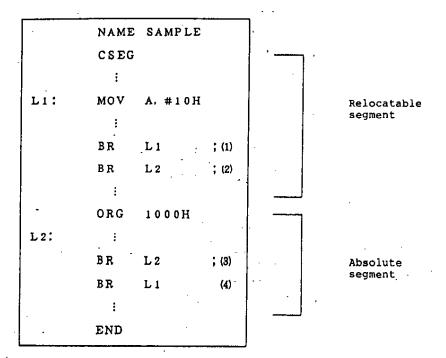

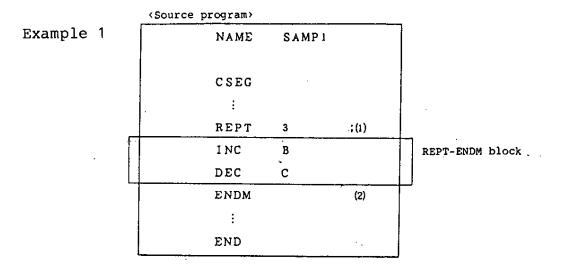

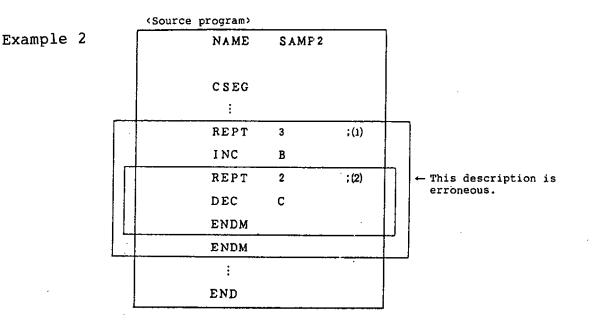

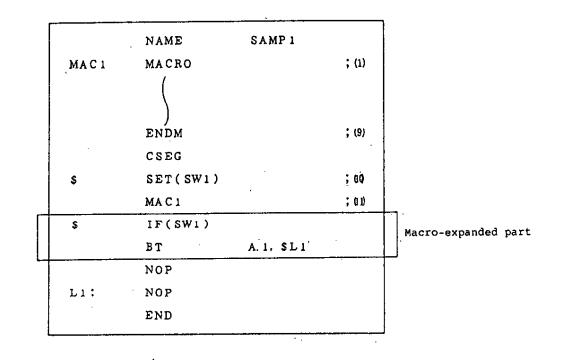

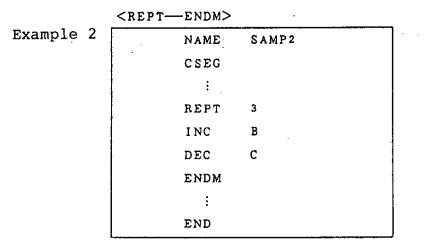

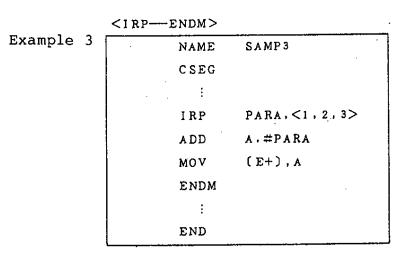

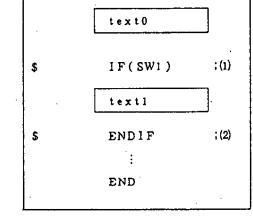

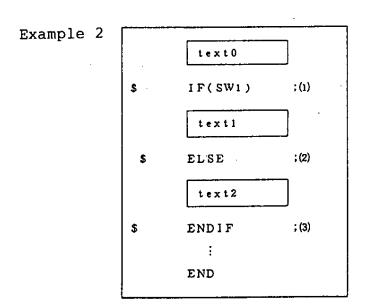

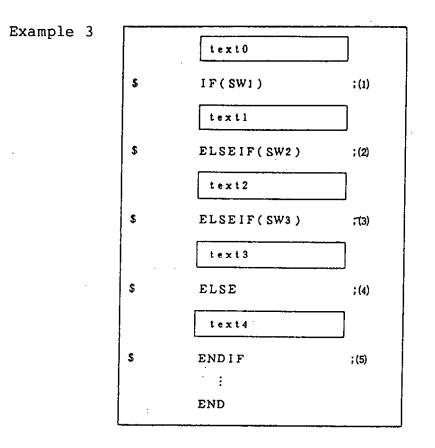

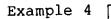

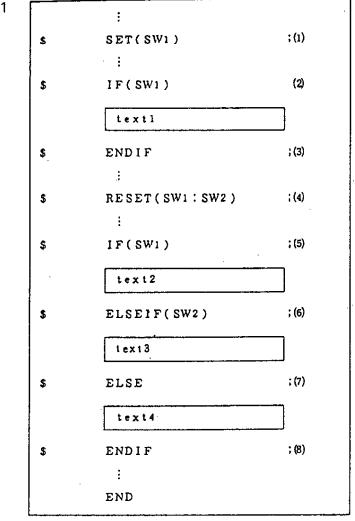

| Other operators           | ( )                             |