**Customer Notification**

# IE-703288-G1-EM1<sup>TM</sup>

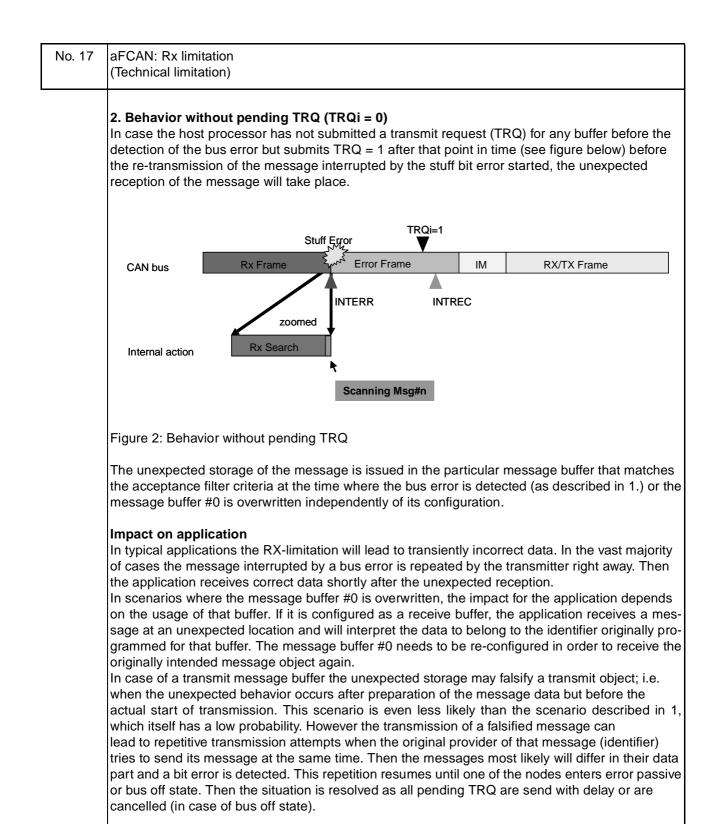

## **In-Circuit-Emulator**

**Operating Precautions**

**Target Device**

V850ES/SG2 V850ES/SJ2

Document No.TPS-HE-B-2843Date PublishedAugust 2004

© NEC Electronics (Europe) GmbH

#### DISCLAIMER

The related documents in this customer notification may include preliminary versions. However, preliminary versions may not have been marked as such.

The information in this customer notification is current as of its date of publication. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC PRODUCT(S). Not all PRODUCT(S) and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

No part of this customer notification may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this customer notification. NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC PRODUCT(S) listed in this customer notification or any other liability arising from the use of such PRODUCT(S).

No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others. Descriptions of circuits, software and other related information in this customer notification are provided for illustrative purposes of PRODUCT(S) operation and/or application examples only. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

While wherever feasible, NEC endeavors to enhance the quality, reliability and safe operation of PRODUCT(S) the customer agree and acknowledge that the possibility of defects and/or erroneous thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects and/or errors in PRODUCT(S) the customer must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

The customer agrees to indemnify NEC against and hold NEC harmless from any and all consequences of any and all claims, suits, actions or demands asserted against NEC made by a third party for damages caused by one or more of the items listed in the enclosed table of content of this customer notification for PRODUCT(S) supplied after the date of publication.

#### Applicable Law:

The law of the Federal Republic of Germany applies to all information provided by NEC to the Customer under this Operating Precaution document without the possibility of recourse to the Conflicts Law or the law of 5<sup>th</sup> July 1989 relating to the UN Convention on Contracts for the International Sale of Goods (the Vienna CISG agreement).

Düsseldorf is the court of jurisdiction for all legal disputes arising directly or indirectly from this information. NEC is also entitled to make a claim against the Customer at his general court of jurisdiction.

If the supplied goods/information are subject to German, European and/or North American export controls, the Customer shall comply with the relevant export control regulations in the event that the goods are exported and/or re-exported. If deliveries are exported without payment of duty at the request of the Customer, the Customer accepts liability for any subsequent customs administration claims with respect to NEC.

- **Notes: 1.** "NEC" as used in this statement means NEC Corporation and also includes its direct or indirect owned or controlled subsidiaries.

- 2. "PRODUCT(S)" means 'NEC semiconductor products' (NEC semiconductor products means any semiconductor product developed or manufactured by or for NEC) and/or 'TOOLS' (TOOLS' means 'hardware and/or software development tools' for NEC semiconductor products' developed, manufactured and supplied by 'NEC' and/or 'hardware and/or software development tools' supplied by NEC but developed and/or manufactured by independent 3<sup>rd</sup> Party vendors worldwide as their own product or on contract from NEC)

| (A) | Table of Operating Precautions    5   |

|-----|---------------------------------------|

| (B) | Description of Operating Precautions7 |

| (C) | Valid Specification                   |

| (D) | Revision History                      |

### (A) Table of Operating Precautions

|     |                                                                        |                                  | IE-7 | 03288-G1- | EM1  |

|-----|------------------------------------------------------------------------|----------------------------------|------|-----------|------|

|     |                                                                        | Rev.                             | 1.02 | 1.03      | 1.04 |

| No. | Outline                                                                | Control-<br>Code <sup>Note</sup> | С    | D         | E    |

| 1   | ROM correction function cannot be emulated (Direction of use)          |                                  | ×    | ×         | ×    |

| 2   | Use-prohibited area<br>(Direction of use)                              |                                  | ×    | ×         | ×    |

| 3   | Emulator memory settings<br>(Direction of use)                         |                                  | ×    | ×         | ×    |

| 4   | Accuracy of ADC and DAC<br>(Technical limitation)                      |                                  | ×    | 1         | 1    |

| 5   | Watchdog timer during break<br>(Direction of use)                      |                                  | X    | ×         | ×    |

| 6   | Timer M during break<br>(Direction of use)                             |                                  | X    | X         | ×    |

| 7   | Timer M compare interrupt<br>(Specification change notice)             |                                  | X    | ×         | X    |

| 8   | Access of UAnRX register during break (Specification change notice)    |                                  | ×    | ×         | ×    |

| 9   | Access of CBnRX register during break (Specification change notice)    |                                  | ×    | ×         | ×    |

| 10  | Access of C0RGPT register during break (Specification change notice)   |                                  | ×    | X         | ×    |

| 11  | Access of C0TGPT register during break (Specification change notice)   |                                  | ×    | ×         | ×    |

| 12  | Access of C0GNCTRL register during break (Specification change notice) |                                  | ×    | ×         | ×    |

| 13  | SLD instruction precaution<br>(Specification change notice)            |                                  | ×    | ×         | ×    |

| 14  | aFCAN transmission / reception<br>(Technical limitation)               |                                  | ×    | ×         | 1    |

| 15  | TMPn / TMQn external event counter function (Direction of use)         |                                  | ×    | ×         | ×    |

| 16  | TMPn / TMQn capture operation<br>(Direction of use)                    |                                  | ×    | ×         | ×    |

|     |                                                |                                  | IE-7 | 03288-G1-I | EM1  |

|-----|------------------------------------------------|----------------------------------|------|------------|------|

|     |                                                | Rev.                             | 1.02 | 1.03       | 1.04 |

| No. | Outline                                        | Control-<br>Code <sup>Note</sup> | С    | D          | E    |

| 17  | aFCAN: Rx limitation<br>(Technical limitation) |                                  | X    | X          | X    |

✓ Not applicable

X Applicable

**Note:** The Control Code is indicated by the letter appearing at the 2nd position from the left in the serial number of the product.

## (B) Description of Operating Precautions

| No. 1 | ROM correction function cannot be emulated (Direction of use)     |

|-------|-------------------------------------------------------------------|

|       | <u>Details</u><br>The ROM correction function cannot be emulated. |

|       | <u>Workaround</u><br>There is no workaround.                      |

| A fa | <i>tails</i><br>ail-safe break is no<br>a of the device is a            |                                                                                                                                                                    | gram execution or                                                                                                                                                                      | an access to a us                                                                                                                                               | se prohibited mer                                                                                                                                                                    |

|------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A b  | o <u>rkaround</u><br>ireak can be genei<br>ak in the debugge            | •                                                                                                                                                                  | -                                                                                                                                                                                      | or a memory acce                                                                                                                                                | ss occurs by setti                                                                                                                                                                   |

|      | Detailed description of                                                 | of restriction on use-pro                                                                                                                                          | hibited area                                                                                                                                                                           |                                                                                                                                                                 |                                                                                                                                                                                      |

|      | Device:                                                                 | D703260(Y),<br>D703270(Y),<br>D703280(Y)                                                                                                                           | D70(F)3261(Y),<br>D70(F)3271(Y),<br>D70(F)3281(Y),<br>D70(F)3264(Y),<br>D70(F)3274(Y),<br>D70(F)3284(Y)                                                                                | D703262(Y),<br>D703272(Y),<br>D703282(Y),<br>D703265(Y),<br>D703275(Y),<br>D703285(Y),<br>D703285(Y),                                                           | D70(F)3263(Y),<br>D70(F)3273(Y),<br>D70(F)3283(Y),<br>D70(F)3266(Y),<br>D70(F)3276(Y),<br>D70(F)3286(Y),<br>D70(F)3288(Y)                                                            |

|      | Use-prohibited area<br>in which a fail safe<br>break does not<br>occur: | (1): 0x3FF8000 to<br>0x3FF8FFF                                                                                                                                     | (2): 0x60000 to<br>0x7FFFF<br>(3): 0x3FF0000 to<br>0x3FF6FFF                                                                                                                           | (4):0x3FF0000 to<br>0x3FF4FFF                                                                                                                                   | (5):0xA0000 to<br>0xFFFFF<br>(6):0x3FF0000 to<br>0x3FF2FFF                                                                                                                           |

|      | Execution access<br>break (used to<br>replace fail save<br>break):      | <ul> <li>Event: Execution</li> <li>Address: Area (1)</li> <li>(2 execution events<br/>used for above con-<br/>ditions)</li> </ul>                                  | <ul> <li>Event: Execution</li> <li>Address: Area (2)</li> <li>Event: Execution</li> <li>Address: Area (3)</li> <li>(4 execution events<br/>used for above con-<br/>ditions)</li> </ul> | <ul> <li>Event: Execution</li> <li>Address: Area (4)</li> <li>(2 execution events<br/>used for above con-<br/>ditions)</li> </ul>                               | <ul> <li>Event: Execution</li> <li>Address:Area (5)</li> <li>Event: Execution</li> <li>Address:Area (6)</li> <li>(4 execution events<br/>used for above con-<br/>ditions)</li> </ul> |

|      | R/W access break<br>(used to replace fail<br>save break):               | <ul> <li>Event: R/W</li> <li>Access size: No<br/>Condition</li> <li>Address: Area (1)</li> <li>(2 execution events<br/>used for above con-<br/>ditions)</li> </ul> | <ul> <li>Event: R/W</li> <li>Access size: No<br/>Condition</li> <li>Address: Area (3)</li> <li>(2 access events<br/>used for above con-<br/>ditions)</li> </ul>                        | <ul> <li>Event: R/W</li> <li>Access size: No<br/>Condition</li> <li>Address: Area (4)</li> <li>(2 access events<br/>used for above con-<br/>ditions)</li> </ul> | <ul> <li>Event: R/W</li> <li>Access size: No<br/>Condition</li> <li>Address: Area (6)</li> <li>(2 access events<br/>used for above con-<br/>ditions)</li> </ul>                      |

| Emulator memory settings<br>(Direction of use)                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Details                                                                                                                                                                                                                                                                                                                                                                                              |

| When the debugger connects to the emulator the memory settings of the devicefile are not aut matically set for several devices. This applies for devices with internal memory sizes that do n match to the below list.                                                                                                                                                                               |

| The size of internal memory of the emulator can only be set to the following values:<br>Internal ROM:                                                                                                                                                                                                                                                                                                |

| 32 KBytes, 64 KBytes, 128 KBytes, 256 KBytes, 512 KBytes or 1 MByte.<br>Internal RAM:                                                                                                                                                                                                                                                                                                                |

| 4 KBytes, 12 KBytes, 28 KBytes or 60 KBytes.                                                                                                                                                                                                                                                                                                                                                         |

| Greenhills Multi:                                                                                                                                                                                                                                                                                                                                                                                    |

| For devices which have different memory sizes than listed above, the size of internal ROM RAM memory is set to the next smaller size of the above list.                                                                                                                                                                                                                                              |

| E. g.: for devices that contain 384/32 KBytes of internal ROM/RAM memory, 256/28 KBytes is s (512/28 KBytes is set for devices containing 640/48 KBytes of internal ROM/RAM).                                                                                                                                                                                                                        |

| IAR Embedded workbench:                                                                                                                                                                                                                                                                                                                                                                              |

| When connecting the debugger to the emulator an error message is shown if the ROM si selected in the devicefile does not fit the possible settings of the emulator (see list above).                                                                                                                                                                                                                 |

| The RAM size is automatically set to the next larger acceptable option.                                                                                                                                                                                                                                                                                                                              |

| <u>Workaround</u>                                                                                                                                                                                                                                                                                                                                                                                    |

| Change the settings when the connection between debugger and emulator is established.                                                                                                                                                                                                                                                                                                                |

| Greenhills Multi:                                                                                                                                                                                                                                                                                                                                                                                    |

| Set the desired size of internal ROM/RAM memory in the .rc file which is executed when t debugger connects to the emulator using the target command "CPU [R=   A= ]".                                                                                                                                                                                                                                |

| Set the internal memory to the next larger size of the above list (e. g. select 512 KBytes for devices that contains 384 KBytes of internal ROM).                                                                                                                                                                                                                                                    |

| The actual settings for internal memory can be checked in the target window using the "CP command.                                                                                                                                                                                                                                                                                                   |

| IAR Embedded workbench:                                                                                                                                                                                                                                                                                                                                                                              |

| Set the internal memory size in the configuration window for "Hardware Settings" which oper<br>automatically when connecting to the emulator for the first time. The "Hardware Settings" wind<br>can also be invoked under the "Emulator   Hardware Setup" drop down menu to alter or check to<br>actual settings. Set the internal memory to the next larger size of the above list (e. g. select 5 |

| KBytes for a devices that contains 384 KBytes of internal ROM).                                                                                                                                                                                                                                                                                                                                      |

| Take care that the memory borders of the actual device are not exceeded since the acutal me ory size provided by the emulator may be larger than the memory size of the emulated device.                                                                                                                                                                                                             |

| No. 4 | Accuracy of A/D converter and D/A converter<br>(Technical limitation)                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>Details</u><br>The accuracy of the A/D converter does not meet the specification.                                                                             |

|       | Workaround<br>There is no workaround. The accuracy has been improved with emulation boards of control code<br>D or later (the conventional error is approx. 8%). |

| No. 5 | Watchdog timer during break<br>(Direction of use)                                                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>Details</u><br>When both of the following conditions (a) and (b) are fulfilled simultanously and a break occurs,<br>the watchdog timer does not stop and will cause a reset or non maskable interrupt. If a reset<br>occurs, the debugger hangs up. |

|       | Conditions that need to be fulfilled so that the above behaviour occurs:<br>(a) The main clock or subclock is selected as the clock source of the watchdog timer and<br>(b) The ring oscillator is stopped (RSTOP flag = 1).                           |

|       | <u>Workaround</u><br>As a workaround to prevent the above behaviour do not stop the ring oscillator clock.                                                                                                                                             |

| No. 6 | Timer M during break<br>(Direction of use)                                                                                                                                                   |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>Details</u><br>When a break occurs while the following conditions (a) and (b) are both fulfilled, timer M does not<br>stop even if the peripheral break function has been set to 'break'. |

|       | <ul><li>(a) INTWT, Ring oscillator clock (fR/8) or subclock is selected as the clock source for timer M.</li><li>(b) The main clock is stopped by setting the MCK flag.</li></ul>            |

|       | (Note: The peripheral break function is not supported by the debugger ID850 V2.51.)                                                                                                          |

|       | Workaround                                                                                                                                                                                   |

|       | Implement one of the below workarounds to stop timer M during a break using the peripheral break function:                                                                                   |

|       | <ul><li>(a) Use the main clock (fXX, fXX/2, fXX/4, fXX/64, fXX/512) as the source clock for timer M.</li><li>(b) Do not stop the main clock oscillation.</li></ul>                           |

| No. 7 | Timer M compare interrupt<br>(Specification change notice)                                                                                |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>Details</u><br>An unexpected interrupt occurs after activation of timer M when the compare register TM0CMP0 contains the value 0xFFFF. |

|       | TMM starts to operate                                                                                                                     |

|       | TM0CE                                                                                                                                     |

|       | TMM FFFFH 0000H 0001H 0002H FFFEH FFFFH 0000H                                                                                             |

|       |                                                                                                                                           |

|       |                                                                                                                                           |

|       | Interrupt                                                                                                                                 |

|       |                                                                                                                                           |

|       | <u>Workaround</u><br>Do not set TM0CMP0 to 0xFFFF.                                                                                        |

| No. 8 | Access of UAnRX register during break<br>(Specification change notice)                                                                                                                                                                                             |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>Details</u>                                                                                                                                                                                                                                                     |

|       | An overrun error occurs under the following conditions (a) to (c):                                                                                                                                                                                                 |

|       | (a) If a break occurs after reading the UART receive buffer register (UAnRX) and the UAnRX reg-<br>ister is displayed in the I/O register window of the debugger, an overrun error occurs when UART<br>reception is performed for the next time.                   |

|       | (b) If a software break occurs immediately after reading the UART receive buffer register (UAnRX), an overrun error occurs when UART reception is performed the next time regardless of whether or not the UAnRX register is displayed in the I/O register window. |

|       | (c) If a DMA transfer from the UART receive buffer register (UAnRX) is performed during a brea-<br>k <sup>NOTE</sup> , an overrun error occurs when UART reception is performed the next time.                                                                     |

|       | Note: Including breaks by the RAM monitor function or DMM function. However the realtime RAM monitor function does not cause this behaviour since it does not set breaks.                                                                                          |

|       | Remark: An overrun error also occurs when the UART receives data multiple times during a break (This complies with the specification of the emulator).                                                                                                             |

|       | Workaround                                                                                                                                                                                                                                                         |

|       | <ul><li>(a) Do not display the UAnRX register in the I/O register window.</li><li>(b) Set a hardware break when setting a break immediately after reading the UAnRX register</li><li>(c) There is no workaround.</li></ul>                                         |

| No. 9 | Access of CBnRX register during break<br>(Specification change notice)                                                                                                                                                                                                                                    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>Details</u><br>When the CSIBn receive data register (CBnRX) is read, it usually starts the next reception opera-<br>tion. Under the following conditions (a) and (b), however, the next reception operation is not<br>started even if CBnRX is read.                                                   |

|       | <ul> <li>(a) If a software break occurs immediately after reading the CSIBn receive register (CBnRX).</li> <li>(b) If a DMA transfer from the CSIBn receive data register (CBnRX) is performed during a break<sup>NOTE</sup>. As a result the communication stops or the DMA controller stops.</li> </ul> |

|       | Note: Including breaks by the RAM monitor function or DMM function. However the realtime RAM monitor function does not cause this behaviour since it does not set breaks.                                                                                                                                 |

|       | Workaround<br>(a) Set a hardware break when setting a break immediately after reading the CBnRX register.<br>(b) There is no workaround.                                                                                                                                                                  |

| No. 10 | Access of C0RGPT register during break<br>(Specification change notice)                                                                                                                                                                                                    |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        | <u>Details</u><br>Under the following conditions (a) and (b), the read pointer (RGPT) that should be incremented is<br>not incremented and the same data as previously read is read again.                                                                                 |  |  |  |

|        | <ul> <li>(a) If a software break occurs immediately after reading the CAN0 module receive history list register (C0RGPT)</li> <li>(b) If a DMA transfer from the CAN0 module receive history list register (C0RGPT) is performed during a break<sup>NOTE</sup>.</li> </ul> |  |  |  |

|        | Note: Including breaks by the RAM monitor function or DMM function. However the realtime RAM monitor function does not cause this behaviour since it does not set breaks.                                                                                                  |  |  |  |

|        | <u>Workaround</u><br>(a) Set a hardware break when setting a break immediately after reading the C0RGPT register.<br>(b) There is no workaround.                                                                                                                           |  |  |  |

| No. 11 | Access of C0TGPT register during break<br>(Specification change notice)                                                                                                             |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        | Details                                                                                                                                                                             |  |  |  |

|        | Under the following conditions (a) and (b), the read pointer (TGPT) that should be incremented is not incremented and the same data as previously transmitted is transmitted again. |  |  |  |

|        | (a) If a software break occurs immediately after reading the CAN0 module transmit history list register (C0TGPT).                                                                   |  |  |  |

|        | (b) If a DMA transfer from the CAN0 module transmit history list register (C0TGPT) is performed during a break <b>NOTE</b> .                                                        |  |  |  |

|        | Note: Including breaks by the RAM monitor function or DMM function. However the realtime RAM monitor function does not cause this behaviour since it does not set breaks.           |  |  |  |

|        | <u>Workaround</u>                                                                                                                                                                   |  |  |  |

|        | <ul><li>(a) Set a hardware break when setting a break immediately after reading the C0TGPT register.</li><li>(b) There is no workaround.</li></ul>                                  |  |  |  |

| No. 12 | Access of C0GNCTRL register during a break<br>(Specification change notice)                                                                                                                                                                                                                     |  |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|        | Details                                                                                                                                                                                                                                                                                         |  |  |  |  |

|        | When a register access is performed in the following sequence, an unexpected forcible shutdowr may occur after the sequence is complete.                                                                                                                                                        |  |  |  |  |

|        | Sequence :                                                                                                                                                                                                                                                                                      |  |  |  |  |

|        | <ul> <li>(1) The EFSD bit of the CAN0 module control register (C0GMCTRL) is set.</li> <li>(2) The I/O register<sup>NOTE</sup> is accessed.</li> </ul>                                                                                                                                           |  |  |  |  |

|        | (3) The GOM bit of the CAN0 mode control register (C0GMCTRL) is cleared.                                                                                                                                                                                                                        |  |  |  |  |

|        | Note: I/O register access except for clearing the GOM bit of the C0GMCTRL register                                                                                                                                                                                                              |  |  |  |  |

|        | The conditions under which a forcible shutdown takes place are shown below:<br>(a) If a break occurs immediately after the I/O register access in (2) occurs.<br>(b) If a break by the RAM monitor function or the DMM function occurs immediately after the I/O register access in (2) occurs. |  |  |  |  |

|        | (c) Stepwise execution is performed for the I/O register access in (2).                                                                                                                                                                                                                         |  |  |  |  |

|        | <u>Workaround</u>                                                                                                                                                                                                                                                                               |  |  |  |  |

|        | Be sure to set the EFSD bit and clear the GOM bit successively when executing a forcible shut down. Do not perform a register access in the above sequence when not performing a forcible shutdown.                                                                                             |  |  |  |  |

| No. 13 | SLD instruction precaution (Specification change notice)<br>(Specification change notice)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                               |                                                                                                     |                                                                                                     |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

|        | <u>Details</u><br>If a conflict occurs between the decode operation of the instruction (<2> in the examples men-<br>tioned below) immediately before the <b>sld</b> instruction (<3> in the examples) following a special<br>instruction (<1> in the examples) and an interrupt request before execution of the special instruc-<br>tion is complete, the execution result of the special instruction may not be stored in a register as<br>expected.<br>This situation may only occur when the same register is used as the destination register of the<br>special instruction and the <b>sld</b> instruction, and when the register value is referenced by the<br>instruction followed by the <b>sld</b> instruction. |                                                                                                                               |                                                                                                     |                                                                                                     |

|        | Conditions under which the<br>The situation may occur wh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                               | nditions (1) to (3) are s                                                                           | atisfied.                                                                                           |

|        | (1) Either condition (I) or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | (II) is satisfied                                                                                                             |                                                                                                     |                                                                                                     |

|        | Condition (I):<br>The same register is used as the destination register of a special instruction (see below) and<br>the subsequent <b>sld</b> instruction and as the source register (reg1) of an instruction shown<br>below followed by the <b>sld</b> instruction (See Example 1).                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                               |                                                                                                     |                                                                                                     |

|        | mov <b>reg1</b> ,reg2<br>satadd <b>reg1</b> ,reg2<br>tst <b>reg1</b> ,reg2<br>cmp <b>reg1</b> ,reg2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | not <b>reg1</b> ,reg2<br>or <b>reg1</b> ,reg2<br>subr <b>reg1</b> ,reg2<br>mulh <b>reg1</b> ,reg2                             | satsubr <b>reg1</b> ,reg2<br>xor <b>reg1</b> ,reg2<br>sub <b>reg1</b> ,reg2                         | satsub <b>reg1</b> ,reg2<br>and <b>reg1</b> ,reg2<br>add <b>reg1</b> ,reg2                          |

|        | Condition (II):<br>The same register is used as the destination register of a special instruction (see below) and<br>the subsequent <b>sld</b> instruction and as the source register (reg2) of an instruction shown<br>below followed by the <b>sld</b> instruction (See Examples 2 and 3).                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                               |                                                                                                     |                                                                                                     |

|        | not reg1, <b>reg2</b><br>satadd imm5, <b>reg2</b><br>tst reg1, <b>reg2</b><br>add imm5, <b>reg2</b><br>sar imm5, <b>reg2</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | satsubr reg1, <b>reg2</b><br>or reg1, <b>reg2</b><br>subr reg1, <b>reg2</b><br>cmp reg1, <b>reg2</b><br>shl imm5, <b>reg2</b> | satsub_reg1, <b>reg2</b><br>xor reg1, <b>reg2</b><br>sub reg1, <b>reg2</b><br>cmp imm5, <b>reg2</b> | satadd reg1, <b>reg2</b><br>and reg1, <b>reg2</b><br>add reg1, <b>reg2</b><br>shr imm5, <b>reg2</b> |

|        | Special instruction:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                               |                                                                                                     |                                                                                                     |

|        | • Id instruction: Id.b,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ld.h, ld.w, ld.bu, ld.hu                                                                                                      |                                                                                                     |                                                                                                     |

|        | • <b>sld</b> instruction: sld.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | b, sld.h, sld.w, sld.bu, s                                                                                                    | sld.hu                                                                                              |                                                                                                     |

|        | Multiply instruction:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mul, mulh, mulhi, mul                                                                                                         | u                                                                                                   |                                                                                                     |

|        | (2) When the execution result of the special instruction (see above) has not been stored in the destination register before execution of the instruction (instruction of condition (I) or (II)) immediately before the <b>sld</b> instruction starts in the CPU pipeline.                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                               |                                                                                                     |                                                                                                     |

| (Sp       |       |          | change notice)            | pecification change notice)                                                                                                                                                              |

|-----------|-------|----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (cc       | ont.) |          |                           |                                                                                                                                                                                          |

| (3)       |       |          | •                         | ion of the instruction (instruction of condition (I) or (II)) immediately and interrupt request servicing conflict.                                                                      |

| <u>Ex</u> | amp   | les of i | instruction seque         | nces that may cause the conflict:                                                                                                                                                        |

| Ex        | amp   | le 1:    |                           |                                                                                                                                                                                          |

|           | <1>   | ld.w     | [r11], <b>r10</b><br>:    | This situation occurs when the decode operation of the <b>mov</b> instruction (<2>) immediately before the <b>sld</b> instruction (<3>) and interrupt request servicing conflict before  |

| .         | <2>   | mov      | <u><b>r10</b></u> , r28   | the execution of the special instruction Id (<1>) is com-                                                                                                                                |

|           | <3>   | sld.w    | 0x28, r10                 | plete.                                                                                                                                                                                   |

| Ex        | amp   | le 2:    |                           |                                                                                                                                                                                          |

|           | <1>   | ld.w     | [r11], <u>r10</u><br>:    | This situation occurs when the decode operation of <b>cmp</b> (<2>) immediately before the <b>sld</b> instruction (<3>) and interrupt request servicing conflict before execution of the |

|           | <2>   | cmp      | imm5, <u><b>r10</b></u>   | special instruction $Id$ (<1>) is complete. As a result, the                                                                                                                             |

|           | <3>   | sld.w    | 0x28, r10                 | compare result of the <b>cmp</b> instruction becomes undefined, which may cause an unexpected operation of the branch                                                                    |

|           | <4>   | bz lat   | bel                       | instruction <b>bz</b> (<4>).                                                                                                                                                             |

| Ex        | amp   | le 3:    |                           |                                                                                                                                                                                          |

|           | <1>   | ld.w     | [r11], <b>r10</b><br>:    | This situation occurs when the decode operation of the <b>add</b> instruction (<2>) immediately before the <b>sld</b> instruction (<3>) and interrupt request servicing conflict before  |

|           | <2>   | add      | imm5, <u><b>r10</b></u>   | execution of the special instruction Id (<1>) is complete.                                                                                                                               |

|           |       |          | 0x28, r10                 | As a result, the result of the <b>add</b> instruction and the depending status flags become undefined, which may                                                                         |

|           | <4>   | setf     | c, r16                    | cause an unexpected operation of the <b>setf</b> instruction (<4>).                                                                                                                      |

| Wa        | orkar | round    |                           |                                                                                                                                                                                          |

| (1)       | Do    | not use  | e the <b>sld</b> instruct | ion (e. g. by avoiding code optimization that makes use of <b>sld</b> ).                                                                                                                 |

| • •       |       |          | •                         | cribed above is used (a <b>sld</b> instruction following an instruction than a sert a <b>nop</b> instruction before the <b>sld</b> instruction.                                          |

| cai       | n be  | execu    | •                         | cribed above is used (a <b>sld</b> instruction following an instruction that<br>exchange the order of the previous two instructions as long as the                                       |

|   | SLD instruction precaution (Specification change notice)<br>(Specification change notice)  |

|---|--------------------------------------------------------------------------------------------|

| ( | (cont.)                                                                                    |

|   | Example:<br>1. (before implementing workaround)<br>ld.w [r11], r10                         |

| 1 | <br>add r11, r12<br>mov r10, r28<br>sld.w 0x28, r10                                        |

| 1 | 2. (after implementing workaround)<br>ld.w [r11], r10                                      |

| l | <br>mov r10, r28<br>add r11, r12<br>sld.w 0x28, r10                                        |

|   | (4) When assembler code is used:<br>Avoid the crictical code sequences as described above. |

| No. 14 | aFCAN transmission / reception<br>(Technical limitation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <u>Details</u><br>The aFCAN macro will under certain timing conditions accompanied by a particular configuration<br>of the message buffers and a specific operational usage not operate as expected. Different<br>behaviors have to be considered. The description of the particular unexpected behavior is organ-<br>ized by the buffer Type: TX and RX, the frame format (extended or standard identifier), and the<br>buffer number.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | <b>TX-Buffer Behavior</b><br>This section describes all unexpected behaviors linked to the configuration of transmit buffers.<br>Configurations not listed are of no concern and can be used without restrictions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|        | - Buffer #0 or Buffer #0 and #1 are configured as TX-buffer<br>When using message buffer #0 as a TX-buffer, the message requested for transmission of this<br>buffer may not be sent at the next possible timing. This behavior is caused when the internal scan<br>for new transmission requests reached buffer #0 and at the same time the transmission of a previ-<br>ously sent message ends. Instead of sending the message object from buffer #0, the aFCAN<br>attempts to send the contents of message buffer #1. In case the TRQ of buffer #1 is set, the mes-<br>sage from buffer #1 is sent followed by the transmission of the message in buffer #0. This resem-<br>bles an inner priority inversion. In case the TRQ of buffer #1 is not set or buffer #1 is not a TX-<br>buffer, the contents of buffer #0 are sent whenever any of the other TRQ-bits in the aFCAN are set<br>or cleared, or when a receive operation is started; i.e. when the next bus activity occurs. This<br>behavior is valid for both frame types, extended or standard identifier format.                                                                                                                                                                                                                                                                                                                                                           |

|        | - Buffer #1 - #31 are configured as TX-buffer<br>There are two configurations that lead to the same, unexpected behavior. In the first configuration<br>Buffer #1 through #31 are set up as normal TX-buffers, and in the second configuration buffer #0<br>through #7 are operated in ABT-mode (automatic block transmission) and the remaining buffers<br>(#8 - 31) are configured as normal TX-buffers. The unexpected behavior occurs as well if only a<br>subset of buffers are configured as normal TX-buffers. When using any message buffer #n in the<br>range of buffer #1 through #31 with extended identifier, an inner priority inversion can be encoun-<br>tered. In that case the message from buffer #n+1 is sent in advance of the message in buffer #n<br>even though the priority of the identifier in buffer #n is higher. This behavior is seen when the<br>internal transmit search algorithms of the aFCAN processing buffer #n meets the start of a trans-<br>mission, the end of a frame on the bus (RX or TX) that needs to end with an error frame, or the<br>event of transmission request by the CPU or by the ABTmode. In case the ABT-mode is active,<br>the unexpected behavior does only apply for messages in buffer #8 through #31. This behavior<br>applies only if extended identifiers are in use. Applications exclusively using standard Identifiers<br>do not suffer any limitation of this kind. |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| aFCAN transmission / reception (contd.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|